分离栅式快闪存储器抗编程干扰性能的工艺优化

周儒领,张庆勇

(中芯国际集成电路制造(上海)有限公司,上海201203)

分离栅式快闪存储器抗编程干扰性能的工艺优化

周儒领,张庆勇

(中芯国际集成电路制造(上海)有限公司,上海201203)

随着电子产品的普及,分离栅式快闪存储器作为闪存的一种,因其具有高效的编程速度以及能够完全避免过擦除的能力,无论是在单体还是嵌入式产品方面都得到了人们更多的关注。但由于快闪存储器产品规则的阵列排列方式,高速的编程能力也带来了容易出现编程干扰的问题,成为了制约其实际应用的关键因素。从工艺优化方面探讨在编程过程中,如何有效提高分离栅式快闪存储器的抗编程干扰性能。通过实验发现通过整合改进工艺流程中调节字线阈值电压的离子注入方式的方法,可以显著改进分离栅式工艺快闪存储器的抗编程干扰性能。

分离栅式快闪存储器;抗编程干扰;行干扰;列干扰;对角线干扰

1 引言

分离栅式存储器结构单元如图1和图2所示,其使用了3层多晶硅工艺来分别形成浮栅(Floating Gate,FG)、控制栅(Control Gate,CG)和字线(Word Line,WL)/擦除栅(Erase Gate,EG),并在结构上分离出了专用的控制栅和擦除栅[1]。

如图2所示,在对选中的分离栅式快闪存储器存储单元进行编程操作时,电子通过开启的沟道采用SSI(Source Side Injection,源端热电子注入)机制注入到浮栅中[2]。当进行擦除操作时,浮栅中的电子通过EG-FG多晶硅到多晶硅FN隧穿效应被拉出到EG中去[1]。由于在有电子存在和没有电子存在的情况下,浮栅的电势不同,相同的读取电压下浮栅下方沟道关闭或者开启状态也不同,可以据此对应所读取的源漏间沟道电流的不同大小来判断该存储单元浮栅中有无电子存在,进而得到存储单元的存储信息是0(编程状态)或者1(擦除状态)。相比较传统的堆叠栅式快闪存储器所采用的沟道热电子注入机制,源端热电子注入的编程电流更小,编程功耗更低,编程效率更高[3]。

图1 分离栅式快闪存储器的结构单元

图2 分离栅式快闪存储器的编程操作示意图

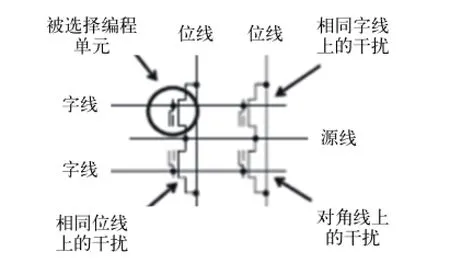

由于快闪存储器产品普遍采用规则的阵列方式排列,在高效编程的过程中,如何克服编程干扰成了不可忽视的问题。所谓编程干扰,是指受被编程存储单元在正常编程过程中的影响,本来没有被选中的存储单元发生的一种导致存储信息改变的错误。通常按照被编程存储单元与受影响存储单元之间的相对关系,编程干扰模式大致可分为3种类型:相同字线上的干扰(Row Disturb)、相同位线上的干扰(Column Disturb)以及对角线上(字线和位线都不同)的干扰(Diagonal Disturb),如图3所示[4]。

图3 快闪存储器的3种不同编程干扰类型

在编程单元被编程时,由于处于规则阵列不同位置上被干扰的存储单元所承受的干扰电压以及干扰时间的不同(如表1所示),因此表现出来的受干扰程度也不尽相同。由于所承受的干扰时间最长,对角线上的干扰(Diagonal Disturb)一般表现最严重。

以擦除状态为背景,我们用受编程干扰前后存储单元的读取电流的变化率作为指标来衡量存储单元的抗编程干扰性能,表征为读取电流的变化率越小,则抗编程干扰性能越强。同时我们也考虑了不同测试温度对编程效率的影响[5],设定的工艺目标为不论是常温还是高温测试条件下,被编程干扰存储单元读取电流的变化率均不超过5%。

表1 3种不同编程干扰类型所承受的不同干扰条件

2 实验内容

在工艺优化之前,分离栅式快闪存储器存在着编程干扰偏大的问题,3种不同类型的编程干扰下所测试的存储单元的读取电流变化率如表2所示。

从表2中可以发现,对角线上的干扰(Diagonal Disturb)在高温(95 ℃)下的抗编程干扰能力最差,部分测试单元读取的电流变化率已经超过5%的设定最大目标。

通过进一步分析其与其他电学测试结果,发现对角线上的干扰(Diagonal Disturb)与字线的阈值电压(Vt-WL)存在着一定的关联性。如图4所示,字线的阈值电压越高,对角线上的干扰就表现得越严重。字线的阈值电压在现有工艺上主要由离子注入工艺(CVT IMP)的注入浓度来调节。

因此,如何在保证字线的阈值电压不受影响的前提下,尽可能去降低调节字线阈值电压的离子注入工艺(CVT IMP)的注入浓度,成为提高存储单元抗编程干扰性能的关键所在。

于是我们整合改进了工艺流程中调节字线阈值电压的离子注入的方式方法,在字线定义后的轻掺杂(Light Dosage Doping,LDD)工艺中增加一步倾斜30°的抗沟道导通(APT IMP,Anti-Punch Through)离子注入,与原本在字线定义前的CVT IMP叠加在一起来调节字线的阈值电压。

图4 对角线上的干扰与Vt-WL的对应关系

表2 工艺优化之前分离栅式快闪存储器存在的编程干扰问题

通过以上改变,即可通过降低CVT IMP注入浓度来达到提高存储单元抗编程干扰性能的目的。虽然降低CVT IMP的注入浓度会引起字线阈值电压的降低,但是倾斜角度的轻掺杂(LDD)可以被用来在后续工艺中进行相应补偿,以保证字线的阈值电压保持在相当水平。

根据以上分析,我们设计的相关实验条件如表3。

3 实验结果

不同实验条件下所测试的存储单元的读取电流变化率见表4。

表3 提高存储单元抗编程干扰能力的实验条件

表4 不同实验条件下的编程干扰测试结果

从测试结果可以看出,在字线阈值电压保持在0.45 V目标左右时,实验条件5有着最小的编程干扰指标,同时仍保持着较高的擦除电流。

我们进一步选择实验条件5进行重复实验,并分别在常温下和高温下测试其编程干扰性能,结果已经达到了读取电流的变化率均不超过5%的工艺目标,如表5所示。对于这一提高抗编程干扰能力的工艺优化,我们对存储单元的编程效率也进行了专门的测试,用到达一定目标电流时所需的时间(T2P, time to program)作为指标来衡量,表征为T2P的时间越短,则编程效率越高。如图5所示,实验条件5下的存储单元依然保持着高效的编写性能,1 μs时间内就可以将沟道电流拉低到目标值,完全满足一般为10 μs的电路设计规格。

从理论上分析,由于在源极p-n结处于反向偏置状态,实验条件5在不牺牲字线阈值电压的情况下,减少CVT IMP离子注入浓度,从而有效减小了字线与浮栅间相邻区域即热电子被注入浮栅的主要区域衬底的掺杂浓度。这就避免了在横向的强电场作用下在该区域发生带带隧穿效应(即价带中的电子能够穿越禁带势垒隧穿到导带中),否则产生的大量热电子很容易在垂直方向的强电场作用下进入浮栅从而导致没有被选中的存储单元也容易被编程,即发生所谓的编程干扰。

分离栅结构中沟道电子密度分布及横向电场分布的二维仿真示意图[4]显示了分离栅式快闪存储器结构的沟道电子密度分布,以及沿沟道方向的横向电场的分布情况,可以发现横向电场最强的区域正是字线与浮栅间相邻区域即热电子被注入浮栅的主要区域,这也进一步佐证了本文的理论分析。

图5 存储单元在split5工艺条件下的T2P表征

表5 实验条件5的重复实验结果

4 结论

本文通过分析发现在分离栅式快闪存储器编程过程中,对角线上的编程干扰(Diagonal Disturb)与字线的阈值电压存在着较强的正比关系。由此我们整合改进了工艺流程中调节字线阈值电压的离子注入方式的方法,在字线定义后的轻掺杂工艺中增加一步倾斜30°的抗沟道导通离子注入,与原本在字线定义前的CVT IMP叠加在一起来调节字线的阈值电压。这样,就可以通过降低CVT IMP注入浓度,避免了字线与浮栅间相邻区域发生带带隧穿效应而使热电子进入浮栅,来达到提高存储单元抗编程干扰性能的目的。同时字线的阈值电压和存储单元的编程效率也不会受到影响。

致谢

感谢中芯国际集成电路制造(上海)有限公司技术研究发展中心同仁以及SST公司合作伙伴在技术和数据收集上的帮助。

[2] Guan H, Lee D, Li G P. An analytical model for optimization of programming efficiency and uniformity of split gate source-side injection SuperFlash memory [J]. Electron Devices, IEEE Transactions, 2003, 50(3):809-815.

[3] Tkachev Y, Xian Liu, Kotov A. Floating-Gate Corner-Enhanced Poly-to-Poly Tunneling in Split-Gate Flash Memory Cells [J]. Electron Devices, IEEE Transactions, 2012, 59(1):5-11.

[4] Markov V, Korablev K, Kotov A, Liu X, Jia Y B, Dang T N, Levi A. Charge-gain program disturb mechanism in split-gate flash memory cell [A]. Integrated Reliability Workshop Final Report, IEEE International, 2007. 43-47.

[5] Lee W H, Chan-Kwang Park, Kim Kinam. Temperature Dependence of Endurance Characteristics in NOR Flash Memory Cells [A]. Reliability Physics Symposium Proceedings,44th Annual., IEEE International, 2006. 701-702.

[1] Caleb Yu-Sheng Cho, Ming-Jer Chen, Chiou-Feng Chen, Tuntasood P, Fan D T, Tseng-Yi Liu. A novel self-aligned highly reliable sidewall split-gate flash memory [J]. Electron Devices, IEEE Transactions, 2006, 53(3):465-473.

Process Optimization to Improve Anti-program Disturb Performance in Split-gate Flash

ZHOU Ruling, ZHANG Qingyong

(Semiconductor Manufacturing International(Shanghai)Corp., Shanghai 201203, China)

As of the popularity of various electronic products, the split-gate flash, one kind of the flash memories, due to its highly efficient programming speed and the ability to completely avoid over-erase issue, got more and more attention both in stand-alone and embedded applications. But with highly efficient programming speed in the regular cell array, the program disturb has been the bottleneck of the application of such split-gate flash. The paper studied on how to improve anti-program performance through process optimization. With the optimized integration scheme on the threshold voltage adjustment implantation of word line, the anti-program disturb performance of such kind of split-gate flash can be greatly improved.

split-gate flash; anti-program disturb; row disturb; column disturb; diagonal disturb

TN305

A

1681-1070(2015)07-0033-04

周儒领(1976—),男,安徽安庆人,2001年毕业于南京大学,硕士学历,目前在中芯国际集成电路制造(上海)有限公司技术研究发展中心主要从事闪存存储器方面的研究和开发工作。

2015-04-08