一种Divided RESURF高压互连结构研究

张 昕,乔 明

(电子科技大学电子薄膜与集成器件国家重点实验室,成都 610054)

一种Divided RESURF高压互连结构研究

张 昕,乔 明

(电子科技大学电子薄膜与集成器件国家重点实验室,成都 610054)

高压互连是功率集成电路中的重要技术,随着PIC在结构功能上的发展和应用范围上的增大,人们对功率集成电路中的高压互连技术的要求也与日俱增。围绕高压互连技术进行研究,使用Divided RESURF技术设计一种横向双扩散金属氧化物半导体场效应晶体管,通过进行二维仿真,优化其结构和掺杂浓度等参数,器件的击穿耐压达到903 V,可用于600 V高压集成电路中。

高压互连线;击穿耐压;Divided RESURF

1 引言

高 压互 连 线(High voltage Inter-connection,HVI)把电流信号在同一颗芯片上的高压端与低压端之间进行传递。该种结构中的互连线金属的高电势会影响其下方器件的电场分布,导致局部出现极高的电场峰值,这会使横向双扩散金属氧化物半导体场效应晶体管(Lateral Double Diffused MOSFET,LDMOS)的击穿电压出现显著的降低。在反向偏置时,HVI相对于器件表面带正电荷,从而引入了额外的纵向电场,这可能导致器件的提前击穿,还可能会造成严重的热载流子注入问题。

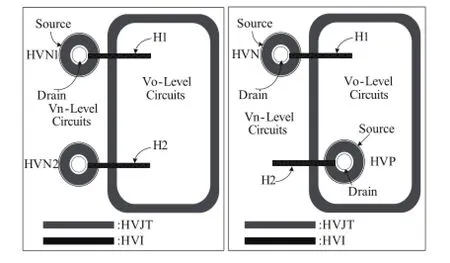

HVI问题在超过600 V的高压集成电路中比较常见,但该现象在200 V左右的较低电压集成电路,甚至低于100 V的电路中也会存在。传统的具有高压互连的高压驱动电路结构如图1所示。图1中H1、H2连接了LDMOS的高压漏端,如果这两条金属线没有被有效地屏蔽,互连线的高电势会严重影响底部高压结终端的电场分布。对一个原本满足RESURF条件的结构来说,HVI引入的电荷会导致严重的电荷失衡。由于互连线相对于器件带正电,中性区中的电子会被吸引到器件表面,从而导致耗尽区的收缩,令栅场板底端的电场峰值剧烈上升,使器件的击穿电压远低于无HVI时的最优耐压。

传统工艺中可以通过提高表面绝缘层厚度,即提高HVI与半导体表面之间的距离来进行屏蔽[1],但这种方法对表面氧化层厚度有较大的限制,并不适用于600 V及以上的高压互连应用中。结终端扩展结构[2](Junction Termination Extension,JTE)及线性变掺杂(Linearly Varying Doped,LVD)的双重表面场降低技术double RESURF[3](Reduced SURface Field)也被广泛应用于高压互连结构中。此外,场板技术也是用来降低HVI对高压器件击穿特性影响的常见选择,包括偏置多晶场板[4]、卷形阻性场板[5]、单层多浮空场板[6]、双层多浮空场板[7]等结构。

本文研究了一种Divided RESURF高压互连结构,分析了其屏蔽HVI的原理和优势,并通过仿真对器件的耐压等特性进行了验证,达到600 V的互连要求。该技术不需要额外的互连屏蔽结构,其击穿特性仅取决于器件PN结的耐压。

图1 传统高压驱动电路结构

2 Divided RESURF高压互连结构

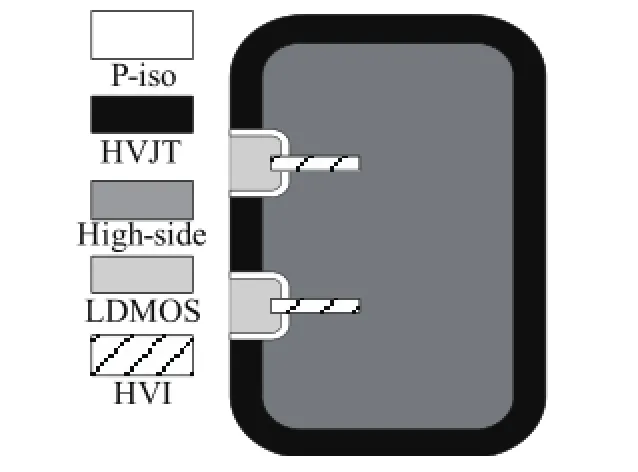

如图2所示,Divided RESURF高压集成电路结构中,高压互连线为内互连,没有跨过器件漂移区和高压结终端,从根本上避免了高压互连线带来的有害影响。高压互连线从LDMOS的漏极连接到高压控制电路中,互连线金属仅跨过了P型隔离区(P-iso)(或P型衬底),当P型隔离区完全耗尽时,LDMOS的耐压不会受到互连线电位的任何影响,从而不需要任何场板结构或降场层结构来屏蔽。

图3给出了Divided RESURF高压互连结构的LDMOS剖面图。在LDMOS和高端控制部分之间增加了由高压P阱(HVP)和P型埋层(Pbl)形成的P型隔离区。在工艺上,P型埋层可通过外延前注入形成,高压P阱可通过多次杂质注入后,再根据外延厚度进行适当的热过程,使高压P阱与P型埋层分别进行纵向上的扩散直到连接到一起,形成P型隔离区。利用P型隔离区和N型外延层的反向偏置,消除了LDMOS与高压控制电路外延之间的漏电流通路。通过在高压电路区域增加N型埋层(Nbl)提高高压控制电路区域的穿通击穿电压,增强该区域内的dV/dt能力,并可以在一定程度上调节LDMOS的电荷平衡。

图2 Divided RESURF高压互连结构俯视图

图3 Divided RESURF高压互连结构示意图

3 仿真分析

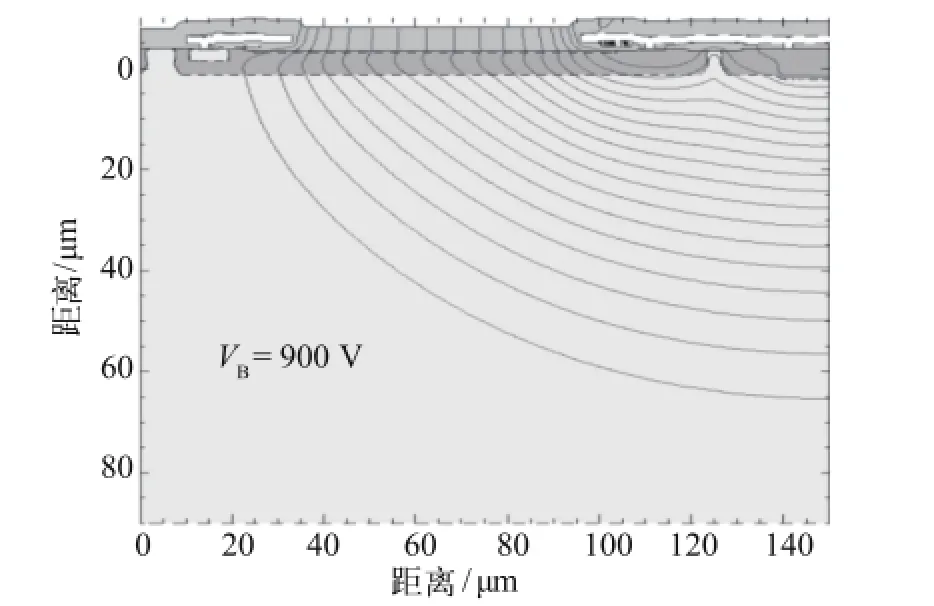

作者应用二维器件仿真软件对器件进行了仿真。图4给出了Divided RESURF LDMOS耐压900 V时的电势分布。电势线分布较均匀,相邻两条等势线间的电势差为50 V,器件击穿电压二维仿真值为903 V。此时,器件耐压903 V时的最大电场出现在体内漏端下的P型衬底和N型外延的冶金结处,属体内纵向击穿。器件表面电场较平坦,漂移区全部耗尽。高压互连线的高电位对器件的击穿耐压没有任何影响。

LDMOS的外延与top层浓度与击穿电压的关系如图5所示。仿真条件如下:漂移区长度为70 μm,场氧化层厚度D=0.8 μm,外延层厚度为6 μm,P型top层厚度1 μm,P型衬底的掺杂浓度为2×1014cm-3。首先可以看出,N外延层浓度较高或较低时器件的击穿电压相比最优值都有所下降,而N外延层浓度很高时器件的耐压下降极为严重。只有当N外延层和P-top浓度同时满足RESURF原理,都在RESURF优化区的情况下才可在较大的范围内获得高的击穿电压。

其次随着N外延层浓度的增加,满足RESURF原理的P-top浓度的范围将逐渐减小。当外延层浓度为3.8×1015cm-3时,使器件能获得600 V以上耐压的P-top层浓度范围已经有所减小。分析上述仿真结果,当LDMOS漏端加高压时,全部耗尽的漂移区和P-top用于承受电压。P-top层靠近源端一侧的P/Nepi结电场与主结Nepi/Pwell结的电场相反,可有效降低主结尖峰电场。若其浓度过低时,P-top层对主结尖峰电场削弱作用不强,使器件过早在该处击穿。反之若其浓度过高则P-top层漏端尖峰电场首先达到Si临界电场Ec,又使器件过早在此处击穿。

图4 Divided RESURF结构仿真图

图5 不同漂移区浓度下耐压与top层掺杂的关系

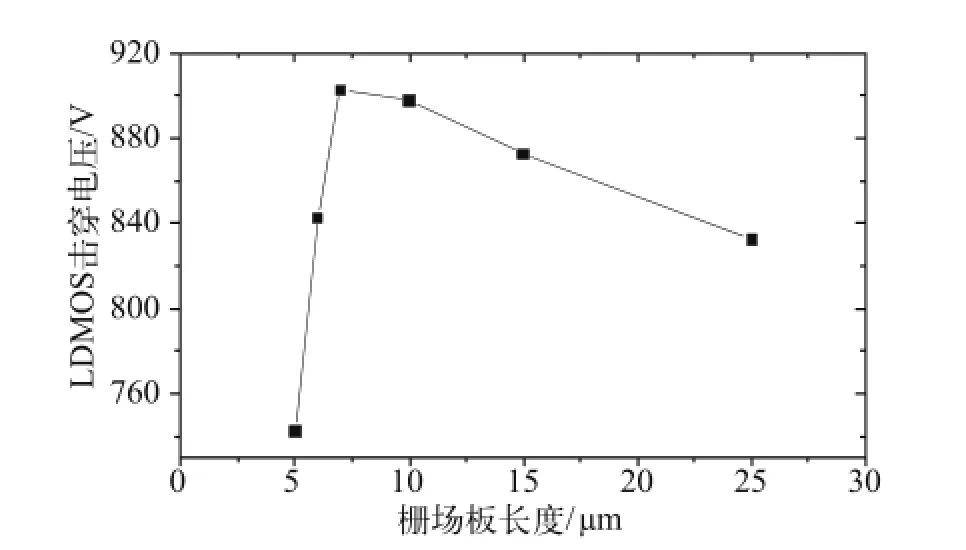

在LDMOS中,场板起到了平衡表面电场的作用。然而在仿真中发现,器件的耐压与栅极场板的长度(图3中标注为L)之间并非完全的正相关关系,如图6所示。当栅极场板长度超过最优值时,器件的耐压反而会随着场板长度的增加有明显下降。出现上述耐压变化的原因在于,当器件的栅极场板长度较小,不能达到降低表面场峰值的最佳值时,随着场板长度的增加,对器件表面电场的优化作用也增大。当场板的长度已经达到降低表面电场峰值的足够长度后,场板长度的继续增大会减小漂移区的长度,而优化表面电场分布的作用已经不太明显。因此器件的耐压随着栅极场板长度的增加出现先增大后减小的变化规律,对于此章中提出的器件结构,场板的最佳长度是7 μm。

图6 器件耐压与栅场板长度的关系

图7为Divided RESURF结构中的P型隔离区域仿真示意图。在该结构中,LDMOS的外延层与漏区相连,高端电路区域的外延层与高端电路的电源电位相连。当连接到LDMOS栅极的低端电路输出信号使LDMOS开启时,LDMOS的漏区电位将低于高端电路区域的电源电位。在Divided RESURF结构中,外延层之间具有P型隔离区,防止LDMOS与高端电路区域之间出现漏电。在此结构中,漏端电压VD与高压电路区域的输入端VO之间的P型隔离区域的穿通击穿耐压是该结构中的关键参数。

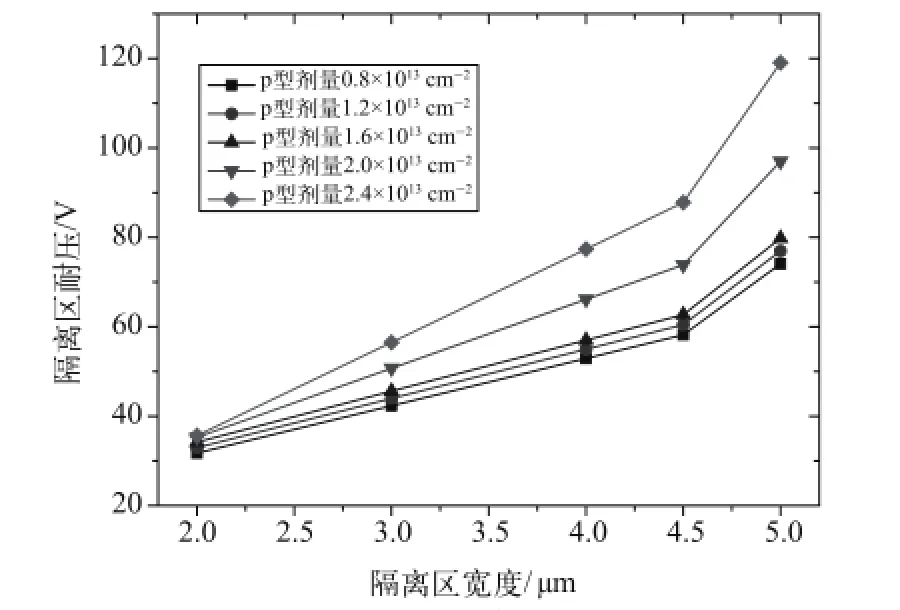

图7 P型隔离区域仿真

使用器件仿真软件进行仿真,令LDMOS的漏极电位为0,Vo的电位从0逐渐增加,研究该结构的穿通击穿耐压。两电极之间的穿通击穿耐压与P型区域宽度、注入剂量的关系如图8所示。经过仿真,隔离区的穿通耐压随着隔离区宽度和注入剂量的增加而增大。在普通电平位移电路中,两电极之间的电压差的值在0~30 V之间,而当两个区域的外延层之间的宽度为3 μm时,穿通耐压可以达到40 V,充分满足实际应用的要求。

由于高压电路区域中的N型埋层具有较高的电位,其与LDMOS的漏极的距离(图3中标注为D)也对该穿通耐压有较大的影响。仿真结果如图9所示,当N型埋层距离P型隔离区较近时,穿通击穿耐压会下降到70 V以下。随着N埋层与隔离区的距离增大,该耐压也随之增大,但同时LDMOS的耐压却随之有所降低,因此对于将该宽度取15~20 µm即可同时保证隔离区耐压与LDMOS的耐压满足应用的需求。这可以作为实际电路设计时对高压电路内部结构布局的参考因素。

图8 隔离耐压与隔离区宽度/剂量的关系

图9 穿通击穿耐压与N型埋层位置的关系

4 结束语

本文对比总结了常用高压互连结构的应用领域及各自局限,并研究了一种Divided RESURF高压互连结构。用仿真软件对提出的Divided RESURF技术进行了工艺仿真,总结出各参数对器件耐压与隔离区穿通击穿耐压的影响。最终器件仿真耐压为903 V,可用于600 V高压集成电路中。

[1] Sakurai N, Nemoto M, Arakawa H, Sugawara Y. A threephase inverter IC for AC 220 V with a drastically small chip size and highly intelligent functions [A]. In: ISPSD symp, 1993. 310-315.

[2] Falck E, Gerlach W, Korec J. Influence of interconnections onto the breakdown voltage of planar high-voltage p-n junctions [J]. IEEE Trans Electron Dev, 1993, 40(2): 439-447.

[3] Souza MMD, Narayanan EMS. Double resurf technology for HVICs [J]. Electron Lett 1990, 32(12).

[4] Murray AFJ, Lane WA. 800 V wiring for HVIC application using biased poly-silicon field plates [J]. Microelectron J, 1996, 27: 209-215.

[5] Endo K, Baba Y, Udo Y, Yasui M, Sano Y. A 500 V 1 A 1-chip inverter IC with a new electric field reduction structure [A]. In ISPSD symp, 1994. 379-383.

[6] Qiao M, Li ZJ, Zhang B, Fang J, Li M. Realization of over 650 V double RESURF LDMOS with HVI for high side gate drive IC [A]. In Proceeding of ICSICT, 2006. 248-250.

[7] Terashina T, Yoshizawa M, Fukunaga M, Majumdar G. Structure of 600 V IC and a new voltage sensing device [A]. In ISPSD, 1993. 224-229.

作者简介:

只生武(1992—),男,甘肃金昌人,本科,主要研究方向为电源管理、音频功放、信号处理等。

Research of Divided RESURF HVI Structure

ZHANG Xin, QIAO Ming

(State Key Laboratory of Electronic Thin Films and Integrated Device, University of Electronic Science and Technology of China, Chengdu 610054, China)

High Voltage Interconnection is a key technology of Power Integrated Circuit. With the rapid rise of structures, functions and applying range of PIC comes a rapid rise of influence causing by HVI. Thus, the traditional HVI structure can no longer meet the modern requirement in this field. This dissertation focuses on the HVI technology and proposes a divided RESURF LDMOS, using two-dimension device simulation to complete a requirement of 600 V interconnection with optimization of its structure and concentration. The structure can be used in the power integrated circuit of 600 V application.

high voltage interconnection; breakdown voltage; divided RESURF

TN402

A

1681-1070(2015)07-0024-04

张 昕(1989—),男,山东兖州人,硕士研究生,主要研究方向为功率器件与工艺设计。

2015-04-08