D类功放输出功率调节电路设计

只生武

(无锡晶源微电子有限公司,江苏 无锡 214028)

D类功放输出功率调节电路设计

只生武

(无锡晶源微电子有限公司,江苏 无锡 214028)

D类音频功放具有高效率的优点,但是随着功率的不断提高,通常需要完善的保护及限制电路。设计介绍了一种用于高功率D类音频功率放大器的输出功率调节电路,可以通过芯片外部引脚输入电压或编程的方式动态调节功放的输出功率。控制方式采用了限制输入信号最大幅度的方法,分别介绍了电路的控制原理与电路实现。测试结果显示,该电路达到了较好的调节效果,具有好的调节线性度,提高了高功率放大器电路的可靠性。

D类功放;功率调节;幅度限制

1 引言

D类音频功放具有效率高、轻便等优点,逐渐成为功率放大器的发展趋势,尤其是在大功率应用场合。近年来,随着调制技术与集成电路技术的迅速发展,D类功放的保真度逐年提高,设计与成本已经不再成为限制D类功放发展的因素,并且D类功放与数字音响可以很好地相通。在提倡节能环保的大背景下,D类功放技术必然成为主流。然而随着功率的增大,对D类功放电路及其系统的保护就显得尤为重要。

2 D类音频功放原理

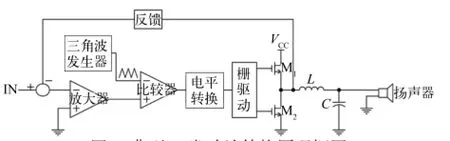

典型的D类音频功放信号流如图1所示。图1中由输入差分放大级、斜波发生器、PWM比较器、功率输出级及滤波电路组成。其中,斜波发生器产生远高于输入信号频率的三角波,输入差分放大级将音频小信号差分放大,使其信号的幅度与斜波发生器产生的三角波幅度相当。然后PWM比较器将放大后的输入音频信号与三角波进行比较,将音频信号的幅度转变为PWM信号的占空比,输出PWM信号。

图1 典型D类功放结构原理框图

其调制原理如图2所示。当三角波幅度大于信号幅度时,PWM比较器输出为低电平。而当三角波幅度小于信号幅度时,PWM比较器输出为高电平。那么,由于三角波的幅度与频率是固定不变的,当信号幅度发生变化时,输出PWM信号的占空比就会随着信号的幅度发生相应变化。经过这一调制过程,就将信号的幅度参数映射到了PWM信号的占空比上。为了最大限度地提高效率,减少内部电路的功率损耗,PWM比较器通常在低压下工作,而输出功率级为了实现高功率,通常工作在高压下,所以中间必须有电平转换电路。经电平转换后的PWM信号由栅驱动电路增强后驱动大功率MOSFET工作,输出高压大电流的PWM信号,最大输出功率通常与功率输出级的MOS管能力相关。

图2 调制原理示意图

最后通过低通滤波器将PWM信号滤波后还原为原始的输入信号,即将PWM的占空比再次恢复为信号的幅度参数。经过这一过程实现了信号的放大。在该转换过程中,大功率MOSFET工作于开关状态,自身损耗较小,因此可以实现高效率。

3 输出功率限制电路设计

由于D类功放的高效率,D类功放的功率可以做得很大而不必担心散热问题。但是过大的功率会造成扬声器的损坏。为了适应不同的功率需求,在D类功放中加入功率调节单元是一个很好的选择。这样不仅增加了整个系统的可靠性,并且实现了功放的智能化。

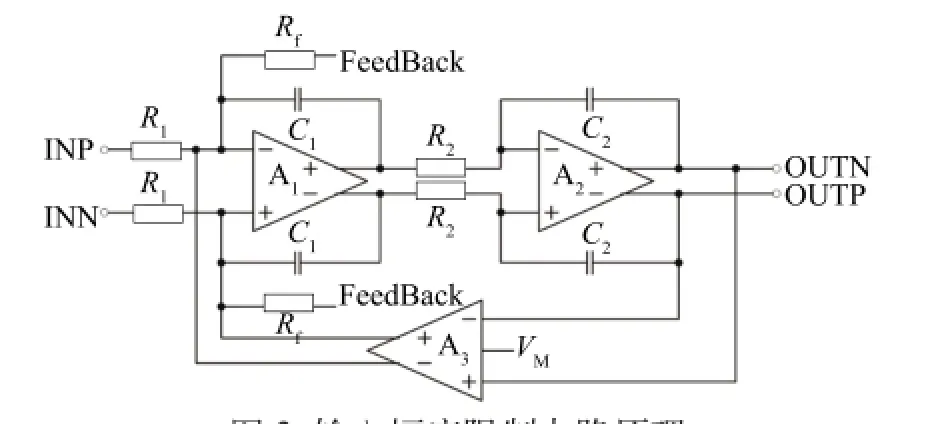

在不改变功放增益的前提下,一种最实用的方式是动态调节输入信号的最大限制幅度。下面介绍一种在D类音频功率放大器前置差分放大电路中限制信号幅度的方法,其实现原理如图3所示。

图3 输入幅度限制电路原理

实际上,该电路输入差分放大由运放A1与A2构成的两级低通滤波器组成。INP与INN为幅度相同但相位相反的差分输入信号,OUTP与OUTN为放大后的差分信号,Rf为反馈电阻,A3是实现功率调节所需的放大器,该放大器的输入信号为滤波器信号输出OUTP与OUTN,A3的输出控制A1的输入信号,以此来实现闭环调节功能。信号的相位关系见图3。当OUTP或OUTN其中一个的信号幅度小于VM时,表明信号太大,输出功率超过了限制的功率,则此时运放A3相应的输出翻转,将A1的输入信号进行限制,使OUTP或OUTN产生削波,限制其幅度。但是当输入信号幅度在正常功率范围内时,A1的输入信号应不受A3的影响,需要将A3的输出与电路断开。而要想实现不同的输出功率,只需通过外部引脚或者编程的方式来控制VM电压的大小就可以了。

经过以上分析,所设计的放大器A3具体实现电路如图4所示。其中,由M2与M3构成源极输入差分对,R1与C1构成低通滤波,使栅极电位稳定。静态时,M2与M3栅极电位为:

设计M10、M15、M16具有相同的宽长比,则稳态时流过M1、M2、M3的电流相等,若M1~M3也具有相同的宽长比,则可以得到:

那么M2、M3的栅极电位又可表示为:

只要IN-或IN+的幅度小于VM,M2或M3管就会导通,使运放输出翻转。由于IN+与IN-为幅度相同但相位相反的差分信号,当IN+低于VM时,IN-必定高于VM,则M2导通,M3截止,使得M7、M8截止,M4、M9相应导通,而使M4下拉OUT+,M9上拉OUT-。同样,当IN-低于VM时,IN+必定高于VM,使得M7下拉OUT-,M8上拉OUT+,而当IN+与IN-均大于VM时,M1、M10与M7、M9均截止,OUT-与OUT+输出为高阻态,使其不会影响到正常工作。当运放工作时,将会限制对应的输入信号,使信号发生削波,限制信号幅度。实际应用中为了获得较大的跨导,通常会将M1、M2、M3的宽长比设置得较大。

图4 放大器A3实现电路图

4 测试结果

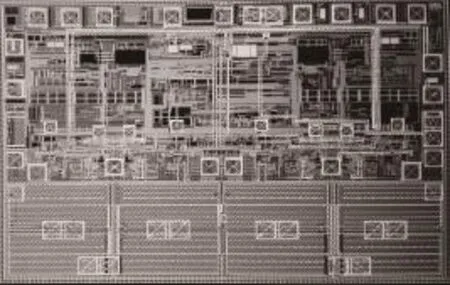

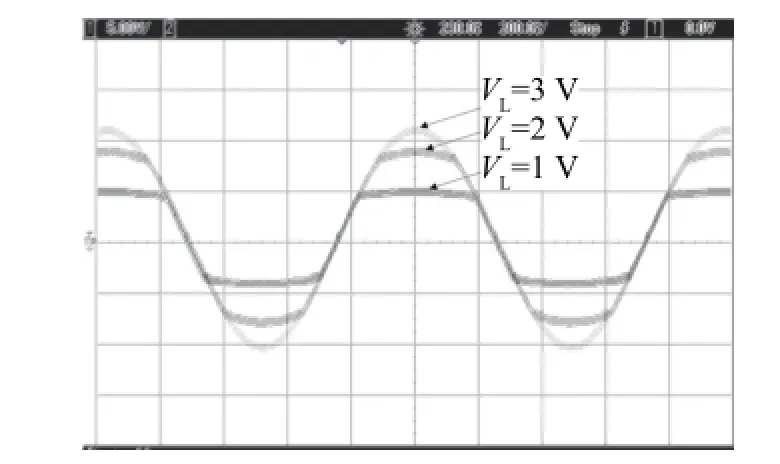

将该功率限制模块加入D类功放后进行了流片,图5为芯片整体版图。对成品进行了整机测试,图6显示了不同电源电压、不同增益下输出功率随外部调节电压的变化曲线。由测试结果可以看出,在不同的增益下,当达到限制点时,输出功率随调节电压的变化而变化,并且输出功率的大小与调节电压之间具有良好的线性度。当调节电压高于限制点时,调节电压的改变几乎不会影响到电路的输出功率,实现了良好的调节效果,在较高电源电压(18 V)的情况下,依然具有较好的调节性能。图7为VCC=12 V、8 Ω负载,调节电压分别为1 V、2 V、3 V时输出信号的波形。可以看出,随着调节电压的减小,输出信号的削波程度也相应增大,实现了输出功率的限制功能。

图5 实现的D类功放整体版图

5 结论

利用调节输入信号最大幅度的方式,设计了一种用于D类音频功率放大器的输出功率调节电路,对设计方案及电路实现进行了详细的介绍,整机应用时的测试结果显示电路实现了良好的调节效果与线性度,提高了大功率D类功放的可靠性与智能化。

图6 输出功率随调节电压的变化曲线

图7 VCC=12 V,8 Ω负载时不同调节电压下输出信号波形

[1] Behzad R. Design of Analog CMOS Integrated Circuits [M]. McGRAW-HALL INTERNATIONAL EDITION, 2001.

[2] Phillip E A, Douglas R H. CMOS 模拟集成电路设计[M].北京:电子工业出版社,2005.

[3] Willy M C S. 模拟集成电路设计精粹[M]. 北京:清华大学出版社,2008.

[4] 童诗白. 模拟电子技术基础[M]. 北京:高等教育出版社,2010.

[5] 方明. 基于D类功放的音频放大器设计[D]. 华南理工大学硕士论文,2010.

[6] 薛超耀. 增益可调的免滤波D类音频功放芯片的设计[D]. 西安电子科技大学硕士论文,2013.

[7] 赛尔吉欧.佛朗哥. 基于运算放大器和模拟集成电路的电路设计第三版[M]. 西安:西安交通大学出版社,2004.

Design of Class D Power Amplifier with Output Power Adjustment

ZHI Shengwu

(Wuxi Crystal Electronics Co. Ltd., Wuxi 214028, China)

Because the class D audio power amplifier has the advantages of high efficiency, has become the trend of the development of high-power audio amplifier, but with the constant improvement of the power, the reliability of the system is particularly important, often need to perfect protection and limiting circuit. The paper introduces a design for high power class D audio power amplifier output power regulating circuit, can be done by outside chip pins input voltage or programmatically dynamically adjust the output power of the power amplifier. Control method using the method of the biggest limit input signal respectively introduces the control principle and circuit realization of the circuit. Test results show that the circuit has reached the good adjustment effect has good linearity adjustment, improve the reliability of the high power amplifier circuit.

class D power amplifier; power regulation; amplitude limit

TN402

A

1681-1070(2015)07-0014-03

2015-01-21