基于ATE的FPGA配置文件生成方法

赵 桦,章慧彬

(中国电子科技集团公司第58研究所,江苏 无锡 214035)

基于ATE的FPGA配置文件生成方法

赵 桦,章慧彬

(中国电子科技集团公司第58研究所,江苏 无锡 214035)

FPGA 是在PAL、GAL、EPLD、CPLD 等可编程器件的基础上进一步发展的产物。它是作为ASIC 领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路有限的缺点。用UltraFlex测试系统(ATE)测试FPGA的方法进行阐述,分析了不同电压模式的配置文件产生方法的差异。

FPGA;测试技术;ATE;配置文件

1 引言

可编程逻辑器件(Programmable Logic Device,PLD)起源于20 世纪70 年代,是在专用集成电路(ASIC)的基础上发展起来的一种新型逻辑器件,是当今数字系统设计的主要硬件平台,其主要特点是完全由用户通过软件进行配置和编程,从而完成某种特定的功能,且可以反复擦写。在修改和升级PLD 时,不需额外地改变PCB 电路板,只是在计算机上修改和更新程序,使硬件设计工作成为软件开发工作,缩短了系统设计的周期,提高了实现的灵活性并降低了成本。因此其获得了广大硬件工程师的青睐,形成了巨大的PLD 产业规模。

目前常见的PLD 产品有:编程只读存储器(Programmable Read Only Memory,PROM)、 现 场可编程逻辑阵列(Field Programmable Logic Array,FPLA)、可编程阵列逻辑(Programmable Array Logic,PAL)、通用阵列逻辑(Generic Array Logic,GAL)、可擦除的可编程逻辑器件(Erasable Programmable Logic Array,EPLA)、复杂可编程逻辑器件(Complex Programmable Logic Device,CPLD)和现场可编程门阵列(Field Programmable Gate Array,FPGA)等类型。PLD 器件从规模上又可以细分为简单PLD(SPLD)、复杂PLD(CPLD)以及FPGA。它们内部结构的实现方法各不相同。

FPGA 是在PAL、GAL、EPLD、CPLD 等可编程器件的基础上进一步发展的产物。它是作为ASIC 领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路有限的缺点。

UltraFlex集成电路测试系统控制软件利用EXCEL表格作为集成测试管理系统,Visual Basic作为编程语言,在其提供的模板基础上根据需要编辑相应的功能。测试系统软件包括:测试处理、测试数据显示、数据统计、测试程序管理、测试程序框架自动生成等,多种功能集成在一起,有独立的pattern产生器,可以产生异步的pattern等性能,常用于测试复杂的大型数字电路。

2 FPGA的结构组成

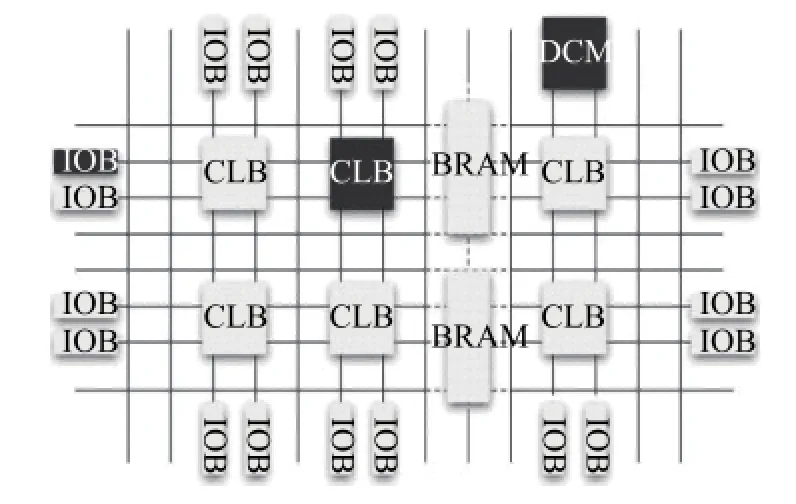

FPGA 芯片主要由6 部分组成,分别为:可编程输入输出单元、基本可编程逻辑单元、完整的时钟管理、嵌入块式RAM、丰富的布线资源、内嵌的底层功能单元和内嵌专用硬件模块,如图1所示。

图1 FPGA芯片的内部结构

3 FPGA不同电压模式配置文件生成方法

由于基于LUT 的FPGA 具有很高的集成度,其器件密度从数万门到数千万门不等,可以完成极其复杂的时序与逻辑组合逻辑电路功能。FPGA大多有可配置的高性能I/O驱动和接收器,支持多种电压标准,不仅可以编程控制输出功率和回转率,还支持DCI(Digitally Controlled Impedance),还具有在内部产生参考电压的功能。

I/O单元是芯片与外界电路的接口部分,完成不同电气特性下对输入/输出信号的驱动与匹配要求。FPGA 内的I/O按组分类,每组都能够独立地支持不同的I/O标准。通过软件的灵活配置,可适配不同的电气标准与I/O物理特性,可以调整驱动电流的大小,可以改变上、下拉电阻。

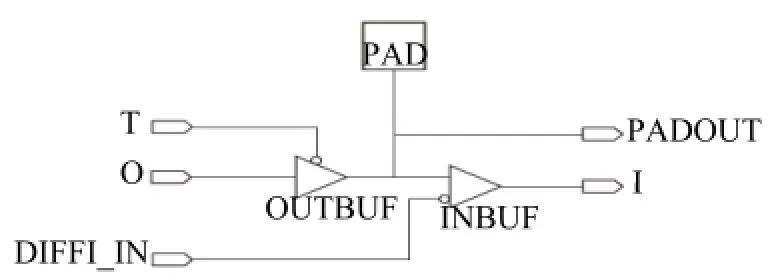

目前I/O口的频率也越来越高,一些高端FPGA通过DDR 寄存器技术可以支持高达2 GB/s 的数据速率。每个I/O都包含输入、输出和三态可选驱动。这些驱动可被配置成不同的I/O标准。要实现差分I/O也只需选择2个I/O口配对即可。具体包括单端 I/O标准(LVCMOS、HSTL、SSTL等)和差分 I/O标准(LVDS、HT、LVPECL、BLVDS、差分 HSTL、SSTL)。

图2 I/O口的基本结构

3.1 LVCMOS

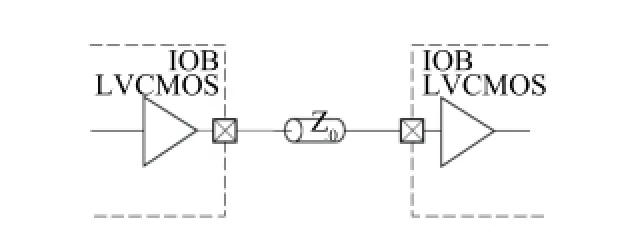

LVCMOS(Low Voltage Complementary Metal Oxide Semiconductor)是以广泛使用的应用于CMOS晶体管的标准。这个标准是在JEDEC(JESD 8-5)中定义的。LVCMOS模式还可以分为LVCMOS12、LVCMOS15、LVCMOS18、LVCMOS25几种模式。

FPGA 是由存放在片内的RAM 来设置其工作状态的,因此工作时需要对片内RAM 进行编程。用户可根据不同的配置模式,采用不同的编程方式。FPGA有4种配置模式:(1)并行模式:并行PROM、Flash配置FPGA;(2)主从模式:一片PROM 配置多片FPGA;(3)串行模式:串行PROM 配置FPGA;(4)外设模式:将FPGA 作为微处理器的外设,由微处理器对其编程。

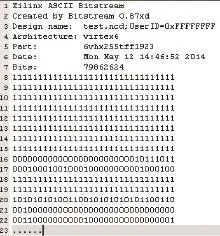

为了实现利用UltraFlex对FPGA进行测试,我们采用并行模式对片内RAM进行编程。利用ISE工具,将输入输出口设置为某功能,例如反向器,并且输入输出口的标准也设置为LVCMOS,编译产生一个配置文件。

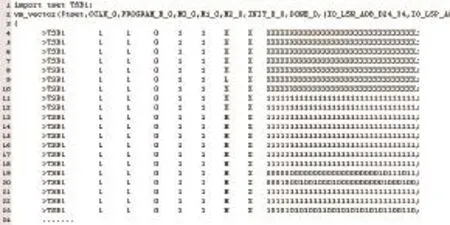

利用这个配置文件,就可以在UltraFlex测试系统上生成一个pattern,在UltraFlex测试系统上通过设置FPGA的控制脚电压将pattern写入FPGA内部的RAM,达到配置FPGA的目的。

配置成功后可以再利用UltraFlex编写一个功能性的pattern,从而验证配置是否成功。同时可以测试在此模式下的漏电压、漏电流、延迟时间、上升时间等交/直流参数是否满足FPGA的性能参数列表要求。

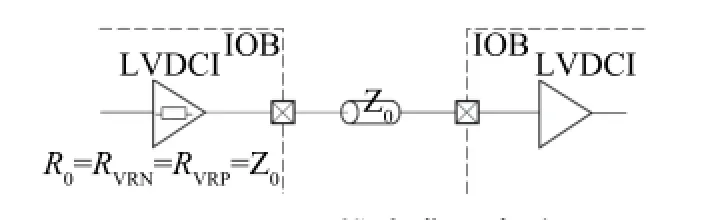

3.2 LVDCI

与LVCMOS设置类似,将输入输出口设置为LVDCI(Low Voltage Digitally Controlled Impedance)模式。再利用ISE工具生成配置文件,在UltraFlex测试系统上生成一个pattern,在UltraFlex测试系统上通过设置FPGA的控制脚电压将pattern写入FPGA内部的RAM,达到配置FPGA的目的。配置成功后就可以利用UltraFlex对FPGA在LVDCI模式下的交直流参数进行测试了。

图3 生成的配置文件

图4 利用配置文件产生的pattern

图5 LVCMOS模式典型电路

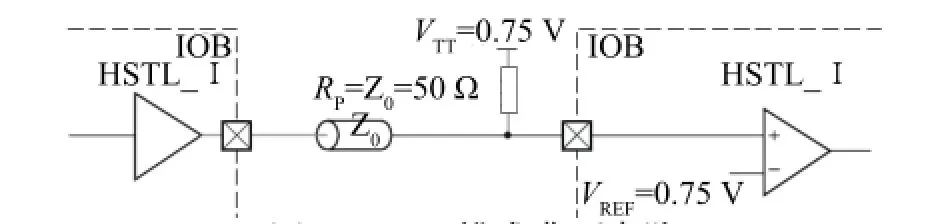

3.3 HSTL

为了便于管理和适应多种电器标准,FPGA 的IOB 被划分为若干个组(bank),每个bank的接口标准由其接口电压VCCO决定,一个bank只能有一种VCCO,但不同bank的VCCO可以不同。只有相同电气标准的端口才能连接在一起,VCCO电压相同是接口标准的基本条件。

图6 LVDCI模式典型电路

图7 HSTL模式典型电路

HSTL(High-Speed Transceiver Logic)是由IBM(EIA/JESD8-6)提出的一个高速总线标准。这个标准在配置FPGA时要求有一个差分放大输入缓存和一个推挽式的输出缓存。所以在设置输入输出口为HSTL模式后,还要在ISP工具的约束文件中对I/O口的每一个bank加一个参考电压VREF,这样产生的配置文件在UltraFlex上才能配置成功。配置成功后就可以利用UltraFlex对FPGA在LVDCI模式下的交直流参数进行测试了。处理方式与HSTL模式相类似的还有SSTL模式。

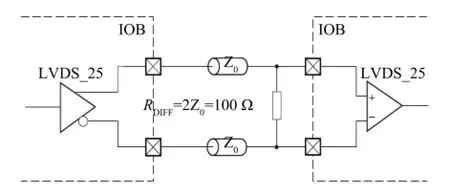

3.4 LVDS和Extended LVDS

LVDS(Low Voltage Differential Signaling)是一个在很多系统中广泛使用的高速界面。它遵循的EIA/ TIA电气标准使系统和硬件设计更加简便。由于LVDS是差分结构,要先设置一对差分脚,这个需要在约束文件中列出,FPGA提供了很多成对的I/O口,选取几组作为输入口,再选取单独的I/O口作为输出口。输入输出口都设置为LVDS模式,相应的bank也要设置VREF电压,这样产生的配置文件才能真正配置成功FPGA。

图8 LVDS模式典型电路

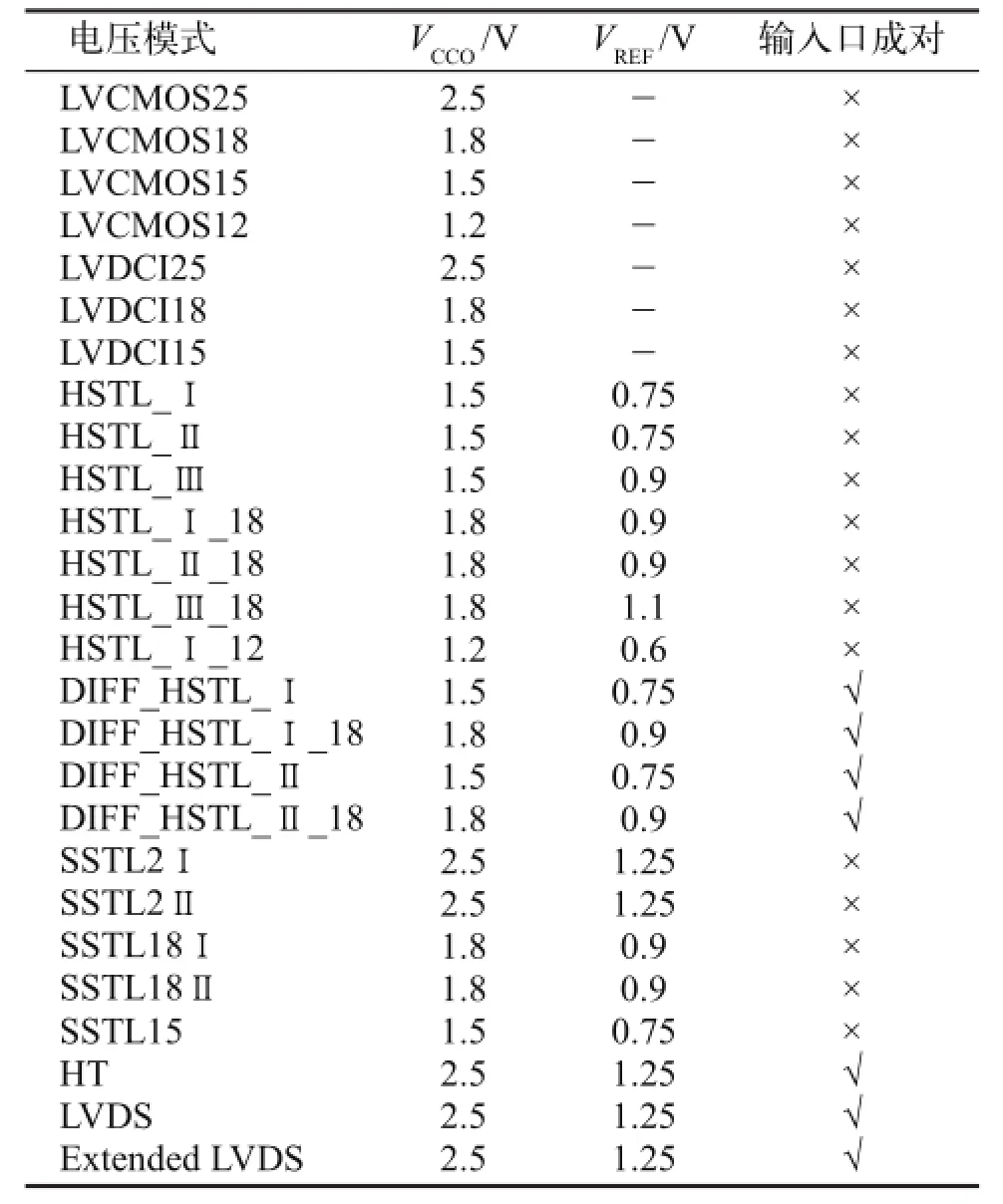

表1 配置文件参数设置对比表

综上所述,可以把FPGA上的几种电压模式下的配置文件设置方法总结为表1。

4 结论

FPGA具有很高的集成度,其器件密度从数万门到数千万门不等,可以完成极其复杂的时序与逻辑组合逻辑电路功能,适用于高速、高密度的高端数字逻辑电路设计领域。而UltraFlex测试系统由于其优越的性能,在开发测试FPGA性能方面应用也越来越广泛。

[1] 夏宇闻. Verilog 数字系统设计教程[M]. 北京:北京航空航天大学出版社,2009.

[2] 刘宝琴. 数字电路与系统[M]. 北京:北京清华大学出版社,1993.

[3] 夏宇闻. 复杂数字电路与系统的Verilog HDL设计[M]. 北京:北京航空航天大学出版社,1998.

作者简介:

包 诚(1981—),男,安徽人,目前在中国电子科技集团公司第38研究所主要从事电子装联工艺工作。

Research on Configuration Files of FPGA Based on the ATE

ZHAO Hua, ZHANG Huibin

(China Electronics Technology Group Corporation No.58 Research Institute, Wuxi 214035, China)

FPGA is developed based on PAL, GAL, EPLD, CPLD programmable application. It is showed as a half customized circuit. It solves the problems of customized circuit and overcomes the shortcoming of former programmable application. This text explains the working theory of UltraFlex(ATE)integrated operational testing method, analyses the difference of configuration files between different voltage standard.

FPGA; testing technology; ATE; configuration file

TN407

A

1681-1070(2015)07-0010-04

赵 桦(1979—),女,江西南昌人,测试工程师,硕士学历,2003年毕业于西南交通大学测试计量及仪器仪表专业,主要从事集成电路测试工作。

2015-05-12