电路软差错率评估综述

电路软差错率评估综述

王真, 李舫, 卢芳芳

(上海电力学院 计算机科学与技术学院, 上海200090)

摘要:综述了近10年来软差错影响下的电路可靠性分析方法,主要从系统结构级、寄存器传输级、门级、电路级4个抽象层次进行了分析,在每个抽象层次上再依据方法属性进行了分类比较.结果表明,多数情况下,基于的抽象层次越高,时间开销越小而准确度越低;不同属性的方法中模型解析法更简易可行,而故障模拟方法更贴合实际.

关键词:可靠性分析; 电路级; 门级; 系统结构级

基金项目:上海电力学院人才启动

中图分类号:TP302.8;TN406文献标志码: A

SurveyonCircuitSoftErrorRateEvaluation

WANGZhen,LIFang,LUFangfang

(School of Computer Science and Technology, Shanghai University of Electric Power, Shanghai200090, China)

Abstract:A survey of reliability analysis methods on soft error of recent ten years is conducted,which is expected to be helpful to future research. During the comprehensive methods introduction,they are categorized into architecture-level,register-transfer-level (RTL),gate-level and circuit-level,and are compared according to method property in each level. In conclusion,it is found that in most cases,the higher the base abstract level is,the less the time overhead is and the lower accuracy is,and among methods with different property,the analytical method is maneuverable,while the fault simulation method is closer to actual issue.

Keywords:reliabilityanalysis;circuitlevel;gatelevel;architecturelevel

近年来,随着数字集成电路制造技术的迅速发展,人们加快了对电子科技的研究和开拓,同时越来越多的应用领域对超大规模集成电路(VeryLargeScaleIntegration,VLSI)的可靠性提出了更高的要求,如航天飞机飞行姿态控制系统、原子核反应堆控制系统、导弹防御系统、铁路运输信号控制系统及金融部门的监督系统等.VLSI的可靠性分析是高可靠设计的必备前提,其相对准确省时的可靠性评估技术可以有效指导电路设计,帮助设计者选择节省开销的高可靠性结构.

本文主要针对近年来软差错影响下的电路可靠性问题,从不同抽象层次进行全面的分析和总结.软差错影响的分析方法,从方法属性来分,一般包括基于模拟的故障注入方法、通过强辐射压力测试的实验分析方法和建立模型计算评估的解析方法;从分析过程基于的抽象层次来看,主要包括电路级、门级、寄存器传输级(Registor-transfer-level,RTL)和系统结构级.本文以抽象层次进行粗分类,以方法属性进行细分类,对受软差错影响的电路可靠性分析方法进行介绍.

1软差错的产生及量化

软差错主要由中子和alpha粒子两大因素所致.受到这两类粒子的撞击,晶体管源级及扩散结点就会积聚电荷,当积聚量超过关键电荷值(Qcrit)后,则会导致逻辑器件的状态翻转或者位差错.由于这种故障差错不会导致器件出现永久性错误,所以称为软差错.一般而言,高能粒子引起的发生频率较高的瞬时效应包括单事件翻转(SingleEventUpset,SEU)和单事件瞬态(SingleEventTransient,SET).当高能粒子轰击锁存器或触发器等时序逻辑电路时,将引发SEU,时序逻辑电路的值将发生翻转,错误的值将保持到下一个值写入.高能粒子轰击组合逻辑电路,将发生SET,产生一个宽0.35~1.3ns的毛刺,[1]并且有可能沿组合逻辑通路传递,如果毛刺恰好被时序逻辑采样到,将会导致集成电路功能错误.

作为一个常用的可靠性度量指标,单位时间失效数(Failure-in-time,FIT)表示运行109h内出现的失效次数,它用于度量工业逻辑模块的差错率,与平均失效前时间(MEAN Time To Failures,MTTF)呈反相关,MTTF为1年,相当于FIT为114 155,即等于109/(24×365).在一个典型结构的芯片上,存储阵列、锁存单元和组合逻辑都会受到软差错的威胁.逻辑电路对软差错一般存在逻辑屏蔽、电气屏蔽和锁存窗屏蔽3种屏蔽作用,因此软差错率(Soft Error Rate,SER)可以通过错误传播到原始输出或者被锁存器捕获的概率来度量.

2电路级可靠性分析

2.1 故障注入法

电路级的软差错分析多采用模拟故障注入方法,即先分析故障机制建立电路级故障模型,依据模型在SPICE或HSPICE等工具模拟的电路的内部节点上注入故障,仿效由于粒子撞击、电荷积聚而形成的瞬时脉冲,即单事件瞬态SET;然后经历敏化通路上的传播,观察组合逻辑输出端的脉冲变化,包括振幅高度和时间宽度,分析SET的削弱程度,结合触发器的上升沿与下降沿来分析锁存窗屏蔽,用以推导SEU的发生概率.

电路级的故障模型主要有电流模型和电压模型.比较典型的电流模型有MESSENGERGC[2]提出的双指数脉冲变化模型:

(1)

式中:I0——最大电流;

t1——结上电荷收集时间;

t2——离子踪迹建立时间.

该模型主要针对alpha粒子撞击PMOS器件的情形建模,改变参数可以得到对其他类型瞬时故障的仿真.

电压脉冲在传播中的振幅变化不大,而宽度变化较大,变化幅度因注入位置、电荷积聚量和注入脉冲波形的不同而不同.ALEXANDRESCUD等人[3]在模拟故障传播过程中使用标准延迟格式文件提供时序信息,并将电路的组合逻辑与锁存单元分开实验,从而加快了故障模拟过程,减少了测试电路中事件发生的次数.RAJEEVRR等人[4]建立了基于查找表的威布尔波形转换函数,脉冲在传播过程中查找对应的波形转换函数,波形转换的结果相同则合并为一次,从而大大降低了时间开销.ADAMW等人[5]在前者的基础上引入了威布尔累积分布,用以拟合上升沿和下降沿的电压脉冲波形,继而提出模拟脉冲传播算法,以便准确模拟故障.

在故障产生和传播的基础上,故障被锁存的概率将最终决定电路对瞬时故障SET的敏感度.瞬时故障是否被捕获由触发器的数据建立时间tsetup,数据保持时间thold,以及传播到寄存器输入的脉冲宽度w决定.例如文献[3]推出的锁存概率为:

(2)

式中:Tclk——时钟周期;

w——到达寄存器的脉冲宽度.

还有一类是基于故障注入的解析方法,通过分析电荷收集量与关键电荷值的关系,以变化的电荷量为主要参数代入解析模型,直接计算SER的值.[6]这类解析式中,软差错率跟粒子流强度、撞击节点横截面积、电荷收集效率呈正比,与关键电荷值呈反比.但由于解析方法一般不考虑逻辑屏蔽作用,故存在一定的局限性.

在电路级注入故障的方法和工具已有很多,如SERA,[7]SEAT-LA,[8]以及针对存储单元的ROBAN,[3]DASIE,[9]TMC-DASIE[10]等方法,这些方法通常模拟电路的内部属性.在此基础上还有学者考虑了环境等外界条件的影响,如乔治亚理工学院集成CadenceSpectre模拟器开发了CAD可靠性分析工具,[11]用以分析电迁移和热载流子效应影响下芯片的可靠性;RAMAKRISHNANK等人[12]基于SEAT-LA工具,分析了不同电源电压、工作温度、热载流子注入、负偏置温度不稳定性等因素对组合逻辑电路SER的影响.

2.2 模型分析法

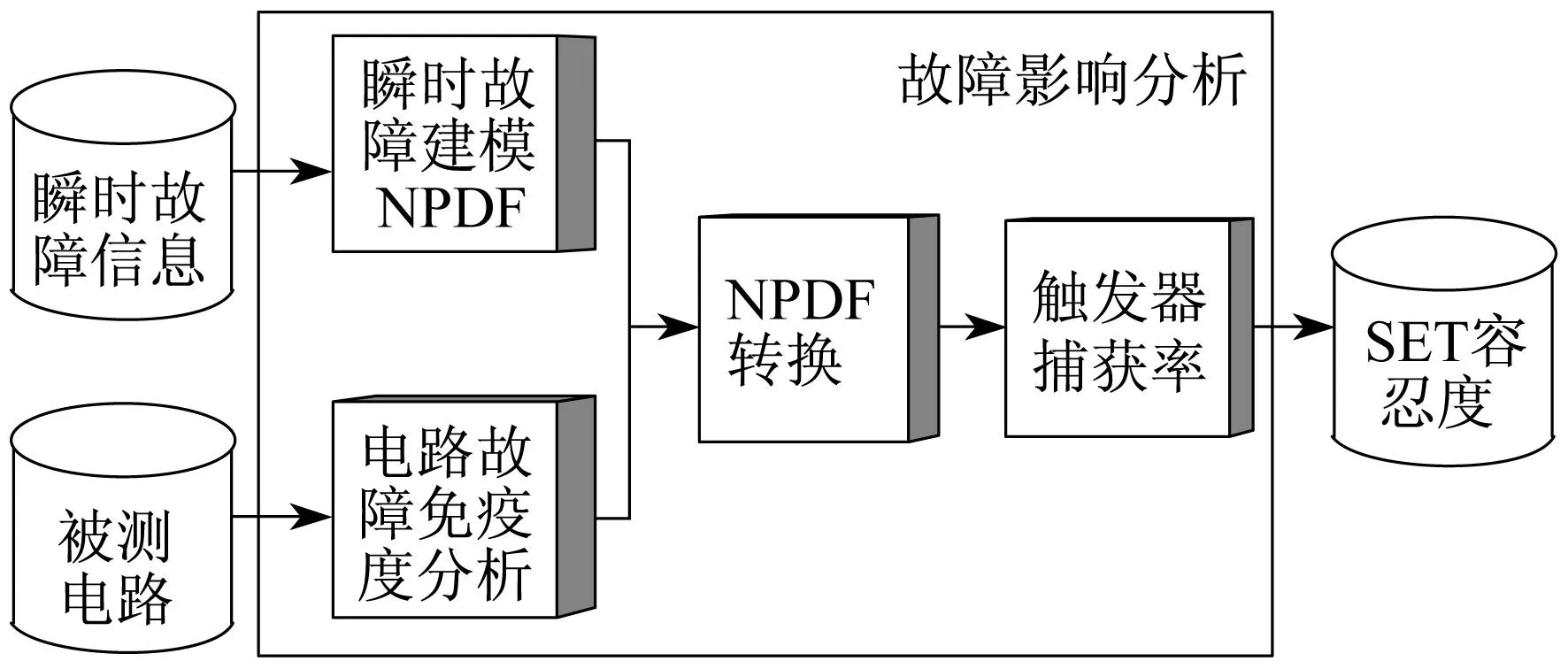

文献[13]提出了一种矩阵建模的分析方法,其中考虑了SET的产生、传播、被锁存以及3种屏蔽作用.故障影响分析如图1所示.

图1 故障影响分析

主要分为如下4个部分:

(1) “瞬时故障建模”过程通过矩阵的形式描述SET发生的概率,即建立噪声概率密度函数(NoiseProbabilityDensityFunction,NPDF);

(2) “电路故障免疫度分析”中分别通过建立矩阵和计算概率量化了电气屏蔽、锁存窗屏蔽和逻辑屏蔽3种屏蔽作用;

(3) 通过“NPDF转换”过程,以矩阵运算的形式反应故障在敏化通路上的传播情况;

(4) 设计解析式计算“故障捕获率”衡量整个电路的SER.

该方法考虑全面,设计完备,但较为繁杂,实施较为不便.

3门级可靠性分析

门级分析软差错影响的方法可以分为两类:一是结合电路级故障注入的综合分析方法;二是基于信号概率的门级模型分析方法.

3.1 综合分析方法

综合分析方法通常使用SPICE模拟电路,依据式(1)或其他电流变化模型注入故障,在电路级收集瞬时脉冲的产生以及传播中衰减的信息,用以分析电气屏蔽,然后在门级建立模拟器,或通过解析方法描述逻辑屏蔽,最后在结合前两个阶段的基础上提取参数,计算锁存概率.该类方法中的电路级模拟仅用于提取脉冲信息,结合了门级的分析,时间开销有所减小.

(1) 门级模拟器的建立文献[14]采用将故障传播过程中时间信息折合成结构信息的方法,将不同时间间隔后的同一个门看作不同的门,作为扩展部分重新模拟电路结构,从而可以实施零延迟的故障模拟而不损失准确性.通过ISCAS85基准电路上的实验表明,与VHDL的时序模拟器实现方法相比,在注入同样多故障时,这种扩充电路的模拟方法的速度可以提高5 000倍,而输出的差错相同.文献[15]利用FASER工具在门级运用BDD结构对故障传播建模,并叠加电路级的脉冲信息,通过电路分割减小复杂度.通过7个组合电路上的实验统计表明,FASER方法的实施速度是基于SPICE模拟方法的9 000倍,而误差在12%.ZHANGM等人开发了SERA工具,[16]结合物理层因素推导了门级高层抽象模型,运用图论算法和故障模拟方法分析逻辑屏蔽机制,采用HSPICE电路模拟分析电气屏蔽和锁存窗屏蔽作用,与基于蒙特卡罗的模拟方法相比,其加速比达到105的数量级,而误差损失不到5%.

(2) 结合解析模型的分析方法MOHANRAMK等人[17]在分析SER时给出了RSEU(n)×Psensitized(n,l)×Platched(n,l)的解析模型,计算逻辑电路中的节点n到锁存器l的软差错易感度.其中,RSEU(n)表示在节点n发生SEU后逻辑值被改变的几率;Psensitized(n,l)表示从n到l存在敏化通路的概率;Platched(n,l)表示n点故障被l锁存的概率.ANDREKN等人[18]面向组合电路,通过所有门失效率FRgate的和来衡量整个电路的失效率,其中FRgate= GserGlit observEMF,这里门的软差错率Gser由输入向量出现的概率乘以这种输入组合下易感性系数得到;毛刺可观度Glit observ表示毛刺在没被其他门逻辑屏蔽的情况下传播到原始输出的概率;电气屏蔽因子EMF表示一个毛刺从产生位置到原始输出的传播通路上不被其他门削弱掉的概率.FRgate越高,则这个门对电路软差错率的影响越大.最终算得的SERcircuit可以用于比较针对软差错的不同容错设计,帮助设计者做出选择.

3.2 门级建模

这类方法通过计算发生在门级的软差错传播到电路原始输出的概率来衡量失效率,计算过程通常考虑电路的拓扑结构和传播路径信息,以及电路中各个门的类型和连接方式.其典型的方法有计算单个输出节点SER的TP算法、[19]通过计算差错传播率表征电路SER的EPP方法,[20]以及通过概率转移矩阵计算电路整体可靠度的PTM方法.[21]

我们对上述3种方法进行了全面的分析与比较,结果表明,TP方法和EPP方法可以计算部分电路的失效率;PTM方法可度量整个电路的可靠性,故其较为完备准确.[22]但PTM方法的复杂度为指数级,只能用于中小规模电路,为了解决此问题,文献[23]和文献[24]分别提出了概率决策图和电路分割的方法,文献[25]针对改进后的PTM模型的精度问题提出宏门的概念,将电路级因素考虑其中.文献[26]基于线性复杂度的EPP方法,提出了S-EPP方法,专门用于对时序单元差错锁存率的评估.

另外,通过门级概率差错传播模型度量电路可靠性的方法还包括基于布尔差分的差错率计算(BooleanDifference-basedErrorCalculator,BDEC)[27]和PGM模型.[28]PGM模型针对每个PO端计算,若电路中没有扇出则为线性复杂度;否则,采用多路径算法以便缓解指数增长的复杂度.与PGM相比,BDEC对输入向量较为敏感,不同的原始输入组合会引起可靠度较大波动.[29]

在门级估计SER的方法一般先以门为单位,建立模型计算差错率,然后沿敏化通路逐级计算直到PO端.这类方法主要分析了逻辑屏蔽的影响,属于局部分析方法.而文献[30]将电气屏蔽因素结合到EPP方法中,通过电路级的模拟以及统计信息使分析过程更加全面准确.

4RTL级及系统级可靠性分析

系统级的可靠性评估方法可以分为故障注入法和故障分析法.

4.1 故障注入法

故障注入法是一种按照选定的故障类型在目标计算机系统中人为地产生故障,并对系统响应信息收集处理的实验过程.目标计算机系统可以是系统原型,也可以是系统的一个抽象模型.一般来说,直接向硬件原型系统注入故障准确度高,但评估周期长,不易控制和观测;向抽象模型注入故障可以方便地控制故障的注入时间和注入地点,能够直接观测故障在模型中的行为,但要仔细平衡抽象层次、模拟速度以及准确度3者之间的关系.

基于原型系统的方法多采用非接触式的故障注入,通过特定的物理手段(包括重离子辐射、电磁干扰、激光放射等)从外界对目标系统施加影响,引起目标芯片内的突发性电流.该方法的优点在于可以模拟目标系统在真实环境中所遭遇到的物理现象,缺点是不能精确地确定重离子辐射或电磁场产生的时刻,导致无法控制故障注入的确切时间和位置.

系统级的软差错率可以通过存储器和逻辑单元的原始差错率,即无工作负载时的分析结果及其降级因子合成得到:

(3)

式中:Amem,Alogic——分别对应存储器和逻辑电路的降级因子,用以反映各自占系统差错率的比例,其取值依赖于芯片结构、版图布局和运行的应用程序.

而对原始SER,则可以通过在强辐射的实验环境下统计单个位的失效率来测量,例如文献[31]模拟alpha粒子和中子辐射观察SER,文献[32]和文献[33]探讨了μ介子对软差错率的影响.

基于原型系统的方法往往遇到用于测试的存储单元类型以及逻辑单元数目受限的问题,于是提出了基于模拟的故障注入方法,即采用位翻转的故障模型,通过VHDL/Verilog和HDL在RTL级描述系统,注入故障并运行一组典型工作负载,观察系统运行情况,分析可靠性影响因素.

文献[34]对龙芯1号进行了软差错敏感性分析,同时运行GoldenCPU和FaultCPU监视两个处理器的运行过程,收集故障信息并进行比较,将软差错敏感性定义为导致处理器运行失效的软差错总数占故障注入软差错总数的比例.文献[35]在对其设计的微控制器FT51评估容错性能时,采取了随机复位寄存器的值,以及在组合逻辑中模拟毛刺、检测时将程序的运行轨迹与预期轨迹相比较的方法.文献[36]针对AMD的一款新设计的微处理器Bulldozer,在RTL级注入差错,通过计算逻辑降级屏蔽因子来分析软差错敏感单元,以期在结构设计中有针对性地进行防错.

基于模拟的故障注入方法更多地用于目标系统被制造之前对设计、功能进行验证和评估.该方法不存在对目标系统可访问性方面的限制,并且可以精确监控所注入的故障,这样就可以直接验证设计,从而节省了生产成本,同时提前对产品容错特性有了量化的评价.其缺点在于建立模型所需的参数和设计细节往往很难得到,而且建模也比较耗时.而基于原型的故障注入方法可以直接发现目标系统设计中的问题,还可以较准确地考评系统在其所处的典型应用环境中对恶劣条件的反应,但需要在原型系统设计之后.

4.2 故障分析法

故障分析法源于MUKHERJEESS等人提出的结构脆弱因子(ArchitecturalVulnerabilityFactors,AVF)分析.[37]AVF是指发生在某一部件中的软差错能够引起程序执行结果错误的概率,其通过在结构级和微结构级分析结构正确执行位(ArchitecturallyCorrectExecutionbit,ACEbit)来计算.某一结构的AVF值即为该结构包含ACE位的时钟数占总时钟数的比例.AVF值越小,表明软差错对该结构的影响越小,也即该结构在软差错影响下的可靠性较好.

AVF是在系统级分析一个故障位对程序最终输出的影响.AVF的计算方法包括基于ACE位的分析方法[58]和故障注入统计法[38]等.结合AVF,SHUBHENDUSM等人[39]给出了详细的失效率的因子分析法,其流程如图2所示.图2中,每一层父结点都是子结点的乘积,直至算出根结点部件FIT,而系统FIT为部件FIT的和.

图2 系统失效率计算因子分析法示意

近年来,有研究者将ACE分析结合到故障注入中,提出CriticalFault注入方案,通过对故障位的脆弱性分析找出不同指令在不同寄存器上的ACE位,然后在这样的比特位上有导向地注入故障,从而使多数故障在无容错机制的情况下不会被屏蔽降级.[40]基于CriticalFault的故障注入统计法能够更加严格地评测容错系统的差错覆盖率.

5方法比较

5.1 基于抽象层次的比较

本文分类的主干线即电路(或系统)的抽象级别,介绍的方法由低层到高层,包括电路级、门级、RTL级及系统级.一般而言,基于的抽象层次越低,方法的准确性就越高,尤其是通过故障注入方法来分析可靠性,抽象级别接近物理实现,则可以进行更为精确的故障建模,得到更为真实的故障行为分析.但低层方法的时间开销较大,过程更复杂,难以用于大规模复杂的电路结构.例如,具有统计意义的大量故障注入,若是在低层模拟复杂结构,耗时难以想象.解析方法同理,基于抽象级别越低,则考虑的因素和参数更多,模型更加复杂.反之,基于的抽象级别越高,电路可靠性的度量过程及模型相对简单,容易实施,但会在一定程度上损失其准确性.

5.2 基于方法属性的比较

各个抽象级别的分析按照方法属性又可以分成故障注入法和解析模型法.在同一个抽象级别上,解析模型方法省时、易处理,故障注入方法准确度高但时间开销大.

6结语

本文面向软差错影响下的电路可靠性分析问题,从不同层面、多个角度介绍并分析了近10多年来的各种方法.各类方法都有其局限性和优越性,当针对具体的可靠性评估目标时,应根据需要和评估对象的特点选择合适的方法类型,或者结合不同方法,采取低层的模拟信息叠加到高层的解析模型、低层故障映射到高层进行分析等措施,用以平衡其准确性及时间开销.

参考文献:

[1]EATONP,BENEDETTOJ,MAVISD,et al.Singleeventtransientpulsewidthmeasurementsusingavariabletemporallatchtechnique[J].IEEETrans.onNuclearScience, 2004,51(6): 3 365-3 368.

[2]MESSENGERGC.Collectionofchargeonjunctionnodesfromiontracks[J].IEEETrans.onNuclearScience,1982,29(6): 2 024-2 031.

[3]ALEXANDRESCUD,ANGHELL,NICOLAIDISM.NewmethodsforevaluatingtheimpactofsingleeventtransientsinVDSMICs[C].Proc.ofthe17thIEEEInt.Symp.onDefectandFaultToleranceinVLSISystems,Vancouver,2002: 99-107.

[4]RAJEEVRR,KAVIRAJC,DAVIDTB,et al.Computingthesofterrorrateofacombinationallogiccircuitusingparameterizeddescriptors[J].IEEETrans.onComputer-AidedDesignofIntegratedCircuitsandSystems,2007,26(3):468-479.

[5]ADAMW,SPYROST.Transientpulsepropagationusingtheweibulldistributionfunction[C].IEEEInt’lSymposiumonDefectandFaultToleranceinVLSIandNanotechnologySystems(DFT),Austin,TX,USA,2012: 109-114.

[6]RAMANARAYANANR,DEGALAHALV,VIJAYKRISHNANN,et al.Analysisofsofterrorrateinflip-flopsandscannablelatches[C].IEEEInt.SOCConference,Portland,2003: 231-234.

[7]ZHANGM,SHANBHAGNR.Asofterrorrateanalysis(SERA)methodology[C].Proc.ofInternationalConf.onComputerAidedDesign.Taipei,Taiwan,2004: 111-118.

[8]RAJARAMANR,KIMJS,VIJAYKRISHNANN,et al.SEAT-LA:asofterroranalysistoolforcombinationallogic[C].Proceedingsofthe19thInternationalconferenceonVLSIDesign,Hyderabad,India,2006: 499-502.

[9]HUBERTG,PALAUJ-M,CASTELLANI-COULIEK,et al.Detailedanalysisofsecondaryions’effectforthecalculationofneutron-inducedSERinSRAMs[J].IEEETrans.onNuclearScience,2001,48(6): 1 953-1 959.

[10]HUBERTG,BOUGEROLA,MILLERF,et al.Predictionoftransientinducedbyneutron/protoninCMOScombinationallogiccells[C]. 12thIEEEInt.On-lineTestingSymposium,LakeofComo,Italy,2006:63-74.

[11]XUANX,CHATTERJEEA.Sensitivityandreliabilityevaluationformixed-signalICsunderelectromigrationandhot-carriereffects[C].IEEEInt’lSymp.OnDefectandFaultToleranceinVLSISystems,SanFrancisco,California,2001: 323-328.

[12]RAMAKRISHNANK,RAJARAMANR,SURESHS,et al.VariationimpactonSERofcombinationalcircuits[C].The8thInternationalSymposiumonQualityElectronicDesign(ISQED'07),SanJose,2007: 911-916.

[13]ZHARC,BAIXL,DEYS.Evaluatingtransienterroreffectsindigitalnanometercircuits[J].IEEETrans.onReliability,2007,56(3): 381-391.

[14]REORDAMS,VIOLANTEM.AccurateandefficientanalysisofsingleeventtransientsinVLSIcircuits[C].IEEEInt’lOn-lineTestingSymp.,KosIsland,Greece,2003: 101-105.

[15]ZHANGBin,WANGWeishen,ORSHANSKYM.FASER:fastanalysisofsofterrorsusceptibilityforcell-baseddesigns[C].The7thInt’lSymp.onQualityElectronicDesign(ISQED`06),2006: 1-6.

[16]ZHANGM,SHANBHAGRN.Soft-error-rate-analysis(SERA)methodology[J].IEEETrans.onComputer-aidedDesignofIntegratedCircuitsandSystems,2006,25(10):2 140-2 155.

[17]MOHANRAMK,TOUBANA.Cost-effectiveapproachforreducingsofterrorfailurerateinlogiccircuits[C].InternationalTestConference,2003: 893-901.

[18]ANDREKN,SAMIRJ,GORANJ.Combinationallogicsofterroranalysisandprotection[C].The12thIEEEInt’lOn-lineTestingSymposium,LakeofComo,Italy,2006:99-104.

[19]KIMJS,NICOPOULOSC,VIJAKRISHNANN,et al.Aprobabilisticmodelforsoft-errorrateestimationincombinationallogic[C].Proc.ofthe1stIntWorkshoponProbabilisticAnalysisTechniquesforRealTimeandEmbeddedSystems,Italy,2004: 25-31.

[20]ASADIG,TAHOORIMB.Ananalyticalapproachforsofterrorrateestimationindigitalcircuits[C].IEEEIntSymponCircuitsandSystems,Kobe,2005: 2 991-2 994.

[21]KRISHNASWAMYS,VIAMONTESGF,MARKOVIL,et al.Accuratereliabilityevaluationandenhancementviaprobabilistictransfermatrices[C].ProcoftheDesign,AutomationandTestinEuropeConferenceandExhibition,Orlando,2005: 282-287.

[22]WANGZhen,JIANGJianhui,YANGGuang.Implementationandanalysisofprobabilisticmethodsforgate-levelcircuitreliabilityestimation[J].TsinghuaScienceandTechnology. 2007,12(S1): 32-38.

[23]ABDOLLAHIA.Probabilisticdecisiondiagramsforexactprobabilisticanalysis[C].Proc.Int’lConferenceonComputerAidedDesign,SanJose,CA,2007: 266-272.

[24]王真,江建慧. 基于概率转移矩阵的串行电路可靠度计算方法[J].电子学报,2009,37(2): 241-247.

[25]XIAOJ,JIANGJH,ZHUX,et al.Amethodofgate-levelcircuitreliabilityestimationbasedoniterativePTMmodel[C].IEEE17thPacificRimInternationalSymposiumonDependableComputing,Pasadena,USA,2011:276-277.

[26]HOSSEINA,MEHDIBT.Softerrormodelingandprotectionforsequentialelements[C].The20thIEEEInt'lSymposiumonDefectandFaultToleranceinVLSISystems,Monterey,USA,2005: 463-474.

[27]MOHYUDDINN,PAKBAZNIAE,PEDRAMM.Probabilisticerrorpropagationinlogiccircuitsusingthebooleandifferencecalculus[C]. 26thIEEEInt`lConf.onComputerDesign,LakeTahoe,2008: 7-13.

[28]HANJ,CHENH.Reliabilityevaluationoflogiccircuitsusingprobabilisticgatemodels[J].MicroelectronReliability,2011,51(2): 468-476.

[29]SINGHNSS,HAMIDNH.Evaluationofcircuitreliabilitybasedondistributionofdifferentsignalinputpatterns[C]. 8thIEEEInt`lColloquiumonSignalProcessinganditsApplications,Malacca,2012: 5-9.

[30]HOSSEINA,MEHDIBT.Estimatingerrorpropagationprobabilitieswithboundedvariances[C]. 22ndIEEEInt’lSymp.onDefectandFaultToleranceinVLSISystems,Rome,Italy,2007: 41-49.

[31]ZHUXiaowei,BAUMANNR,PILCHC,et al.Comparisonofproductfailureratetothecomponentsofterrorrateinamuti-coredigitalsignalprocessor[C].IEEE43rdAnnualInternationalReliabilityPhysicsSymposium,NewYork,2005: 209-214.

[32]SIERAWSKIBD,MENDENHALLMH,REEDRA,et al.Muon-inducedsingleeventupsetsindeep-submicrontechnology[J].IEEETrans.OnNuclearScience,2010,57(6):3 273-3 278.

[33]SIERAWSKIBD,REEDRA,MARCUSMH,et al.Effectsofscalingonmuon-Inducedsofterrors[C].IEEE49thAnnualInternationalReliabilityPhysicsSymposium,Monterey,California,USA,2011: 3C.3.1-3C.3.6.

[34]黄海林,唐志敏,许彤.龙芯1号处理器的故障注入方法与软错误敏感性分析[J].计算机研究与发展,2007,43(10):1 820-1 827.

[35]龚锐,陈微,刘芳,等.FT51:一种容软错误高可靠微控制器[J].计算机学报,2007,30(10):1 662-1 673.

[36]CRISTIANC,MIKEB,CHRISW.ErrorInjection-basedstudyofsofterrorpropagationinAMDbulldozermicroprocessormodule[C].ProceedingofInternationalConferenceonDependableSystemsandNetworks,Boston,MA,USA,2012: 1-6.

[37]MUKHERJEESS,WEAVERC,EMERJ,et al.Asystematicmethodologytocomputethearchitecturalvulnerabilityfactorsforahigh-performancemicroprocessor[C].Proc.IEEE/ACMInt’lSymp.onMicroarchitecture(MICRO-36),WestinHortonPlazaSanDiego,CA,2003: 29-40.

[38]LIXiaodong,ADVEVS,BOSEP,et al.Onlineestimationofarchitecturevulnerabilityfactorforsofterrors[C].Proc.ofthe35thInt’lSymponConferenceofComputerArchitecture(ISCA),Beijing,China,2008: 341-352.

[39]SHUBHENDUSM,JOELE,STEVENKR.Thesofterrorproblem:anarchitecturalperspective[C].Proc.ofthe11thInt’lSymp.onHigh-PerformanceComputerArchitecture,SanFrancisco,2005: 243-247.

[40]XUXin,LIMan-lap.Understandingsofterrorpropatationusingefficientvulnerability-drivenfaultinjection[C].ProceedingofInternationalConferenceonDependableSystemsandNetworks,Boston,Massachusetts,USA,2012: 1-12.BENEDETTOJ,MAVISD,et al.Singleeventtransientpulsewidthmeasurementsusingavariabletemporallatchtechnique[J].IEEETrans.onNuclearScience, 2004,51(6): 3 365-3 368.

[2]MESSENGERGC.Collectionofchargeonjunctionnodesfromiontracks[J].IEEETrans.onNuclearScience,1982,29(6): 2 024-2 031.

[3]ALEXANDRESCUD,ANGHELL,NICOLAIDISM.NewmethodsforevaluatingtheimpactofsingleeventtransientsinVDSMICs[C].Proc.ofthe17thIEEEInt.Symp.onDefectandFaultToleranceinVLSISystems,Vancouver,2002: 99-107.

[4]RAJEEVRR,KAVIRAJC,DAVIDTB,et al.Computingthesofterrorrateofacombinationallogiccircuitusingparameterizeddescriptors[J].IEEETrans.onComputer-AidedDesignofIntegratedCircuitsandSystems,2007,26(3):468-479.

[5]ADAMW,SPYROST.Transientpulsepropagationusingtheweibulldistributionfunction[C].IEEEInt’lSymposiumonDefectandFaultToleranceinVLSIandNanotechnologySystems(DFT),Austin,TX,USA,2012: 109-114.

[6]RAMANARAYANANR,DEGALAHALV,VIJAYKRISHNANN,et al.Analysisofsofterrorrateinflip-flopsandscannablelatches[C].IEEEInt.SOCConference,Portland,2003: 231-234.

[7]ZHANGM,SHANBHAGNR.Asofterrorrateanalysis(SERA)methodology[C].Proc.ofInternationalConf.onComputerAidedDesign.Taipei,Taiwan,2004: 111-118.

[8]RAJARAMANR,KIMJS,VIJAYKRISHNANN,et al.SEAT-LA:asofterroranalysistoolforcombinationallogic[C].Proceedingsofthe19thInternationalconferenceonVLSIDesign,Hyderabad,India,2006: 499-502.

[9]HUBERTG,PALAUJ-M,CASTELLANI-COULIEK,et al.Detailedanalysisofsecondaryions’effectforthecalculationofneutron-inducedSERinSRAMs[J].IEEETrans.onNuclearScience,2001,48(6): 1 953-1 959.

[10]HUBERTG,BOUGEROLA,MILLERF,et al.Predictionoftransientinducedbyneutron/protoninCMOScombinationallogiccells[C]. 12thIEEEInt.On-lineTestingSymposium,LakeofComo,Italy,2006:63-74.

[11]XUANX,CHATTERJEEA.Sensitivityandreliabilityevaluationformixed-signalICsunderelectromigrationandhot-carriereffects[C].IEEEInt’lSymp.OnDefectandFaultToleranceinVLSISystems,SanFrancisco,California,2001: 323-328.

[12]RAMAKRISHNANK,RAJARAMANR,SURESHS,et al.VariationimpactonSERofcombinationalcircuits[C].The8thInternationalSymposiumonQualityElectronicDesign(ISQED'07),SanJose,2007: 911-916.

[13]ZHARC,BAIXL,DEYS.Evaluatingtransienterroreffectsindigitalnanometercircuits[J].IEEETrans.onReliability,2007,56(3): 381-391.

[14]REORDAMS,VIOLANTEM.AccurateandefficientanalysisofsingleeventtransientsinVLSIcircuits[C].IEEEInt’lOn-lineTestingSymp.,KosIsland,Greece,2003: 101-105.

[15]ZHANGBin,WANGWeishen,ORSHANSKYM.FASER:fastanalysisofsofterrorsusceptibilityforcell-baseddesigns[C].The7thInt’lSymp.onQualityElectronicDesign(ISQED`06),2006: 1-6.

[16]ZHANGM,SHANBHAGRN.Soft-error-rate-analysis(SERA)methodology[J].IEEETrans.onComputer-aidedDesignofIntegratedCircuitsandSystems,2006,25(10):2 140-2 155.

[17]MOHANRAMK,TOUBANA.Cost-effectiveapproachforreducingsofterrorfailurerateinlogiccircuits[C].InternationalTestConference,2003: 893-901.

[18]ANDREKN,SAMIRJ,GORANJ.Combinationallogicsofterroranalysisandprotection[C].The12thIEEEInt’lOn-lineTestingSymposium,LakeofComo,Italy,2006:99-104.

[19]KIMJS,NICOPOULOSC,VIJAKRISHNANN,et al.Aprobabilisticmodelforsoft-errorrateestimationincombinationallogic[C].Proc.ofthe1stIntWorkshoponProbabilisticAnalysisTechniquesforRealTimeandEmbeddedSystems,Italy,2004: 25-31.

[20]ASADIG,TAHOORIMB.Ananalyticalapproachforsofterrorrateestimationindigitalcircuits[C].IEEEIntSymponCircuitsandSystems,Kobe,2005: 2 991-2 994.

[21]KRISHNASWAMYS,VIAMONTESGF,MARKOVIL,et al.Accuratereliabilityevaluationandenhancementviaprobabilistictransfermatrices[C].ProcoftheDesign,AutomationandTestinEuropeConferenceandExhibition,Orlando,2005: 282-287.

[22]WANGZhen,JIANGJianhui,YANGGuang.Implementationandanalysisofprobabilisticmethodsforgate-levelcircuitreliabilityestimation[J].TsinghuaScienceandTechnology. 2007,12(S1): 32-38.

[23]ABDOLLAHIA.Probabilisticdecisiondiagramsforexactprobabilisticanalysis[C].Proc.Int’lConferenceonComputerAidedDesign,SanJose,CA,2007: 266-272.

[24]王真,江建慧. 基于概率转移矩阵的串行电路可靠度计算方法[J].电子学报,2009,37(2): 241-247.

[25]XIAOJ,JIANGJH,ZHUX,et al.Amethodofgate-levelcircuitreliabilityestimationbasedoniterativePTMmodel[C].IEEE17thPacificRimInternationalSymposiumonDependableComputing,Pasadena,USA,2011:276-277.

[26]HOSSEINA,MEHDIBT.Softerrormodelingandprotectionforsequentialelements[C].The20thIEEEInt'lSymposiumonDefectandFaultToleranceinVLSISystems,Monterey,USA,2005: 463-474.

[27]MOHYUDDINN,PAKBAZNIAE,PEDRAMM.Probabilisticerrorpropagationinlogiccircuitsusingthebooleandifferencecalculus[C]. 26thIEEEInt`lConf.onComputerDesign,LakeTahoe,2008: 7-13.

[28]HANJ,CHENH.Reliabilityevaluationoflogiccircuitsusingprobabilisticgatemodels[J].MicroelectronReliability,2011,51(2): 468-476.

[29]SINGHNSS,HAMIDNH.Evaluationofcircuitreliabilitybasedondistributionofdifferentsignalinputpatterns[C]. 8thIEEEInt`lColloquiumonSignalProcessinganditsApplications,Malacca,2012: 5-9.

[30]HOSSEINA,MEHDIBT.Estimatingerrorpropagationprobabilitieswithboundedvariances[C]. 22ndIEEEInt’lSymp.onDefectandFaultToleranceinVLSISystems,Rome,Italy,2007: 41-49.

[31]ZHUXiaowei,BAUMANNR,PILCHC,et al.Comparisonofproductfailureratetothecomponentsofterrorrateinamuti-coredigitalsignalprocessor[C].IEEE43rdAnnualInternationalReliabilityPhysicsSymposium,NewYork,2005: 209-214.

[32]SIERAWSKIBD,MENDENHALLMH,REEDRA,et al.Muon-inducedsingleeventupsetsindeep-submicrontechnology[J].IEEETrans.OnNuclearScience,2010,57(6):3 273-3 278.

[33]SIERAWSKIBD,REEDRA,MARCUSMH,et al.Effectsofscalingonmuon-Inducedsofterrors[C].IEEE49thAnnualInternationalReliabilityPhysicsSymposium,Monterey,California,USA,2011: 3C.3.1-3C.3.6.

[34]黄海林,唐志敏,许彤.龙芯1号处理器的故障注入方法与软错误敏感性分析[J].计算机研究与发展,2007,43(10):1 820-1 827.

[35]龚锐,陈微,刘芳,等.FT51:一种容软错误高可靠微控制器[J].计算机学报,2007,30(10):1 662-1 673.

[36]CRISTIANC,MIKEB,CHRISW.ErrorInjection-basedstudyofsofterrorpropagationinAMDbulldozermicroprocessormodule[C].ProceedingofInternationalConferenceonDependableSystemsandNetworks,Boston,MA,USA,2012: 1-6.

[37]MUKHERJEESS,WEAVERC,EMERJ,et al.Asystematicmethodologytocomputethearchitecturalvulnerabilityfactorsforahigh-performancemicroprocessor[C].Proc.IEEE/ACMInt’lSymp.onMicroarchitecture(MICRO-36),WestinHortonPlazaSanDiego,CA,2003: 29-40.

[38]LIXiaodong,ADVEVS,BOSEP,et al.Onlineestimationofarchitecturevulnerabilityfactorforsofterrors[C].Proc.ofthe35thInt’lSymponConferenceofComputerArchitecture(ISCA),Beijing,China,2008: 341-352.

[39]SHUBHENDUSM,JOELE,STEVENKR.Thesofterrorproblem:anarchitecturalperspective[C].Proc.ofthe11thInt’lSymp.onHigh-PerformanceComputerArchitecture,SanFrancisco,2005: 243-247.

[40]XUXin,LIMan-lap.Understandingsofterrorpropatationusingefficientvulnerability-drivenfaultinjection[C].ProceedingofInternationalConferenceonDependableSystemsandNetworks,Boston,Massachusetts,USA,2012: 1-12.

(编辑胡小萍)

DOI:10.3969/j.issn.1006-4729.2015.04.014