适用于10 Gbps以太网物理层收发器的变速箱电路设计

黄安君,罗 旸,雷淑岚

(中国电子科技集团公司第58研究所,江苏 无锡 214035)

1 引言

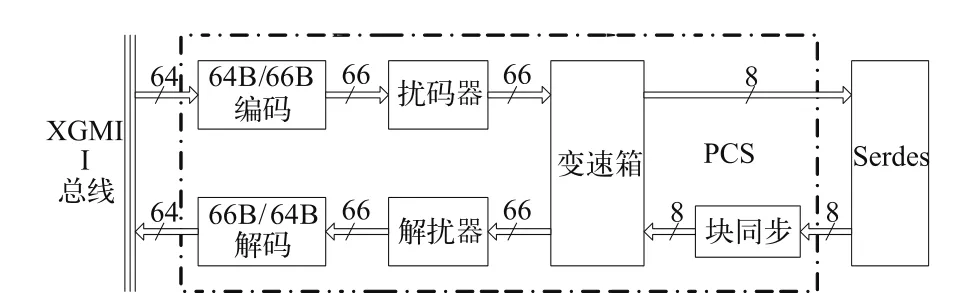

随着串行通讯速率向10 Gbps甚至100 Gbps发展,传统的编解码方式如8 b/10 b编码,由于其效率较低,存在20%的带宽浪费,如在高速系统中继续采用这样的编码方式,将极大地浪费信道的带宽,降低数据的传输效率。因此在高速系统中,更多的使用高效率的编码方式如64 B/66 B, 64 B/67 B[1]。在10G Base-R以太网物理编码层协议中就规定使用64 B/66 B的编码方式[2],如图1所示。

图1 10 Gbps以太网收发器结构

但现在的数字系统总线位宽大多都是1,2,4,8等2的n次方字节,例如在10G Base-R协议中,经过64 B/66 B编码后的数据在发送到Serdes模块之前,一般要进行位宽由多到少的转换,因为在10G Base-R的物理层收发器设计过程中,Serdes的并行端数据输入的位宽数一般不是66位,且一般都不超过20位,如8位、10位、16位等。同样数据从Serdes模块发送到PCS模块时,也需要进行数据位宽由少到多的转变。变速箱电路就是实现任意数据位宽之间的转换,来保证芯片内各模块之间的无缝连接与正常的数据传输功能[3~4]。如果根据变速箱两侧的数据输出和输入的数据率相等的原理,利用两个频率的时钟对数据位宽直接进行转换,而不对两侧时钟或者数据进行任何的控制或者处理,则会出现下面两种情况:

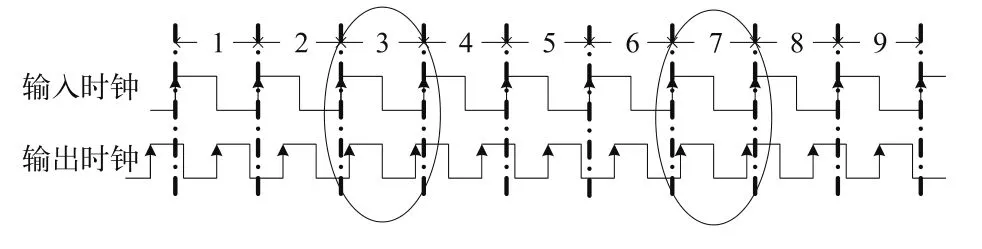

当变速箱数据输出的时钟频率大于变速箱数据输入的时钟频率,即输出数据所用的时钟周期小于输入数据的宽度时,在数据位宽转换过程中,在某个时钟周期下,输出数据的时钟会将当前周期下的数据采样2次,如图2中的第3和第7时钟周期,从而造成输出数据的重复。

图2 同一数据采样2次

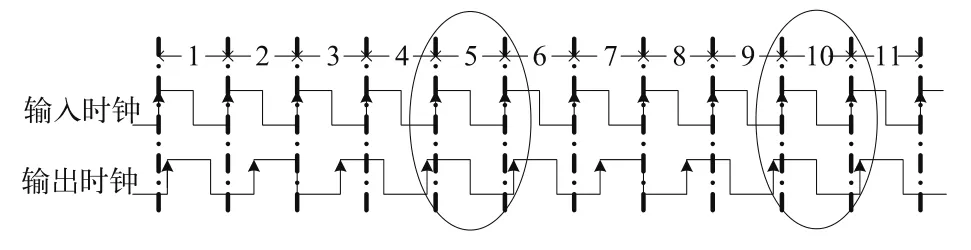

当变速箱数据输出的时钟频率小于变速箱数据输入的时钟频率,即输出数据所用的时钟周期大于输入数据的宽度时,在数据位宽转换过程中,在某个时钟周期下,如图3中的第5和第10个时钟周期,输出数据的时钟会漏采当前周期下的数据,从而影响数据传输的正确性。

图3 数据漏采

针对上述的问题,可以通过借用时钟周期的办法解决:在数据位宽由多向少转变的过程中,通过在某个时钟周期暂停给变速箱输入数据,但不停止变速箱的数据输出;在数据位宽由少向多转变的过程中,通过在某个时钟周期暂停给变速箱输出数据,但不停止变速箱的数据输入。但是这种办法会减少系统数据传输的效率,尤其是在输入数据位宽和输出数据位宽之间差距较大的情况下,系统的整体性能会有极大的下降,只适合FPGA设计,因为FPGA用户可以自己来设计控制逻辑。而在一般的ASIC或者SOC设计中,这种显著降低系统传输效率的方法是不能满足系统要求的[5~6]。本文提出一种新的不均等时钟周期的方法,可以在不改变数据传输速率的基础上,很好地解决上述问题。

2 不均等时钟周期变速箱的设计思路

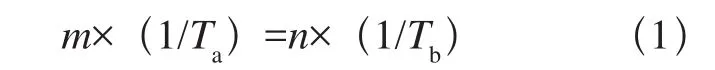

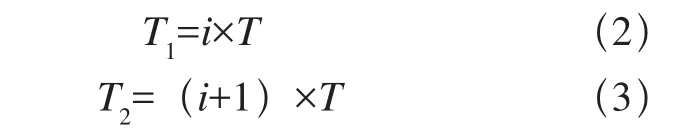

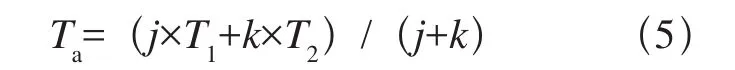

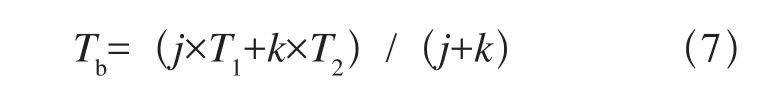

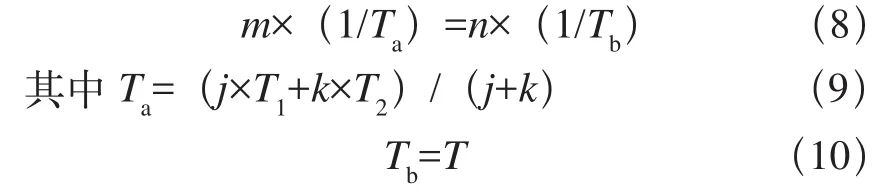

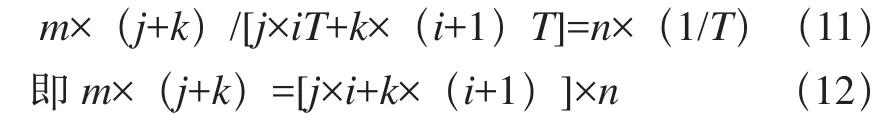

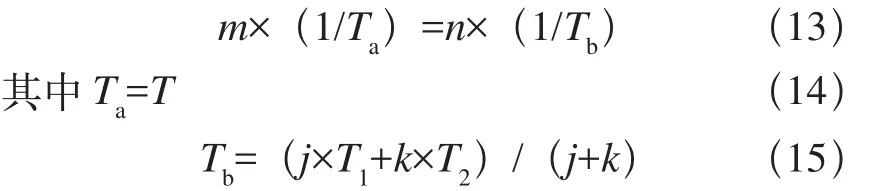

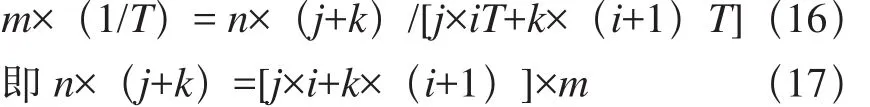

在通信系统中,变速箱电路主要实现不同数据位宽之间的转换,变速箱两端的数据位宽和时钟频率在某一实际电路中是确定值。在本设计中,为了使数据传输效率最大化,变速箱两端的比特率相同,由此可以确定变速箱两端的位宽值和时钟频率之间的比例关系。为方便阐述,定义变速箱输入端时钟周期为Ta,输入端位宽为m,输出端时钟周期为Tb,输出端位宽为n,变速箱两端的比特率相同,则存在:

在实际电路中,输入时钟和输出时钟都是由系统中的固定时钟源产生,时钟源的频率是固定的,变速箱两端的位宽m、n的值根据具体电路的值确定,Ta和Tb的值也要根据m、n的值做相应的调整。电路中的时钟源周期定义为T,用于生成输入时钟和输出时钟。在本设计中,由周期为T的时钟源先产生两个基本的时钟周期分别为T1和T2,其中T1和T2只相差一个时钟源周期:

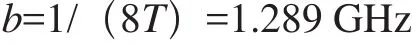

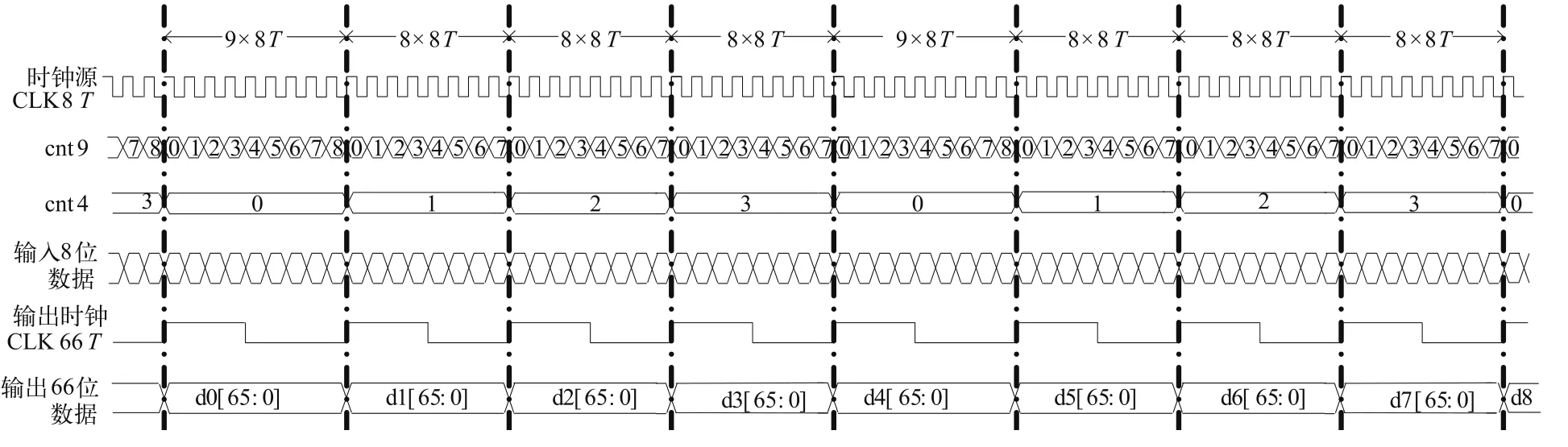

i为正整数;再用T1和T2组成所需要时钟周期Ta或Tb,具体电路中m、n的关系可以定义为m>n和m 当m>n时,输入时钟的周期值Ta大于输出时钟周期Tb,则输出时钟周期Tb=T,输入时钟Ta、T1和T2的关系为: T1和T2组合成输入时钟的周期: j和k为正整数。可以看出此时的输入时钟的每个时钟周期不完全相等,在一定的时钟周期数下,其平均周期为Ta。在每个T1或T2时钟周期都输入m位的数据,在每一个T时钟周期输出n位的数据。当m T1和T2组合成输出时钟的周期: j和k为正整数。可以看出此时输出时钟的每个时钟周期不完全相等,在一定的时钟周期数下,其平均周期为Tb。在每一个T时钟周期输入m位的数据,在每个T1或T2时钟周期都输出n位的数据。 本变速箱设计的特点是在数据转换中,生成不均等的时钟周期的变速箱时钟,在保证传输过程中数据比特率不变的情况下,解决数据的丢失或重复传输的问题。 变速箱数据传输的过程与其时钟生成过程是密切相关的,也需要分成m>n和m 当m>n时,在数据的输入端,每一个T1或T2时钟周期,变速箱的输入端都输入m位的数据;在数据的输出端,在输入时钟周期为T1的时间内,输出i个n位数据,在输入时钟周期为T2的时间内,输出i+1个n位数据,在j+k个时钟周期内,输入端输入了(j+k)×m位的数据,在输出端输出[j×i+k×(i+1)]×n位的数据,由于变速箱两端的比特率相等: 化简可以得到: 则变速箱完成了(j+k)个m位数据到[j×i+k×(i+1)]个n位数据的位宽转变。 以此类推当m 化简可以得到: 则变速箱完成了[j×i+k×(i+1)]个m位数据到(j+k)个n位数据的位宽转变。 接下来具体说明变速箱的实现过程,以10G BASE-R物理层为例,Serdes的位宽要求为8位,PCS采用64 B/66 B的编解码方式,其数据波特率为10.312 5 Gbps,在与Serdes模块进行数据传输过程中,需要通过变速箱模块实现66位到8位或者8位到66位两种位宽的转换。 输入数据的位宽m为66位,输出数据的位宽n为8位。 变速箱的输入数据所用时钟A的频率: 输出数据所用时钟B的频率: 其中,T表示为每一位数据传输的周期,T=0.096 97 ns。 变速箱时钟源的周期定义为8 T,此8 T时钟由Serdes内置的PLL产生,则变速箱输入数据的时钟周期为66 T,变速箱输出数据的时钟周期为8 T。由时钟周期为8 T的时钟源先产生两个基本的时钟单 元:8×8 T 和 9×8 T,并 且 8×8 T<66 T<9×8 T,8×8 T和9×8 T按一定的比例关系组合成66 T的时钟周期,根据 [(64 T)×x+(72 T)×y]/(x+y)=66 T,计算得出x/y=3/1;也就是4个66 T的时钟周期可以重组为 {8×8 T,8×8 T,8×8 T,9×8 T}。在数据位宽转换过程中,输入时钟周期为8×8 T或9×8 T,输出时钟周期都为8 T,数据具体传输过程如图4所示。 在第一个8×8 T输入时钟周期,变速箱输入66位数据,变速箱输出端移位8次,输出8个8位的数据,保留2个位的数据在缓冲器的低位。在第二个8×8 T输入时钟周期,变速箱输入66位数据作为缓冲器高位,变速箱输出端移位8次,输出8个8位的数据,保留4个位的数据在缓冲器的低位;在第三个8×8 T输入时钟周期,变速箱输入66位数据作为缓冲器高位,变速箱输出端移位8次,输出8个8位的数据,保留6个位的数据在缓冲器的低位。在第一个9×8 T输入时钟周期,变速箱输入66位数据作为缓冲器高位,变速箱输出端移位9次,输出8个8位的数据,缓冲器中没有保留的数据,完成4个66位数据向33个8位数据位宽转变过程。 图4 66位位宽向8位位宽转换 输入数据的位宽m为8位,输出数据的位宽n为66位。变速箱的输入数据所用时钟A的频率a=1/(8 T)= 1.289 GHz,输出数据所用时钟B的频率b=1/(66 T)=156.25 MHz,其中T表示为每一位数据传输的周期,T=0.096 97 ns。变速箱时钟源的周期定义为8 T,此8 T时钟由Serdes内置的PLL产生,则变速箱输入数据的时钟周期为8 T,变速箱输出数据的时钟周期为66 T。 如上所述,66 T的时钟周期可以重组为{9×8 T,8×8 T,8×8 T,8×8 T}。在数据位宽转换过程中,输入时钟周期都为8 T,输出时钟周期为8×8 T或9×8 T,数据具体传输过程如图5所示。在第一个9×8 T输入时钟周期,变速箱输入9个8位数据进缓冲器,变速箱输出缓冲器的低66位作为输出数据,保留6个位的数据在缓冲器的低位。在第一个8×8 T输入时钟周期,变速箱输入8个8位数据作为缓冲器高位,变速箱输出缓冲器的低66位作为输出数据,保留4个位的数据在缓冲器的低位。在第二个8×8 T输入时钟周期,变速箱输入8个8位数据作为缓冲器高位,变速箱输出缓冲器的低66位作为输出数据,保留2个位的数据在缓冲器的低位。在第三个8×8 T输入时钟周期,变速箱输入8个8位数据作为缓冲器高位,变速箱输出缓冲器的低66位作为输出数据,缓冲器中没有保留的数据,完成33个8位数据向4个66位数据位宽转变过程。 图5 8位位宽向66位位宽转换 使用verilog HDL语言对上述变速箱的功能进行描述,搭建验证平台,并使用VCS软件进行仿真,仿真示意图如图6所示。 图6 验证平台示意图 仿真结构图如图6所示,pattern_gen模块产生66位的数据,gearbox_1和gearbox_2是例化本变速箱模块,其中变速箱gearbox_1模块的输入数据位宽为66位,输出数据位宽为8位,变速箱gearbox_2模块的输入数据位宽为8位,输出数据位宽为66位,在pattern_chk模块中把pattern_gen模块产生66位数据延时几个时钟周期后和该数据经过变速箱位宽转变后的66位数据相比较。仿真的波形如图7所示,仿真分为两部分:数据宽度66位到8位的转换和8位到66位的转换。 clk8t是固定的时钟源,其周期为0.776 ns,在每一个clk8t时钟周期下传输8位的数据。clk66_out1是66位转变为8位位宽组合后的输入时钟,其平均时钟周期为6.402 ns,是由一个6.984 ns(9个clk8t时钟周期)和3个6.208 ns(8个clk8t时钟周期)组合而成。在gearbox_1中,在每个6.208 ns时钟周期下,输入66位的数据,输出8个8位数据。在每个6.984 ns时钟周期下,输入66位的数据,输出9个8位数据。gearbox_1中输出的8 位数据作为gearbox_2中输入,clk66_out2是8位转变为66位位宽组合后的输出时钟,其平均时钟周期也为6.402 ns,同样是由一个6.984 ns(9个clk8t时钟周期)和3个6.208 ns(8个clk8t时钟周期)组合而成。在gearbox_2中,在9个clk_8t时钟周期下,输入9个8位数据,在clk66_out2的每个6.984 ns时钟周期下输出66位的数据,在8个clk_8t时钟周期下,输入8个8位数据,在clk66_out2的每个6.208 ns时钟周期下输出66位的数据。 把gearbox_1的66位输入数据延时4个clk66_out1时钟周期后和gearbox_2的66位输出数据一一比较,result信号为高电平,表明这两个数据完全相同,说明变速箱在66位位宽转变为8位位宽,再由8位位宽转变为66位位宽过程正确,没有丢失或重复采样。 图7 仿真波形图 在变速箱电路中,通过固定时钟源产生的不均等时钟周期的变速箱输入输出时钟,可以保持变速箱两边的数据传输速率不变,并且保证在传输过程中没有数据的丢失或重复采样,可以用于高速的串行通信系统中。 [1] Zhou Qinglun, Li Chunyan, Wang Yong. Hardware Implementation of 64 B/66 B Encoder/Decoder for 10-Gigabit Ethernet [Z]. [2] IEEE Std 802.3ae-2002 [S/OL]. New Jersey: IEEE, 2002[2002-8-30]. http://standards.ieee.org. [3] S Sidiropoulos, N Acharya, P Chau, J Dao, A Feldman, H J Liaw, M Loinaz, R S Narayanaswami, C Portmann, S Rabii, A Salleh, S Sheth, L Thon, K Vleugels, P Yue, D Stark. An 800 mW 10 Gb ethernet transceiver in 0.13 μm CMOS [A]. in IEEE ISSCC Dig. Tech.Papers, 2004. 168-169. [4] H R Lee, M S Hwang, B J Lee, Y D Kim, D Oh, J Kim, S H Lee, D K Jeong, W Kim. A fully integrated 0.13 μm CMOS 10 Gb Ethernet transceiver with XAUI interface[A]. in IEEE ISSCC Dig. Tech. Papers, 2004. 170-171. [5] Virtex-II Pro Platform FPGA User Guide [EB/OL]. San Jose: Xilinx, 2005[2005-3-23]. http://www.xilinx.com. [6] Yongsam Moon, Member, IEEE, Sang-Hyun Lee, Daeyun Shim. A Divide-by-16.5 Circuit for 10-Gb Ethernet Transceiver in 0.13 μm CMOS [Z]. 1175-1179.

3 不均等时钟周期变速箱的实现

3.1 数据位宽由多向少转变

3.2 数据位宽由少向多转变

4 变速箱的仿真与性能分析

5 小结