一种新的DTI位同步方法与FPGA实现

胡玉霞,杨志刚,胡 墩

(1.黄山学院 信息工程学院,安徽 黄山245041;2.烽火通信科技股份有限公司 技术部,湖北 武汉430070)

1 前 言

DOCSIS (Data-Over-Cable Sevice Interface Specifications) 有线电缆数据服务接口规范是由有线电缆标准组织CableLabs制定的国际标准,定义了在有线电缆上提供数据服务所需的通信和运营支撑的接口。DTI (DOCSIS Timing Interface) 又称DOCSIS定时接口,是ITU-T J.211标准中规定了一种新型的定时接口,主要应用于有线电缆网络,通过协议交互方式,在一根电缆线上同时实现频率和时间同步[1]。

作为数字通信网的基础支撑技术,时钟同步技术的发展受到通信网技术发展的影响。随着通信新业务和新技术的不断发展,对同步技术性能要求越来越高。相对于成熟的频率同步技术,以P2P技术为代表的时间同步技术获得了快速发展。目前,新兴的时间同步与现有的频率同步彼此相对独立,但从长远来看,频率同步与时间同步的统一是发展的必然趋势。

FPGA[2,3]由于其可并行运算,体系结构和逻辑单元灵活,集成度高,适应范围宽,计算速度快等特点,受到广大硬件工程师的欢迎。针对当前DTI技术中使用的闭环相位调整位同步方法同步建立时间较长的缺点,提出一种新的开环位同步方法。该方法能够解决在位同步失步的情况下,同步建立时间和调整精度相互制约的难题。借助FPGA开发平台,给出了新的开环位同步FPGA 设计方法,并在ISE10.1平台上进行了实现。使用软件对新的位同步方法的性能进行了测试,结果证明开环位同步方法能够准确提取输入datain的同步时钟,实现精确的位同步。

2 DTI位同步方法

位同步是指在接收端的基带信号中提取码元定时的过程,是正确取样判决的基础。在实现位同步时,可分为外同步法和自同步法两种。在外同步法中,接收端的同步信号事先由发送端送来,而不是自己产生也不是从信号中提取出来。自同步法是指能从数据信号波形中提取同步信号的方法。DTI通信的码元调制采用Manchester码方式。Manchester码是一种典型使用自同步法保持位同步的线路码型[4]。

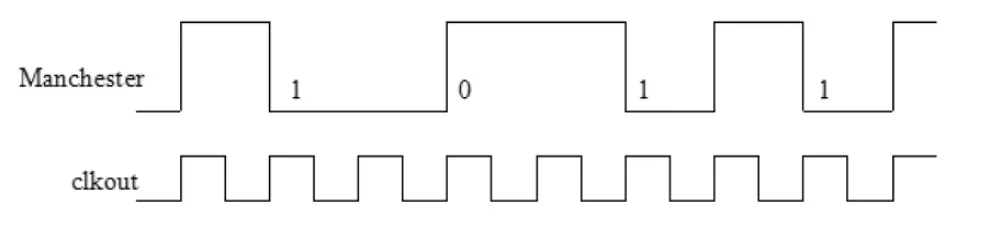

在Manchester码中,每一位的中间有一跳变,位中间的跳变既作时钟信号,又作数据信号;从高到低跳变表示“1”,从低到高跳变表示“0”。Manchester码解决了传输数据没有时钟的问题,Manchester码流与Manchester码流中的同步时钟时序,如图1所示。

图1 Manchester码与同步时钟的时序

图1中,Manchester是输入的Manchester 码流,clkout 是从Manchester 码流中恢复得到的同步时钟。使用clkout同步时钟的下降沿就可以正确读取Manchester码元信息,为下一步的解码提供必要条件。

目前,在CPLD/FPGA上常用的位同步方法采用锁相环的闭环相位调整方法,该方法主要由采样鉴相器,数字环路滤波器,数控振荡器3部分组成,闭环相位调整的位同步方法工作原理如图3所示。

图2 闭环相位调整的位同步方法工作原理

在图2中,输入datain与数控振动器里的输出时钟clkout通过采样鉴相器产生超前脉冲up或滞后脉冲down,up和down脉冲通过数字环路滤波器产生相位校正序列co和bo。数控振荡器根据co和bo信号不断调整输出clkout时钟的相位,直到clkout与datain的相位一致,即clkout环路锁定。clkout环路锁定时,鉴相器无up和down脉冲输出,输出时钟clkout为输入datain的同步时钟。

3 新的DTI位同步方法

闭环相位调整的位同步方法需要高频时钟以保证精度,一旦失步,就需要通过反馈回路重新调整。每一个超前和滞后脉冲仅能调整一步,使其同步建立时间和调整精度变得相互制约;如果接收码元出现连“0”或是连“1”的情况,锁定时间会很长。

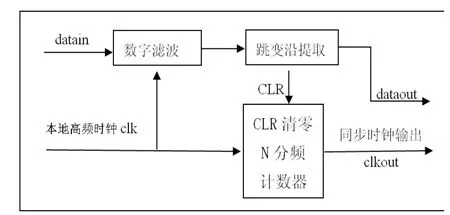

由于闭环相位调整的位同步方法存在同步建立时间较长的缺点,提出了一种新型的开环位同步方法。开环位同步方法原理如图3所示。

开环位同步方法实现位同步的基本原理是利用输入码元datain的CLR(跳变沿)信号控制N分频计数器,由N分频计数器产生同步时钟clkout。N分频计数器实现对本地高频时钟clk的N分频,控制同步时钟clkout输出的频率;通过CLR信号对计数器的清零调整同步时钟clkout输出的相位。

图3 开环位同步方法原理图

3.1 数字滤波模块的FPGA实现

数字滤波模块的作用是通过本地高频时钟将输入码元中的窄脉冲干扰滤除掉,这样有效的避免线路传输中产生的毛刺对输入的跳变沿提取造成干扰。这部分电路在FPGA设计中使用一个移位寄存器产生,输入码元被送入移位寄存器并缓存,通过移位寄存器的值产生输出。datain通过数字滤波模块后会产生一个固定的相移,再通过跳变沿提取电路后输出到dataout。dataout与datain存在一定的相移,datain、dataout和clkout的相位如图4所示。

图4 datain、dataout和clkout的相位

同步时钟clkout根据dataout产生,与dataout相位一致,clkout的下降沿能够准确读取dataout的码元信息,从而实现位同步。

3.2 跳变沿提取模块的FPGA实现

跳变沿提取模块的作用是通过提取输入信号的跳变信息产生CLR信号,获得输入信号的真实相位。用这个CLR信号控制分频计数器,就能控制输出时钟clkout的相位,实现输出时钟与输入信号同步。跳变沿提取模块的时序如图5所示。本地高频时钟clk通过提取输入datain的跳变信息产生CLR信号。

图5 跳变沿提取模块的时序

3.3 N分频计数器模块的FPGA实现

N分频计数器模块主要实现同步时钟clkout的输出,由本地高频时钟clk控制计数,CLR信号产生清零。计数器为N进制的自增加循环计数器,计算值为:0→1→…→N-1→0→1→…。clk的下降沿计数器计数,当没有CLR信号输入时,计数器的值自加1;有CLR信号时,计数器的值被置0。clk的上升沿读数并分频输出clkout,计数器的值为N-1时,clkout输出为高,计数值为N/2-1时,clkout输出为低。通过计数器值对clkout输出的控制,产生一个跟输入码元宽度对应且占空比为50%的时钟信号,即实现对输入码元的同步时钟恢复,恢复出的同步时钟为clkout。

4 仿真测试分析

对新的DTI开环位同步方法进行性能仿真测试分析,分为两个部分进行:(1) 位同步功能仿真分析;(2)DTI服务器信号接收和发送测试。

4.1 位同步的仿真分析

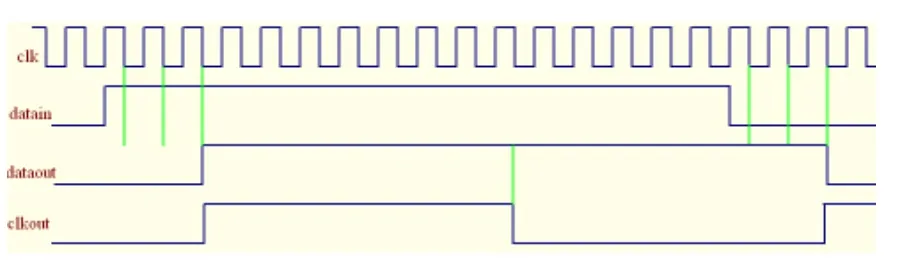

使用ISE10.1仿真工具ISE Simulater,对新的DTI位同步方法的功能进行仿真,功能仿真结果如图6所示。

图6 位同步模块在ISE Simulater上的功能仿真

从图6中可以看到,dataout与clkout的相位保持一致,证明开环位同步方法能够准确提取输入datain的同步时钟,实现精确的位同步。

4.2 DTI服务器信号接收与发送测试

DTI服务器信号接收与发送测试,能够验证位同步模块能否正常工作。利用ISE10.1中的ChipScope Pro工具,通过搭建模拟client端的测试环境,完成对DTI服务器信号接收与发送测试。ChipScope Pro Analyzer上的位同步波形如图7所示。

图7 ChipScope Pro Analyzer上的位同步波形

图7中,信号tx_rx_data是客户端返还给服务器的数据波形,clk_tx是服务器位同步电路产生的同步时钟。从图中可以看出,位同步电路恢复出的同步时钟与输入的数据波形相位一致,通过同步时钟的下降沿能够准确读取输入数据信息。

5 结束语

本文提出一种新的DTI开环位同步方法,该方法能够解决在位同步失步的情况下同步建立时间和调整精度相互制约的问题。通过FPGA平台对新方法进行了实现,使用软件对新方法的性能进行了仿真测试分析,结果表明新的DTI位同步方法能够实现位同步,具有较好的可行性,为开发性能可靠的DTI服务器提供了理论方法和实践基础。

[1]王沁,龙萍,等.基于DOCSIS规范的测距机制分析与嵌入式实现[J].通信学报,2006,32(9):96-101.

[2]杨海钢,孙嘉斌,等.FPGA器件设计技术发展综述[J].电子与信息学报,2010,32(3):714-727.

[3]俞吉波,孔雪.FPGA实际可用性评估与发展趋势分析[J].计算机工程,2011,37(13):282-284.

[4]Forster.R.Manchester encoding:opposing definitions resolved[J].Engineering Science and Education Journal.2000,9(6):278-280.