电子工业用锡及锡基合金电镀技术:现状及展望

贺岩峰,鲁统娟,王芳(长春工业大学化工学院,吉林 长春 130012)

【综述】

电子工业用锡及锡基合金电镀技术:现状及展望

贺岩峰*,鲁统娟,王芳

(长春工业大学化工学院,吉林 长春 130012)

概述了电子工业用锡及锡基合金(如锡-银、锡-铜和锡-铋)电子电镀技术的发展现状,重点探讨了了相关电镀工艺、镀层锡晶须生长问题和锡及锡合金电镀在先进封装中的应用现状,最后展望了电子工业用锡及锡合金电镀未来的发展趋势。

锡;锡合金;电镀;晶须;封装;电子工业

First-author’s address: School of Chemical Engineering, Changchun University of Technology, Changchun 130012, China

由于锡具有良好的可焊性、延展性、导电性及导热性,并具有较低的熔点和良好的耐蚀性,因此锡及锡合金作为可焊性及防护性镀层已经被广泛应用于电子行业中。锡及锡基合金的电镀已经成为电子电镀的重要组成部分,在电子电镀中占有重要的地位。

随着欧盟相关法规(RoHS和WEEE)的提出及实施,近十几年来各种无铅化锡及锡基合金电镀技术得到了广泛的研究和应用。经过长期的应用实践,工业上已经形成了较为成熟的生产工艺和较为完善的性能评价体系。锡及锡基合金的电镀技术也有了长足的进步,涌现了许多新方法、新产品和新工艺,一些新问题也相应地出现。镀锡及锡基合金技术就是在不断解决各种问题的过程中走过了这十几年,并不断地得到发展。

1 镀锡及锡基合金技术的发展现状

1.1纯锡电镀

纯锡电镀是各种无铅镀层中研究和应用最早的电镀工艺。欧盟的RoHS指令(关于在电子电器设备中限制使用某些有害物质的指令)于2002年10月11日批准,2003年2月13日正式发布,规定指令的实施日期是2006年7月1日。但是由于相关报道早已出现,无铅化在2002年就已经开始进入实质性的研究阶段。在2002年,国内已经有企业开始试验及试用无铅纯锡电镀产品。纯锡电镀在电子电镀中的应用及发展主要是在2003年至2006年间。这期间正值国内微电子行业大发展,新建可焊性电镀生产线基本全部采用了无铅纯锡电镀。电子行业从最初的迟疑、徘徊到最后认同、接受了无铅化纯锡电镀产品。经过多年的研究和推广,现在无铅纯锡电镀不但得到了国内企业的普遍认同和广泛应用,也逐步为欧美、日本等国家所接受。

但纯锡电镀中依然存在着一些问题[1]:

(1) 锡晶须问题。纯锡电镀中最大的问题依然是锡晶须,由于锡晶须的存在,纯锡电镀主要是应用于集成电路(IC)及器件的引脚电镀(通常用于引线间距大于0.5 mm的场合)。十几年持续的、大规模的纯锡电镀应用表明,如果使用得当,锡晶须是可以控制在可接受水平的。

(2) 变色性问题,包括储存变色和回流焊变色。尽管经过十余年的发展,变色性问题已经可以通过工艺、添加剂及后处理得到控制和解决,但这仍然是电镀纯锡工艺中最频繁出现的问题之一。

(3) 镀液浑浊问题。目前镀锡溶液的抗氧化技术已经取得长足的进步,镀液的稳定性已经得到很大改善,但镀液的浑浊问题依然存在,也时有发生。

此外,还有焊接温度较高(回流焊峰值温度通常为 260 °C)及存在着其他可靠性问题(例如 Cu/Sn界面的Cu6Sn5层可能出现微孔,焊点可能出现空洞等)。

目前,工业上广泛采用的纯锡电镀有多个品种:镀层方面有哑光和光亮,镀液分为甲基磺酸体系和硫酸体系。对于普通的信号型和功率型元件(例如小外形晶体管封装 SOT、小外形封装SOP、四边引线扁平封装 QFP等)引脚,通常采用甲基磺酸哑光电镀,少数采用硫酸哑光电镀。对于引脚间距较大的器件(例如晶体管外形封装TO等)的引脚,通常采用硫酸光亮电镀或甲基磺酸光亮电镀。

1.2Sn-Ag电镀

由于锡和银的标准电极电位相差很大[φθ(Sn2+/Sn)= -0.137 5 V,φθ(Ag+/Ag)= 0.799 1 V][2],因此需要在电镀液中引入适宜的配位剂(旧称络合剂),使锡和银的沉积电位靠拢才能使二者实现共沉积。在Sn-Ag电镀液中银的配位剂是关键组分,若配位剂对银的配位能力不足,则镀液不稳定,银易形成沉淀或在阳极上析出。因此选择配位剂的重点是选择合适的银配位剂,使银的沉积电位负移。同时该配位剂必须只能选择性地对银起作用,对锡却无作用或作用很小。

虽然无氰化的银配位剂很多,但在酸性介质中其配位作用都会变弱。过去有采用大量KI配位Ag+的焦磷酸盐镀液以及以硫脲为配位剂的镀液。由于配位能力不足,常需要在弱酸性条件(pH 4 ~ 6)下工作。但在弱酸性条件下镀液的导电性差,所以只能在较低电流密度下工作,沉积速率低。现在工业上的Sn-Ag电镀工艺通常采用甲基磺酸体系,并采用甲基磺酸浓度较高的强酸性镀液,所用的银配位剂通常是硫醇化合物及二硫化物。

Sn-Ag合金的共晶组成为Sn-3.5%(质量分数,下同)Ag,共晶温度为221 °C,比纯锡的熔点(232 °C)稍低。合金中存在富Sn相和Ag3Sn金属间化合物相,结晶颗粒细小,曾被认为是性能最好、最有希望替代Sn-Pb的镀层。Sn-Ag合金具有机械强度高、电迁移较低等优点,但其成本较高。工业上通常将镀层银含量控制在2.5%,以便降低成本。目前,Sn-Ag合金镀层被大量应用于凸点电镀及相关的先进封装领域。

1.3Sn-Cu电镀

锡与铜也有较大的电极电位差[φθ(Cu2+/Cu)= 0.340 V]。Sn-Cu合金的共晶组成为Sn-0.7%Cu,即共晶组成中铜含量很低。要使镀层达到共晶组成,镀液中铜离子的浓度需要控制得很低(例如Cu2+含量为0.1 ~ 0.3 g/L),难以操作。所以,现在的Sn-Cu电镀工艺多把镀层中铜含量控制在1.5% ~ 2.0%之间。电镀时通常不能使用Sn-Cu合金作为阳极,因为Sn-Cu合金中铜是以金属间化合物(Cu6Sn5相)的形式存在,而金属间化合物在镀液中的溶解难以控制。所以电镀Sn-Cu合金通常采用纯锡阳极。镀液中的铜离子只能通过添加铜盐进行补充,这不但加大了控制镀液组分的难度,也提高了电镀成本。

Sn-Cu合金中主要是形成Sn和Cu6Sn5的共晶相,即Cu以Cu6Sn5金属间化合物的形式分散在Sn相中。金属间化合物的存在,导致Sn-Cu合金镀层的机械强度较差。此外,镀层的电迁移性能较差,但延展性好、结合强度较大。Sn-Cu合金具有良好的可焊性及与无铅焊料的相容性,制造成本也较低。Sn-0.7%Cu的共晶温度为227 °C,比Sn-Ag合金高,但比纯锡低。而且,Sn-Cu合金镀层的铜含量在一定范围内变化对其熔融温度的影响不大。

在无铅化的初期,Sn-Cu电镀在日本受到重视,获得了较多的研究和应用。Sn-Cu合金一直是争议较大的无铅镀层,有人认为其优点多,是较为理想的无铅化镀层。也有人认为Sn-Cu合金不适合作为无铅化镀层。尤其是有关Sn-Cu合金对锡晶须的影响,至今仍有争议。A.Dimitrovska等[3]认为把铜引入到锡中有利于提高锡镀层抑制锡晶须的能力,A.Baated等[4]则给出相反的证据证明Sn-Cu合金会加剧锡晶须的形成。

1.4Sn-Bi电镀

Sn-Bi合金是一种较早被研究的可焊性电镀技术。与Sn-Ag及Sn-Cu电镀相比,Sn与Bi的电极电位差最小,为。Sn-Bi电镀通常也在强酸性溶液中进行,可使用硫酸盐镀液或甲基磺酸盐镀液。由于铋盐在硫酸溶液中的溶解度小,因此镀液中铋的含量较高(例如超过 10%)时就不能用硫酸型镀液。现在Sn-Bi电镀通常在甲基磺酸溶液中进行。

Sn-Bi合金的共晶组成为Sn-58%Bi,其中铋的含量较高,这一点类似于Sn-Pb合金(共晶组成为Sn-37%Pb)。Sn-Bi共晶合金镀层具有非常显著的优点,如非常低的熔融温度(138 °C)、低的热膨胀系数(CTE,15 × 10-6K-1),尤其是其具有非常出色的抑制锡晶须的能力。这种低熔点的可焊性镀层非常适用于温度敏感的电子器件,所以可用于低温封装。但Sn-Bi合金的缺点也非常明显,Sn-Bi合金的脆性大,容易开裂,这降低了焊点的可靠性。

近年来发现,少量甚至微量的铋加入到锡镀层中就能够有效抑制锡晶须[5]。因此在Sn-Bi合金电镀中,常将镀层铋含量控制在1.5% ~ 3.0%之间。但随着镀层中铋含量降低,镀层的熔融温度会升高,例如铋含量为2%时,合金镀层的熔融温度升高到223 ~ 231 °C范围内。

2 锡晶须问题的研究进展

2.1影响锡晶须生长的因素

2.1.1镀层的微结构

通过采用聚焦离子束(FIB)研究镀层断面的结晶结构发现,晶粒的形貌是影响锡晶须的一个关键因素[6-7]。当镀层中结晶颗粒为柱状结构时(如纯锡镀层),金属间化合物会沿着晶粒边界增长而产生应力,因为存在着垂直方向的应力释放通路,当发生垂直方向的应力释放时就产生了锡晶须。所以柱状的结晶结构会促进锡晶须的生长。但晶粒为等轴状时,不存在这样的应力释放通路,在整个镀层中应力是均匀分布的,不存在应力集中现象,所以不易产生锡晶须。通过形成合金可使纯锡镀层的结晶结构由柱状转变为等轴状,所以合金化是解决锡晶须问题的重要方法之一[3]。

2.1.2镀层中的杂质

镀层中的杂质主要来自电镀过程的夹杂,通常与碳含量有关。在电沉积层中,杂质通常聚集于晶粒的边界处,由于锡晶须是通过晶界生长的,这些杂质的存在会加剧锡沉积层中锡晶须的形成[8]。实验数据表明[9],将2种相近厚度的镀层放置在50 °C环境下4个月,其中含碳量为0.2%的镀层中锡晶须长度为235 μm,而含碳量为0.05%的镀层中锡晶须的长度只有12 μm。

2.1.3基体材料

基体材料对锡晶须的形成有很大影响。各种基材按生成锡晶须的倾向由大到小的顺序为:黄铜、C151、C194、C7025、纯铜、FeNi42合金、Ni。但在工业生产中,对镀纯锡的FeNi42框架进行热冲击试验(TCT试验)和高温高湿试验(温度55 °C,相对湿度85%)之类的热试验时,却经常发现有大量锡须产生,不能通过锡晶须的试验考核。其原因主要是纯锡镀层与基材的热膨胀系数存在差别。纯锡的热膨胀系数为23 × 10-6K-1,而FeNi42的热膨胀系数为4.3 × 10-6K-1,二者的热膨胀系数差别非常大,因此受热时纯锡镀层中会产生额外的热应力,从而引发了锡晶须的生成。对FeNi42合金基材表面的Sn-10%Pb合金镀层进行热试验时也同样会产生锡晶须。

但是据报道[10],图形化阵列结构的镀锡层由于把锡镀层划分成小颗粒,因此即使在黄铜基体上也具有极低的生成锡晶须倾向。

2.2锡晶须的评估及考核方法

目前工业上通常采用JEDEC固态技术协会标准JESD201A-2008(锡和锡合金表面涂层的锡晶须灵敏度环境验收要求)和JESD22A121A-2008(锡和锡合金表面涂层锡晶须的试验方法)对锡晶须进行评估和考核。

JESD22A121A标准采用3种考核条件:(1)温度循环(-55或-40至85 °C);(2)室温存放(温度30 °C,相对湿度60%);(3)高温高湿(温度55 °C,相对湿度85%)。

JESD201A标准给出了验收准则,按对锡晶须的要求分成4个类别。

(1) 类别 1A--要求最低,主要用于产品寿命较短的消费类电子产品,对锡晶须关注度低。验收标准:温度循环1 000次及高温高湿1 000 h,锡晶须长度40 μm;室温存放1 000 h,锡晶须长度20 μm。

(2) 类别 1--具有中等产品寿命的工业及消费类电子产品,对锡晶须有中等的关注水平。验收标准:温度循环1 500次、高温高湿4 000 h及室温存放4 000 h,锡晶须长度67 μm(引脚类器件)或50 μm(高频器件)。

(3) 类别 2--商业关键应用性产品,如电信基础设施、高档电器、汽车电子等。这些产品具有长的产品寿命,对锡晶须关注度高。验收标准:温度循环1 500次,锡晶须长度45 μm;高温高湿4 000 h及室温存放4 000 h,锡晶须长度40 μm。

(4) 类别3--军事、航空航天及医学应用等。此类别不允许使用纯锡或高锡镀层。

2.3锡晶须的控制

2.3.1镀层的热处理

目前工业上通用的方法是镀后将镀层置于150 °C下烘烤1 h。目前已经证实,这种高温处理方法的作用主要是在锡镀层和铜基体的界面处生长出一层厚度均匀的金属间化合物。由于金属间化合物层均匀分布,不会产生不均匀的应力分布,因此就不易生成锡晶须。但这要消耗一定厚度的锡层,使锡层减薄,所以锡镀层应保持一定的厚度。

2.3.2电镀过程

电镀过程的控制决定了镀层的质量和性能,需要控制的参数主要有镀层厚度(>8 μm)、晶粒尺寸(1 ~ 8 μm)、杂质含量(碳的质量分数小于 0.05%)、表面形貌等。维护好镀液,保持镀液澄清,经常进行清缸及镀液部分更新,避免杂质积累。

3 镀锡及锡基合金在先进封装中的应用

3.1凸点电镀

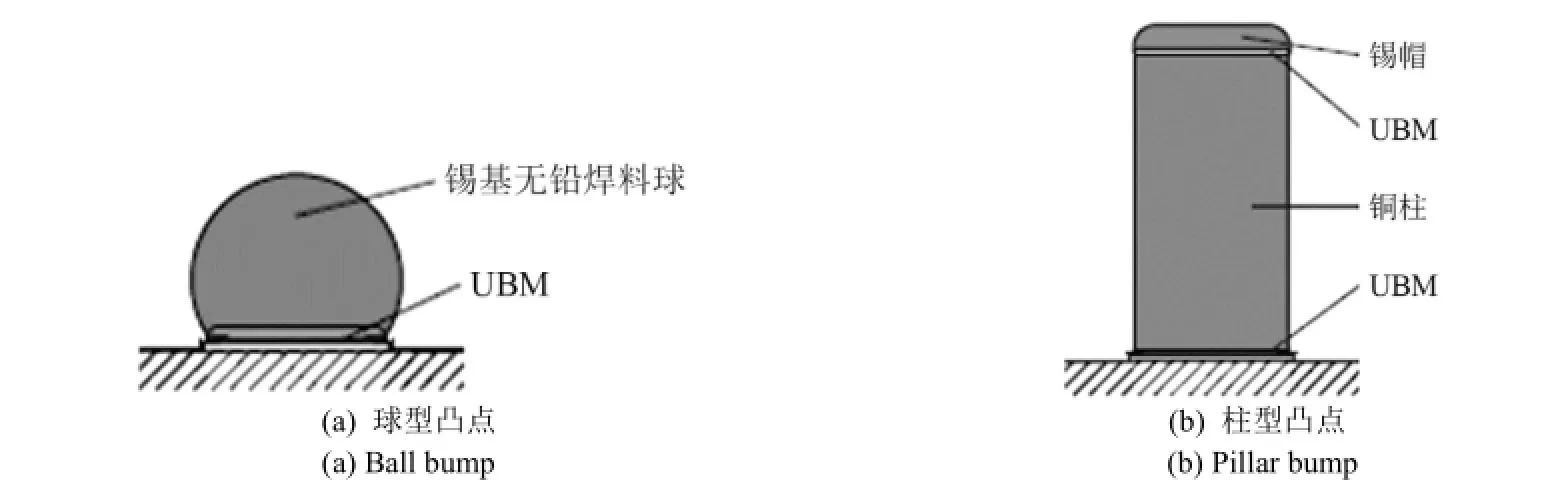

电镀锡及锡基合金已被广泛应用于各种先进封装中凸点的制作。目前主要有两种形式的凸点,即球型凸点(ball bump)和柱型凸点(pillar bump),如图1所示。

图1 不同类型凸点的示意图Figure 1 Schematic diagrams of different kinds of bumps

球型凸点的基本制作过程是:先在芯片表面制作 UBM(凸点下金属,under-bump metal)层,然后用光刻胶做出图案(孔),通过电镀在孔中沉积锡或锡基合金,再去除光刻胶,最后回流使柱型的焊料变成球型。柱型凸点的制作是先镀出铜柱(Cu pillar),然后在铜柱顶端镀一层锡或锡基合金(锡帽,solder cap)进行封顶。通常铜柱下的UBM用Cu/Ti,上层锡帽下的UBM为Ni。凸点类型的确定一般要考虑芯片形式、尺寸、厚度和互连密度等因素。

锡基无铅焊料通常采用镀纯锡、Sn-Ag合金及Sn-Cu合金等制作,其中Sn-Ag合金用得最多。电镀锡及锡基合金在这两种类型凸点的制作中都起着关键作用。

3.2微凸点

随着互连密度的不断提高,凸点的尺寸不断缩小,许多凸点的尺寸可能小至直径为50 μm或更小,可称为微凸点。

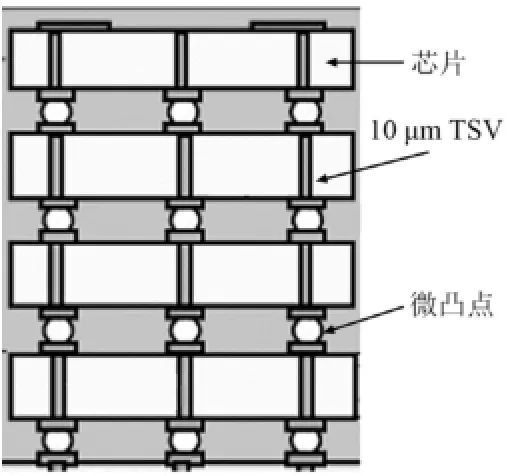

微凸点的典型应用是在芯片与芯片之间的互连上。在TSV(硅通孔)等3D封装中需要涉及多层芯片的叠层互连,即将分立的芯片键合成为一体。结合TSV及层间键合可以实现不同芯片的垂直互连,构建3D封装系统。其中的键合方法主要有氧化物键合和微凸点键合。采用金属/焊料微凸点的键合方式时,键合点既作为结构支撑及连接结构,又起着电气互连的作用,易于实现高可靠性低温互连。所以,微凸点型键合得到了广泛应用。采用微凸点键合TSV叠层的封装结构如图2所示。

图2 采用焊料微凸点键合的TSV叠层封装结构Figure 2 Construction of a typical stacked-chip with TSV and solder micro-bumps

微凸点可以通过丝网印刷、植球、C4NP(焊料转移)及电镀等方法制作。但随着封装密度的不断提高,其他方法通常不能满足对小尺寸、高密度凸点制作的要求,制作成本会急剧上升。而用电镀法则可以制作小尺寸、高密度的微凸点,并且具有易于批量生产,凸点形状和尺寸易于精确控制的优点,所以电镀法制作微凸点具有很好的应用前景。

4 展望

4.1微孔镀锡

随着微电子技术的不断发展,锡及锡基合金在先进封装中的应用将会不断扩展。其重要应用之一就是在集成电路、MEMS(微机电系统)和 LED(发光二极管)等领域中凸点和微凸点的制作。为了应对封装密度的不断提高,凸点及微凸点的尺寸和间距不断减小,从直径200 μm、间距500 μm的BGA(球栅阵列)封装发展到现在的直径为20 ~ 50 μm甚至更小的微凸点。这些微小尺寸凸点的电镀会涉及微小区域的选择性镀锡和其在微孔中的填充情况。

随着凸点尺寸的不断减小,界面反应、电迁移及热膨胀系数不匹配等问题变得更加突出。为了保证互连的可靠性,对电镀的质量要求也会随之提高。不仅要保证无空洞的填充,而且需要研究各种因素的影响和控制问题,包括镀层的微结构(晶粒尺寸、缺陷结构及晶面取向等)、镀层夹杂(杂质类型、含量及机理等)、均匀性(组成、厚度及相结构等)等。

4.2减少镀层夹杂

镀层夹杂就是指在电镀过程中杂质随镀层的生长而进入到镀层中,其表现就是镀层中含有C、S、N及O等杂质,相当于电沉积层受到污染。这种夹杂作用可能会改变镀层的氧化态和镀层的微结构(结晶颗粒及取向),引起镀层性能发生变化。这些杂质的存在会加剧锡镀层中锡晶须的形成,也会引起锡镀层容易发生变色问题[11]。随着镀锡及锡基合金在先进封装中应用范围的逐渐扩大,对镀层中的夹杂提出了更高的要求。

笔者[12]提出了一种抑制添加剂夹杂的新思路,即利用分子间相互作用在阴极表面构建添加剂的分子网络,以阻挡金属离子向阴极接近,从而实现对电沉积的控制。初步实验表明,在对电沉积实现良好控制的情况下,采用该方法可得到碳含量较低的镀层。

4.3引脚可焊性电镀——提高产品质量、降低成本

按照国际半导体产业联盟(ITRS)发布的国际半导体技术发展路线图(International Technology Roadmap for Semiconductor,2011),目前单芯片封装中仍然以引线键合型为主要的芯片与外部互连方式(占70%),而引线键合型中大部分都是以引脚的形式作为引出端。所以,锡及锡基合金电镀技术目前仍然主要用于IC及各类电子器件引脚可焊性镀层的制作。

对于这些现有工艺,重点是提高产品质量、降低成本。目前,尽管电子电镀锡及锡基合金技术已经比较成熟,但还必须面对不断出现的新问题。例如,现在国内使用的引线框架种类很多,有些低质量的框架可能会出现镀层发花、发黑,甚至变色的现象。所以,现有技术提升的重点是提高操作上的宽容度,进一步拓宽工艺窗口,增强镀液的适应性和易操作性。

[1]贺岩峰, 孙江燕, 张丹.无铅纯锡电镀中的若干问题[J].电子工艺技术, 2007, 28 (1): 20-23.

[2]SPEIGHT J G.Lange’s Handbook of Chemistry [M].16th ed.New York: McGraw-Hill Professional Publishing, 2005: 1.380-1.392.

[3]DIMITROVSKA A, KOVACEVIC R.The effect of micro-alloying of Sn plating on mitigation of Sn whisker growth [J].Journal of Electronic Materials, 2009,38 (12): 2726-2743.

[4]BAATED A, HAMASAKI K, KIM S S, et al.Whisker growth behavior of Sn and Sn alloy lead-free finishes [J].Journal of Electronic Materials, 2011, 40 (11):2278-2289.

[5]JO J L, NAGAO S, HAMASAKI K, et al.Mitigation of Sn whisker growth by small Bi additions [J].Journal of Electronic Materials, 2014, 43 (1): 1-8.

[6]STEIN J, REHM S, WELZEL U, et al.The role of silver in mitigation of whisker formation on thin tin films [J].Journal of Electronic Materials, 2014, 43 (11):4308-4316.

[7]SANDNES E, WILLIAMS M E, VAUDIN M D, et al.Equi-axed grain formation in electrodeposited Sn-Bi [J].Journal of Electronic Materials, 2008, 37 (4):490-497.

[8]PINSKY D A.The role of dissolved hydrogen and other trace impurities on propensity of tin deposits to grow whiskers [J].Microelectronics Reliability, 2008, 48 (5):675-681.

[9]HWANG J S.Tin whiskers: capsulization [J].SMT Magazine, 2014 (7): 16, 18-22, 24-29.

[10] CRANDALL E R.Factors governing tin whisker growth [M].New York: Springer, 2013: 34-42.

[11] ZENG X, SUN H Q, HE Y F, et al.Reflow discoloration formation on pure tin (Sn) surface finish [J].Microelectronics Reliability, 2012, 52 (6): 1153-1156.

[12] HUA H Y, WANG W J, SHI X M, et al.Effects of the intermolecular interactions between phthalic acid and surfactants on electrodeposition of tin [J].Journal of the Electrochemical Society, 2014, 161 (4): D190-D194.

[ 编辑:周新莉 ]

Tin and tin alloy electroplating in electronic industry: present status and prospect

HE Yan-feng*, LU Tong-juan,

WANG Fang

The recent advances of tin and tin alloys (such as tin-silver, tin-copper, and tin-bismuth) electroplating in the electronic industry were reviewed.Related electroplating processes, tin whisker growth in coatings, and application status of tin and tin alloy electroplating in advanced electronic packaging were discussed.The future development tendency of tin and tin alloy electroplating in the electronics industry was predicted.

tin; tin alloy; electroplating; whisker; packaging; electronic industry

TQ153.2

A

1004 - 227X (2015) 04 - 0217 - 06

2014-12-18

2014-12-29

贺岩峰(1957-),男,教授,内蒙古赤峰人,主要从事功能型薄膜电子化工材料及电沉积相关的研究工作。

作者联系方式:(E-mail) yfhe@mail.ccut.edu.cn。