一种基于FPGA的嵌入式实时以太网

贺永鹏,张向前,张凯,徐莉,王诗祺

(天津电气科学研究院有限公司,天津300180)

一种基于FPGA的嵌入式实时以太网

贺永鹏,张向前,张凯,徐莉,王诗祺

(天津电气科学研究院有限公司,天津300180)

提出了一种基于FPGA的嵌入式实时以太网。通过分析国际上多种实时工业以太网的特点,针对模块化设备对内部高速通讯的需求,设计了一种简化的实时以太网协议,并通过FPGA实现,最后通过实验进行验证;协议完全基于FPGA实现,简单可靠、通讯延时小,解决了现有工业以太网应用复杂、增加成本等问题,为高性能模块化工业控制系统奠定了通讯技术基础。

实时以太网;现场可编程门阵列;嵌入式

随着工业自动化控制系统的快速发展,工业设备向着智能化、模块化的方向推进。设备的模块化使零、部件具有通用性、互换性,延长了产品的生命周期,整体上降低了产品成本,提高了产品性能。模块化的产品需要借助强有力的通讯连接,来组成一个优化的工业控制系统。

目前设备内部各模块或板卡之间数据传输多采用并行总线和串行工业总线方式,其中背板并行总线包括VME总线、PCI总线等。并行总线具有高速、高同步性的特点,但并行总线一般需要在背板上实现,且对板卡设计有较高要求。依靠背板的设计也限制了接入设备的数量和结构。

串行工业总线包括RS-485总线、CAN总线等,具有实现简单、安全可靠的特点,但串行工业总线的通讯速率一般在10M以下,只适合设备各模块间通讯速度要求不高的场合。

近年来实时工业以太网技术发展迅速,工业以太网既有串行工业总线简单、安全可靠的特点,又有并行总线高速、高同步性的特点。但工业以太网技术需要考虑与商用以太网的兼容,主站需要支持TCP/UDP/IP协议,所以往往使用PC机或高性能嵌入式处理器实现,同时标准协议技术复杂,开发移植成本高,无法直接用于设备内各模块间的数据通讯。某些公司会开发自有协议来实现设备模块间的通讯,例如西门子在新一代驱动产品SINAMICS中,使用了分布式模块化的设计,各模块间通过高速驱动通讯接口DRIVE-CLiQ相互连接。多种功能模块不但可以自由组合,而且可以实现多轴高性能控制。

本文提出了一种基于FPGA的嵌入式实时以太网方案,有以下特点:1)采用主从方式通讯,用FPGA实现通讯协议,便于植入到嵌入式控制器中;2)通过寄存器配置实现通讯控制,降低了控制系统负担;3)借鉴Ethercat飞速传输的转发机制,缩短以太网帧在从站间的传递延时;4)实现时钟同步,时钟偏差小于100 ns;5)实现周期通讯窗口和非周期通讯窗口。

1 系统结构及原理

1.1 通讯协议模型和拓扑结构

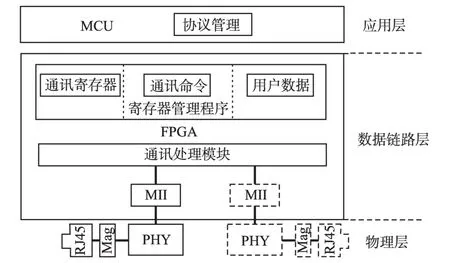

本设计采用精简的3层协议结构:物理层、数据链路层和应用层,图1为通讯协议模型。主站设备为单RJ45端口,从站设备为双RJ45端口。

图1 通讯协议模型Fig.1 Protocol model

数据链路层在FPGA中实现,由通讯处理模块和寄存器组成。主站寄存器由通讯寄存器、通讯命令寄存器和用户数据寄存器3部分组成;从站寄存器由通讯寄存器和用户数据寄存器组成。

应用层通过对数据链路层寄存器配置实现对通讯的管理和从站数据的读写。

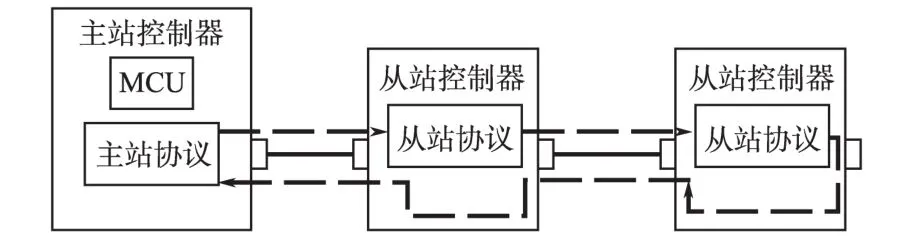

数据传输的拓扑结构参见图2。本设计采用一主多从直线型网络拓扑结构,各个站点首尾相连,相互之间使用标准网线连接,尾站只有一个接口与前站连接。这样可在网络中形成两个数据流,第1个数据流由主站发送数据帧,数据通过各从站的协议处理模块到达尾站;第2个数据流由尾站将处理的数据通过各从站透传至主站。

图2 拓扑结构Fig.2 Topology structure

1.2 链路层协议原理

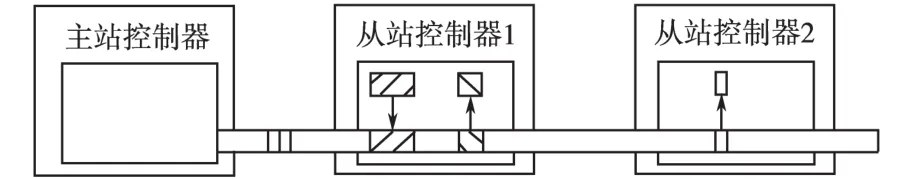

数据链路层采用飞速传输机制,在通讯数据传输不停顿的情况下,从站在特定的“时间窗”内,将与本站有关的数据从数据帧中提取出来,并把本站要输出的数据插入到帧内,同时对数据进行检查校验。传输机制的示意图参见图3。

图3 传输机制Fig.3 Transmission mechanism

通讯只能由主站发起,每次通讯由主站发送一个数据帧,在一个数据帧中包含所有从站的子报文,每个子报文用来与特定的从设备进行数据交换。从设备在一个传输周期中读取子报文接收数据帧,并将本站的数据插入到子报文发送数据帧中,使数据帧在传输中的延时降到最低。

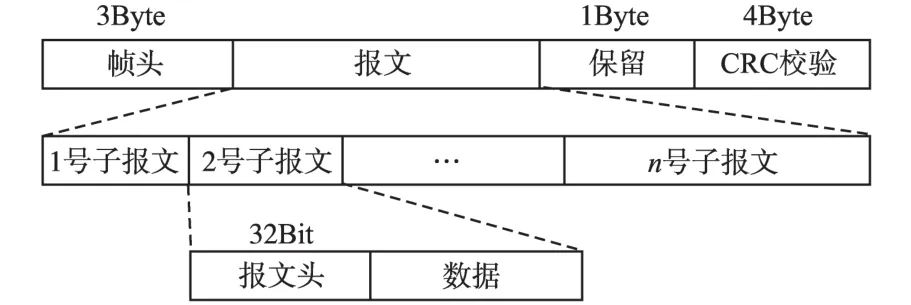

1.3 帧结构

由于不需要与以太网兼容,帧结构中舍弃了TP协议头和TCP/IP协议头。考虑到要采用寄存器控制方式,所有的控制通过寄存器配置实现,所以只定义一种帧格式。同时为最大限度利用数据带宽,采用了精简的帧结构。其中帧头包含16位类型标示及8位报文长度,FCS采用32位的CRC校验。子报文头包含操作命令和从站寻址。帧结构如图4所示。

图4 帧结构Fig.4 Frame structure

1.4 时钟同步

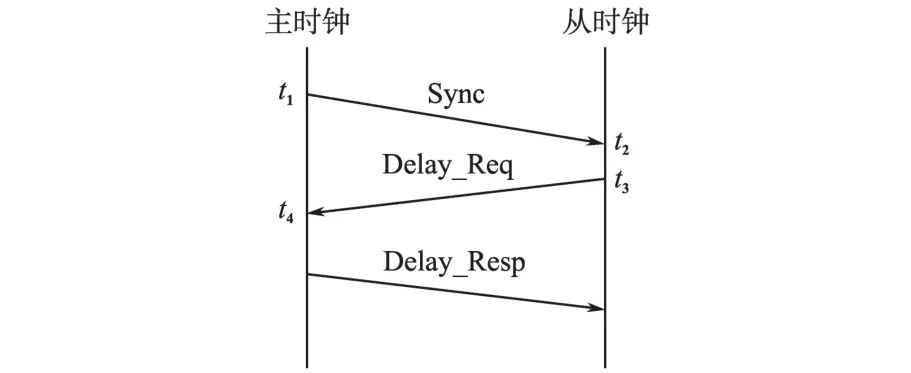

整个通讯系统内部,即主站和所有从站中各模块的时钟同步对于组成高性能控制系统十分重要。本设计借鉴IEEE1588精确时钟同步协议原理实现时钟同步,根据本设计特点只需使用两帧数据,就可以实现网络中所有从站时钟同步。

IEEE1588协议是通过在主站和从站之间利用传输“同步报文(Sync)”、“延时请求报文(Delay Request)”、“延时响应报文(Delay Re-sponse)”3种同步帧的方式,测量网络延迟时间和主从时钟偏移时间。工作过程如图5所示,从站分别得到主站通过“同步报文”发送的时间t1,从站记录接收到“同步报文”时间t2,从站记录发送“延时请求报文”时间t3,主站记录收到“延时请求报文”的时间t4,并通过“延时响应报文”发送给从站。

图5 偏移和延迟的测量Fig.5 Measure the offset and delay

从站利用下式求出网络延迟时间Delay和主从时钟偏移时间Offset:

由于本设计采用飞速传输机制和直线型网络拓扑,启动同步机制时“同步报文”和“延时请求报文”可以在一帧数据中实现,主站再发送一帧“延时响应报文”就可以实现同步。但由于采用直线型网络拓扑,数据帧会多通过一条回传路径,所以主站收到“延时请求报文”时间t4需要减去回传路径延时。

1.5 传输类型

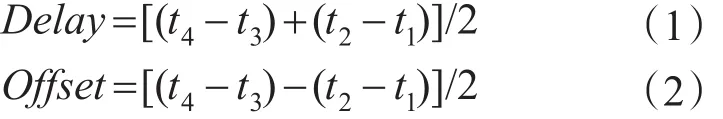

本协议支持周期通讯窗口和非周期通讯窗口两种类型。

周期传输用于主从设备之间每个控制周期内的固定通讯,周期传输优先级最高,具有最高的实时性,不能被打断或占用。非周期传输用于非固定周期、实时性要求不高的通讯任务,在周期传输的间隙中进行。传输类型如图6所示。

图6 周期窗口与非周期窗口Fig.6 Periodic and non⁃periodic window

2 设计与实现

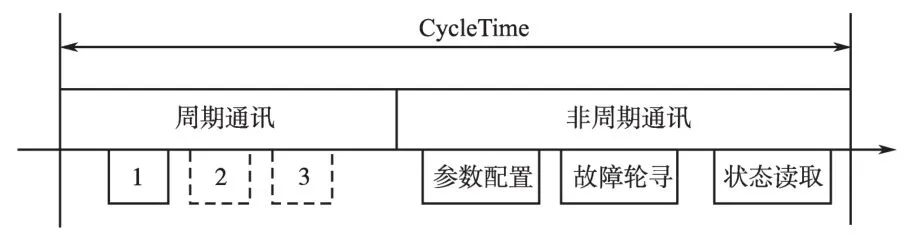

通讯程序分为主站程序和从站程序,主站的程序框图参见图7。图7中发送器和接收器分别由独立的模块实现;主站寄存器控制包括寄存器管理和相应的控制逻辑;PHY管理用于对物理芯片的配置;通讯仲裁用于控制非周期通讯使能;时钟同步用于同步管理。

图7 主站程序框图Fig.7 Master station program block diagram

主站寄存器控制是主站程序的核心,由控制寄存器、命令寄存器、数据寄存器3部分组成。寄存器在FPGA内部实现,由寄存器管理模块控制。通讯控制和数据操作通过寄存器实现。

控制寄存器用于控制通讯的操作,监控通讯状态。命令寄存器操作命令控制一个子报文的生成。在初始化过程中,MCU通过与FPGA的接口发送配置寄存器命令。通讯开始运行后发送器会读取命令寄存器的命令,并进行解析。数据寄存器用于存储子报文中的数据,数据寄存器是在主站中从设备寄存器的映射,包括从设备控制寄存器和数据寄存器。

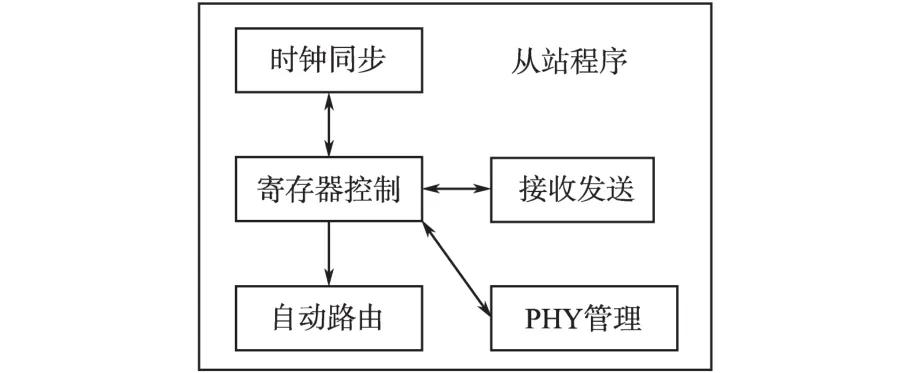

从站的发送和接收使用一个模块实现,实现收发同时进行。从站寄存器控制包括从站寄存器和控制逻辑;自动路由可以实现通信路由功能;时钟同步用于实现从站时钟同步。从站程序框图如图8所示。

图8 从站程序框图Fig.8 Slave station block diagram

从站的收发使用两层状态机实现,外层状态机处理帧信息,内层状态机处理报文信息,这样帧处理和报文处理不会相互影响,便于协议的调整,见图9。

图9 从站接收发送状态机Fig.9 Transmit and receive state machine of slave station

3 实验验证

通过实验对本文提出的实时以太网协议进行了验证,实验系统主站使用Altera DE2-115开发板实现,板上有2个千兆以太网接口,主控芯片为Cyclone IV EP4CE115,MCU由FPGA中NIOSII软核实现。从站使用自主开发的通讯板卡,主控芯片为Cyclone IV EP4CE40,有2个百兆以太网接口和2个光纤接口。测试使用1个主站和4个从站组网,在每个从站共收发20字节数据,总共640 bit数据情况下,最小通讯周期为11 μs;通过对主站的在线观测,4个从站的数据延时为2.12 μs;同步时钟的抖动小于100 ns。实验结果验证了本通讯协议具有很高的通讯实时性、可靠性和可移植性。

4 结论

本文提出了一种基于FPGA的嵌入式实时以太网设计方案。主站与从站利用FPGA实现通讯协议,采用精简的3层协议结构和帧结构,拓扑结构为一主多从直线型结构,数据链路层采用飞速传输机制,具备主从时钟同步,并实现周期通讯和非周期通讯窗口。最后通过实验对本协议进行了验证。

本协议在保证通讯的可靠性与实时性的情况下,降低了控制器负担,便于移植,适用于模块化系统的高速通讯。

[1]冯世宁,马杰,赵雪飞.若干种实时以太网标准的比较[J].南京师范大学学报:工程技术版,2010(2):88-92.

[2]郇极,刘艳强.工业以太网现场总线EtherCAT驱动程序设计及应用[M].北京航空航天大学出版社,2010.

[3]周贤伟,韦炜,覃伯平.无线传感器网络的时间同步算法研究[J].传感技术学报,2006,19(1):22-23.

[4]IEEE 1588—2008 IEEE Standard for a Precision Clock Syn⁃chronization Protocol for Networked Measurement and Control Systems[S].

[5]崔衍,王潜平,马海波.基于FPGA的工业以太网灵活解决方案[J].微计算机信息,2009(5):167-169.

[6]德国倍福公司.实时以太网:I/O层超高速以太网[J].自动化博览,2004(4):48-50.

FPGA⁃based Embedded Real⁃time Ethernet Protocol

HE Yong⁃peng,ZHANG Xiang⁃qian,ZHANG Kai,XU Li,WANG Shi⁃qi

(Tianjin Research Institute of Electric Science Co.,Ltd.,Tianjin 300180,China)

A FPGA⁃based embedded real⁃time Ethernet was proposed.By analyzing a variety of real⁃time industrial Ethernet features on the international,in order to meet the needs of internal high⁃speed communications of modular equipment,a simplified real⁃time Ethernet protocol was designed,implemented through FPGA,and finally verified by experiment.This protocol is realized entirely based on FPGA,simple and reliable,and it′s delay is small,solves the complex of industrial Ethernet applications,increased costs and other issues,lay the foundation for communications technology of high⁃performance modular industrial control system.

real⁃time Ethernet;field programmable gate array(FPGA);embedded

TM461

A

2014-10-20

修改稿日期:2015-02-02

贺永鹏(1983-),男,硕士研究生,工程师,Email:heyongpeng@tried.com.cn