具有抗谐波干扰的三相数字锁相环设计与仿真

陆原,汪周玮,郭素兵

(河北大学电子与信息工程学院,河北保定071002)

具有抗谐波干扰的三相数字锁相环设计与仿真

陆原,汪周玮,郭素兵

(河北大学电子与信息工程学院,河北保定071002)

在光伏或风能的三相有源逆变过程中,获取三相电网实时基波相位是非常重要的。针对当电网出现三相电压不平衡或较强的高次谐波干扰的情况,给出了一种具有抗谐波干扰的三相数字锁相环设计方案,并对方案的工作原理做了说明。最后,利用Matlab/Simulink对该三相数字锁相环在各种条件下做了对比分析,证明了基于多二阶广义积分器三相数字锁相环设计方案可以消除各次谐波的影响,使三相锁相环获得良好的跟踪基波相位的效果。该方案可以移植到FPGA中,构成全硬件集成锁相环;也可以移植到DSP中,构成全软件锁相环。

二阶广义积分器;三相鉴相器;数字锁相环;设计与仿真

无论是光伏还是风能,在三相有源逆变过程中,获取三相电网实时基波相位是非常重要的。锁相环PLL(phase-locked loop)是一种能使输出信号与输入信号在相位和频率上保持同步的自动闭环控制系统,可用于电力电子设备的控制过程,跟踪电网相位。被广泛应用的单同步坐标系的软件锁相环(SRF-SPLL)[1-3],在电网电压对称、理想的情况下,通过设计锁相环的控制参数,可以获得良好的动态特性,即使电网电压含有高次谐波,由于系统本身有2个等效积分环节,对高频分量有较强的抑制作用。当电网出现瞬时故障而出现三相不平衡时,或出现较强的高次谐波时,单同步坐标系锁相环会使相位误差增大以致不能准确跟踪三相电网实时基波相位。

本文提出一种基于多二阶广义积分器三相数字锁相环设计方案,可以在电网三相不平衡时或出现较强高次谐波时正确跟踪电网正序分量的基波相位,本文利用Matlab/Simulink在各种条件下对该三相数字锁相环做了对比分析,证明了基于多二阶广义积分器三相数字锁相环设计方案可以消除各次谐波的影响,使三相锁相环获得良好的跟踪基波相位的效果。

1 设计原理

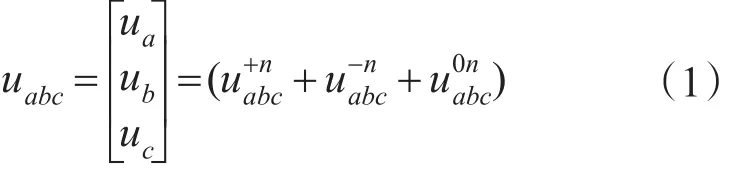

电网在瞬时故障或某些情况下,三相电网电压会变得不平衡,此不平衡三相电压可表示为一系列不平衡谐波成分的合集[4]。这时就能分解出有幅值的负序。一般的三相电压uabc可表示为正序分量、负序分量和零序分量的合集为

式中:+n,-n,0n分别为电压矢量正序分量、负序分量和零序分量的n次谐波分量。

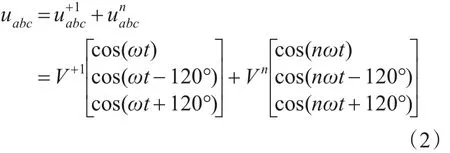

对于采用隔离变压器网侧为角接的分布式电源系统,可忽略零序分量,仅包含的正序基波或正序n次谐波或负序分量n次谐波,可表示为

式中:ω为电网角频率;θ为A相相位,θ=ωt。n>0时表示正序分量,n<0时表示负序分量。可以理解为三相正序基波合成矢量V+1在平面abc 3轴坐标系下,以角频率ω逆时针旋转;负序合成矢量V-1(n=-1)以角频率-ω顺时针旋转。经Clark变换后,abc 3轴变αβ两轴静止直角坐标系,如下式所示:

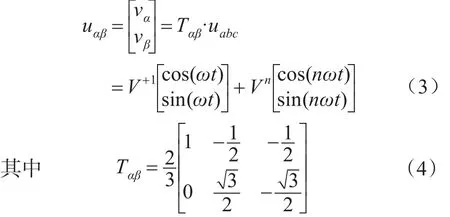

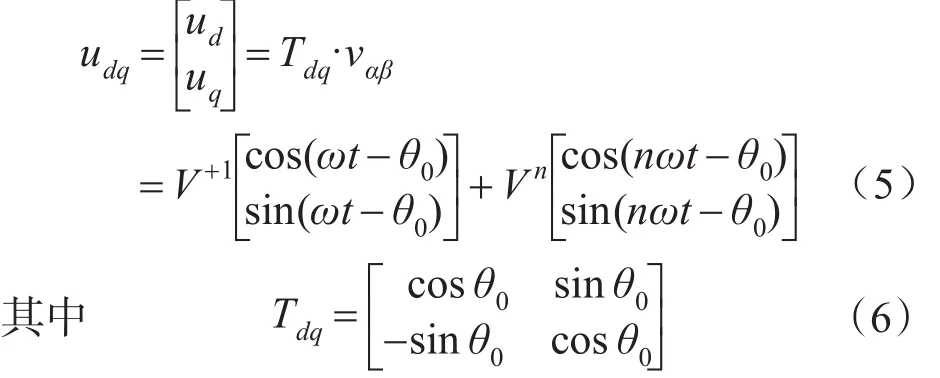

通过Park变换引入的旋转坐标系;旋转坐标角频率ω0,ω0为本地角频率,本地相位为θ0=ω0t。

得:

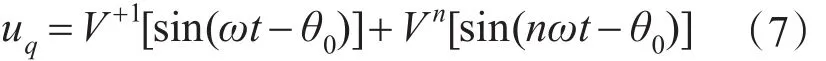

式(7)的第1项中,当三相正序基波合成矢量相位θ=ωt与旋转坐标相位θ0=ω0t相同时,表示相位锁定。此时作为三相鉴相器输出,uq的第1项V+1[sin(ωt-θ0)]≅0。

n=-1,为负序1次谐波,Part变换后,uq的第2项为V-1[sin(-ωt-θ0)]=-V-1sin(2ωt),-V-1sin(2ωt)实质上是由于负序分量1次谐波对鉴相器输出的干扰,它是50 Hz的2次谐波。解决的方法是设法生成一等幅、等频同相的信号,然后抵消uq中的干扰。

同理,n=2时,为电网中的2次谐波干扰,Park变换后,干扰为1次波V2sin(ωt)。

n=3时,为电网中的3次谐波干扰,Park变换后,干扰为2次谐波V3sin(2ωt)。

n=4时,为电网中的4次谐波干扰,Park变换后,干扰为2次谐波V4sin(3ωt)。

n=-1和n=3时,Park变换后,干扰均为2次谐波,但相位相反。

2 二阶广义积分器[5-6]

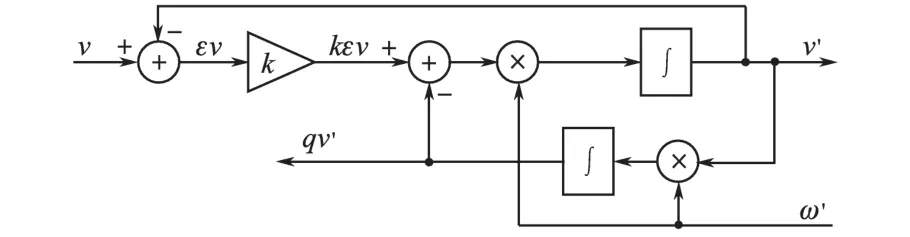

二阶广义积分器(SOGI)是由积分器、加法器、乘法器和放大器构成,如图1所示。完全可以由硬件实现。其特点如下:

1)它是具有选频特性的窄带带通滤波器,带通的中心频率为ω′,中心频率由输入信号ω′控制,ω′仿真时为一常数。图2a为它的选频特性,当输入v为等幅基波50 Hz,2次谐波100 Hz和4次谐波200 Hz,当ω′=2π×100时,输出v′对基波和4次谐波的衰减;

2)输出为v′和qv′,2路频率为ω′的正交信号。εv为输出v′与输入v之差;

3)图2b为二阶广义积分器的波特图,从幅频特性可看出对频率ω′零衰减,对ω′的其它谐波有较大衰减。从相频特性可看出对频率ω′无移相,对ω′的其它谐波移相近90°。

图1 SOGI结构图Fig.1 Structure diagram of SOGI

图2 SOGI的频率特性图Fig.2 The characteristic diagram of selecting frequency of SOGI

4)二阶广义积分器的实现方法。用模拟的方法实现二阶广义积分器功能相对比较困难,因为需要相对应的模拟器件。可以用数字方法实现。

硬件方法实现:利用FPGA器件的通用AD_IP核在FPGA内设计AD转换器,AD转换器可对输入信号作实时AD。然后对AD转换结果可做并行的硬件加法、乘法和积分运算。输出为数字编码。

软件方法实现:利用DSP器件直接对输入信号作实时AD转换。然后对AD转换结果可做顺序的软件加法、乘法和积分运算。

硬件方法比软件方法运算速度要快。

3 三相数字锁相环

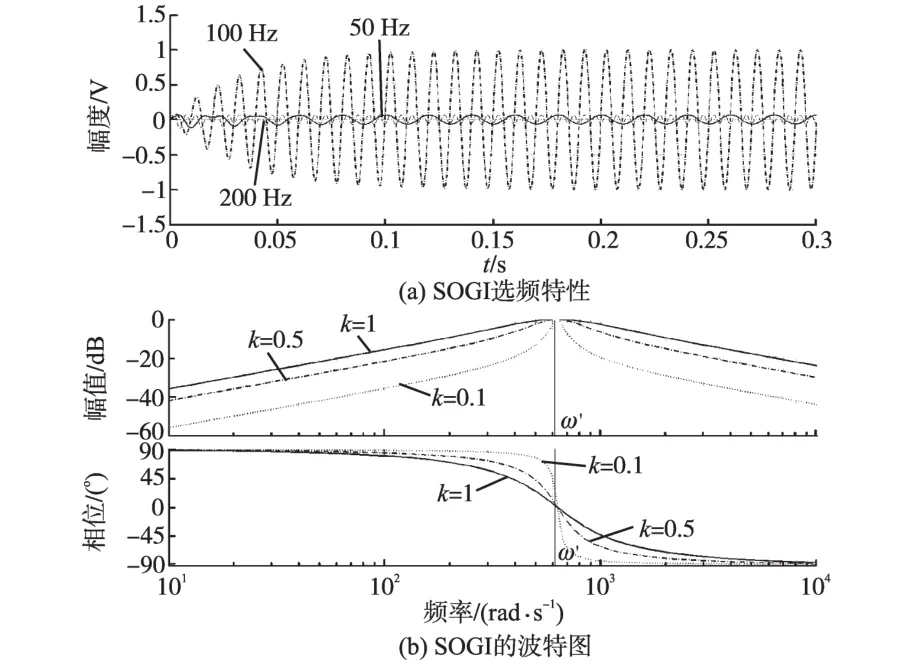

图3a是“基于多二阶广义积分器的三相数字锁相环”结构原理框图,它是由三相鉴相器、m个SOGI构成的滤波器和数字分频器组成。

1)三相鉴相器。三相鉴相器是由Clark变换器、Park变换器和PI调节器组成,输入为2部分,采样后的电网实时三相电压值和由三角函数表ROM输出的旋转坐标的旋转角度离散的三角函数值,uq为三相鉴相器输出。

2)滤波器。由m个二阶广义积分器(SOGI)构成,可滤除1~m次谐波[7]。当相锁定后,同时保留鉴相器输出V+1[sin(ωt-θ0)]=Δθ′→0直流分量。图3b是由4个SOGI组成的滤波器,可滤除1~4次谐波。

3)数字分频器。数字锁相环晶振产生标频4n kHz,经4分频、n分频和20分频后,获50 Hz、相位为θ0的本地同步信号。

图3 “基于多SOGI的三相数字锁相环”的结构原理框图Fig.3 The principle diagram of three phase digital phase locked loop based on multi second⁃order generalized integrator

在4分频电路中,可根据三相鉴相器的PI控制输出Δθ′>0,Δθ′<0或Δθ′=0,控制分频电路插入计数脉冲或扣除计数脉冲来调整本地50 Hz相位θ0。等效加减门电路在不同的Δθ′状态下为3分频电路、5分频电路或4分频电路。

20分频电路为20进制循环计数器,5根状态输出为三角函数ROM表提供5根地址线。

4 Matlab/Simulink对比仿真分析

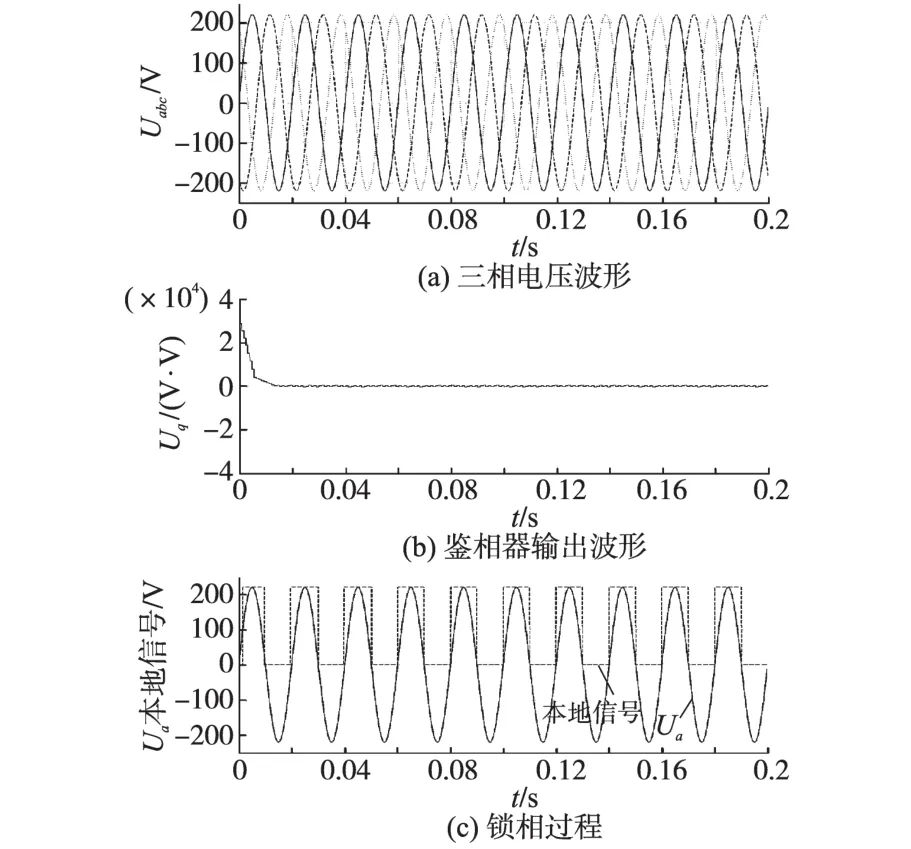

图4三相电压正常时的仿真图Fig.4 Simulation diagram while three⁃phase voltage is normal

图4 为三相电压正常时的仿真图,无谐波分量,锁相环不加SOGI滤波。图4a为三相电压波形;图4b为鉴相器输出波形;图4c为锁相过程。

结论:三相电压无谐波,锁相环不加SOGI时,如图4b所示,大约在0.02 s时,鉴相器输出规律性变化,由图4b,此时锁相环完成锁相。

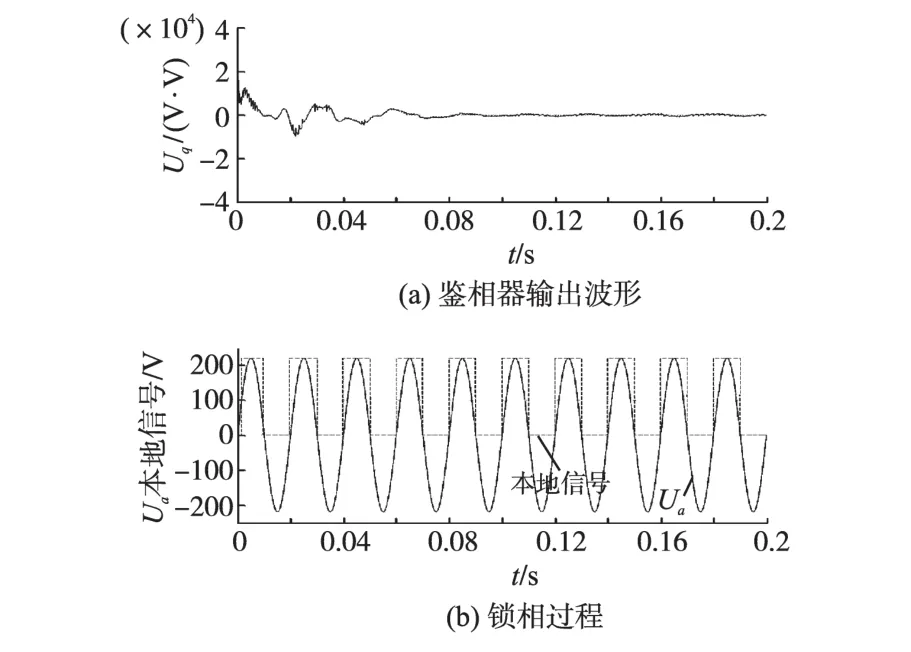

三相电压无谐波,锁相环加SOGI时,图5a为鉴相器输出波形;图5b为锁相过程。

图5 三相电压无谐波,锁相环加SOGIFig.5 Three⁃phase voltage without harmonic,phase locked loop with SOGI

结论:三相电压无谐波,锁相环加SOGI后,由图5a可知,对鉴相器输出、锁相过程均有影响,可忽略。由图5b可知,大约在0.08 s时完成锁相。

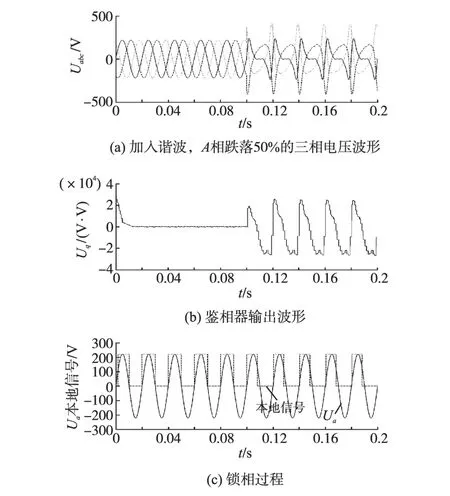

图6 三相电压有谐波,A相跌落,锁相环不加SOGI滤波Fig.6 Three⁃phase voltage with harmonic,phase A drop,phase locked loop without SOGI

图6 为三相电压加入谐波时的仿真图。三相电压加入2~5次谐波,幅值依次递减50%,分别为110 V,55 V,27 V,13 V;同时,A相跌落50%,锁相环不加SOGI时,图6a为三相电压加入上述谐波,A相跌落50%的波形;图6b为鉴相器输出波形;图6c为锁相过程。

结论:当在0.1 s时,三相电压加入依次递减50%的2~5次谐波,幅值分别为110 V,55 V,27 V,13 V,A相跌落50%,锁相环不加SOGI,由图6a可知,鉴相器在0.1 s前波形平稳,之后大幅度波动,幅值约为27 000 V2,由图6b可以看到锁相后,相差超出允许范围。

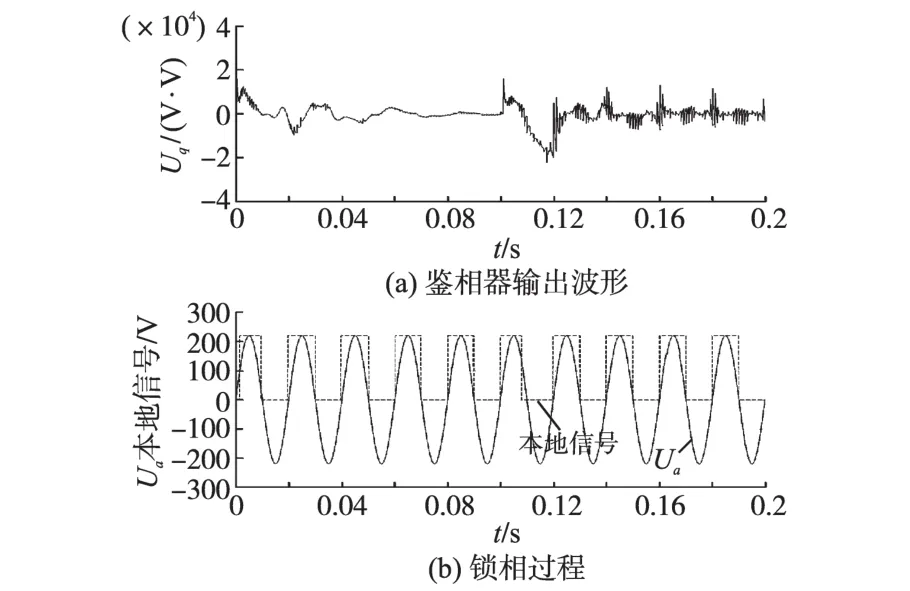

图7为三相电压加入依次递减50%的2~5次谐波时,幅值分别为110 V,55 V,27 V,13 V,并且A相跌落50%,锁相环加入SOGI滤波后,图7a为鉴相器输出波形;图7b为锁相过程。

图7 三相电压有谐波,A相跌落,锁相环加入SOGI滤波Fig.7 Three⁃phase voltage with harmonic,phase A drop,phase⁃locked loop with SOGI

结论:在0.1 s时,三相电压加入50%的2~5次谐波,幅值分别为110 V,55 V,27 V,13 V,A相跌落50%,锁相环加SOGI后,由图7a可知,0.1 s前鉴相器输出波形趋于平缓,锁相完成;在0.1 s后,波形相位出现波动,但是0.14 s之后,幅峰值约为8 000 V2,对鉴相器输出有影响。由图7b分析,相位能够锁定。计算后,锁相误差在允许范围。

5 结论

关于相位误差国家没用专门的标准,在GB/T 15945—2008《电能质量电力系统频率偏差》规定了电力系统正常运行条件下频率偏差限制为±0.2 Hz[8]。检测方法是1 s间隔内计到的整数周期与整数周期累计时间之比,相当于1个周期最大相差应小于1.44°。所以仿真时以1.44°作为误差允许范围。

从仿真结果可以看出加入二阶广义积分器,对锁相环跟踪电网相位带来的影响。当三相电网出现谐波和三相不平衡时,加入二阶广义积分器后,鉴相器输出幅度峰值衰减70%。锁相后,满足相位误差要求。证明二阶广义积分器对谐波确实起到滤除效果。仿真结果验证了方案正确性和可行性,本地相位可以快速跟踪三相电网正序基波相位。

利用Simulink实现了具有抗谐波干扰的三相数字锁相环功能仿真,说明设计方案理论上是可行的。该方案可以移植到FPGA中,构成全硬件集成锁相环;也可以移植到DSP中,构成全软件锁相环。

[1]吉正华,韦芬卿,杨海英.基于dq变换的三相软件锁相环设计[J].电力自动化设备,2011,31(4):104-106.

[2]Zhan C J,Fitzer C,Ramachandaramurthy V K,et al.Soft⁃ware Phase⁃locked Loop Applied to Dynamic Voltage Restor⁃ er(DVR)[C]//Power Engineering Society Winter Meeting,2001,3:1033-1038.

[3]洪小圆,吕征宇.基于同步参考坐标系的三相数字锁相环[J].电工技术学报,2012,27(11):203-209.

[4]杨君,王兆安,邱关源.不对称三相电路谐波及基波负序电流实时检测方法研究[J].西安交通大学学报,1996,30(3):94-97.

[5]孔飞飞,袁铁江,晁勤,等.基于二阶广义积分的变流器电网同步法[J].电力系统保护与控制,2012,40(12):116-120.

[6]Remus Teodorescu.光伏与风力发电系统并网变换器[M].周克亮,译.北京:机械工业出版社,2012.

[7]Rodirguez P,Luna A,Candela I,et al.Grid Synchronization of Power Converters Using Multiple Second Order General⁃ized Integrators[C]//Industrial Electronics,2008:755-760.

[8]全国电压电流等级和频率标准化技术委员会.GB/T 15945—2008电能质量电力系统频率偏差[S].北京:中国标准出版社,2008.

Design and Simulation of Three⁃phase Digital Phase⁃locked Loop with Anti Harmonic Interference

LU Yuan,WANG Zhou⁃wei,GUO Su⁃bing

(Electronics and Information Engineering College,Hebei University,Baoding 071002,Hebei,China)

In the process of photovoltaic or wind energy with three phase active inverter,obtaining the three⁃phase power grid real⁃time fundamental phase is very important.For when the grid appears unbalanced three⁃phase voltage or strong situation harmonic interference,proposed a three⁃phase digital phase lock with anti harmonic interferenceringdesignscheme,andtheworkingprinciplewasexplained.Finally,usedofMatlab/Simulinkforthethree⁃phase digital phase locked loop to do a comparative analysis under various conditions,proved that two order generalized integrator based on three⁃phase digital phase locked loop design scheme can eliminate the effect of harmonics,the three⁃phase phase⁃locked loop tracking the fundamental phase obtained good effect.The scheme can be transplanted to FPGA,constitute a full hardware integrated PLL;can also be transplanted to DSP,constitute the entire software phase⁃locked loop.

second⁃order generalized integrator(SOGI);three⁃phase phase discriminator;digital phase⁃locked loop;design and simulation

TN712;TM919

A

2014-09-22

修改稿日期:2015-03-01

陆原(1957-),男,高级工程师,Email:luyuan@hbu.edu.cn