功耗约束下的3D-SICs测试调度优化算法

焦 铬,李 浪,刘 辉,邹 祎

(1.衡阳师范学院计算机科学系,湖南衡阳 421002;2.湖南交通工程学院电气与信息工程系,湖南衡阳 421001)

功耗约束下的3D-SICs测试调度优化算法

焦 铬1,2,李 浪1,刘 辉1,邹 祎1

(1.衡阳师范学院计算机科学系,湖南衡阳 421002;2.湖南交通工程学院电气与信息工程系,湖南衡阳 421001)

提出了一种功耗约束下的三维堆叠集成电路(3D-SICs)测试调度优化算法。该算法在功耗约束下,协同优化了测试应用时间、TAM总线带宽和测试硬件开销。通过采用ITC’02标准电路中的d695和p93791做应用验证,结果表明该算法将测试应用时间分别减少为91.25%和93.11%,证明算法能有效地减少测试应用时间,降低测试成本。

功耗约束;三维堆叠集成电路;测试调度

0 引言

随着以硅通孔技术(Through Silicon Via,TSV)为核心的3D芯片结构的快速发展,对芯片的测试方法带来了新的挑战。三维堆叠集成电路比传统非堆叠的二维集成电路对测试的要求更高、更复杂,需要特殊的测试访问机制(Test Access Mechanism,TAM),测试结构不仅要支持单个芯片测试,还能实现对部分或全部堆叠集成电路进行测试。三维堆叠集成电路测试的一个重要目标就是降低芯片的测试时间,提高测试的经济性。

1 相关研究工作

进入SoC(System on Chip)时代以后,SoC所需的测试验证费用越来越高,已有很多研究者提出了许多方法来减少测试应用时间(Test Application Time,TAT)。二维结构下TAM设计、测试调度问题已有广泛研究。文献[1]使用ILP(整型线性规划)模型对TAM带宽的划分和芯核分配进行了优化,减少了总体测试时间。文献[2]提出了一种基于遗传算法的SoC 测试调度方法,该方法对测试总线的划分进行优化,合理调度,以实现各个芯核的并行测试,考虑了硬件开销的情况下,有效地缩短了芯核的测试时间,但没有优化测试成本。文献[3]提出了一种灵活TAM总线分配的SoC测试调度方法,将一个 IP核灵活地分配多组测试总线,把IP核信息从宽度上进行分割,采用交叉熵方法进行求解,能有效地降低SoC的测试时间。

由于集成电路封装成本高,3D-SICs测试包括绑定前测试(Pre-bond Test)、绑定后测试(Post-bond Test)和最终测试(Final Test)。绑定前测试是对每个晶片分别测试,而绑定后测试是对多个晶片堆叠后进行测试,最终测试是对整个三维芯片系统封装后进行的系统测试。3D-SICs测试流程如图1所示。

图1 3D-SICs测试流程

同样,也有很多学者提出了解决3D-SICs测试问题的方法。文献[4]考虑测试调度中所需要的各种硬件开销,但没有优化整体测试成本。文献[5]提出了晶片级的外壳和三维测试结构设计,进行了绑定前和绑定后测试,但没有考虑测试调度问题。文献[6]提出了一种功耗约束下的测试调度优化算法,该算法能有效地权衡测试应用时间和硬件开销。本文主要研究在功耗约束下,协同优化测试应用时间、TAM总线带宽和测试硬件开销,使测试应用时间最少。

2 问题分析

2.1 测试结构

图2所示是一个基于核的3D SoC[7],两个硅层上分布了8块芯核,共有3条TAM:TAM1连接芯核C1、核芯C2、核芯C4,TAM2连接芯核C5、核芯C6、核芯C8,TAM3连接芯核C3、核芯C7,TAM1和TAM2贯穿了两个硅层。

图2 3D SoC测试结构示例

总测试时间:

T=Tpre+Tpost

式中:Tpre表示每个硅层绑定前的测试时间,即Layer1绑定前测试时间+ Layer2绑定前测试时间;Tpost表示芯片堆叠绑定后的测试时间。

假定用Ci(ti,TAMWi)表示芯核i使用的TAM带宽(用TAMWi表示)和测试时间(用ti表示)的集合。假设8块芯核使用的TAM带宽和测试时间为:C1(4,8)、C2(7,4)、C3(5,4)、C4(8,6)、C5(5,6)、C6(5,6)、C7(7,4)、C8(10,6)。测试时间如图3所示,绑定后的测试时间为20,从图3可以看出很多空闲时间没有得到有效利用。

图3 3D SoC测试时间

2.2 TAM总线分配

按照Si=ti×TAMWi计算所有芯核的矩形面积,8块芯核的面积如下:S1=32、S2=28、S3=20、S4=48、S5=30、S6=30、S7=28、S8=60。将矩形面积按TAM宽度作为第一主键降序、测试时间作为第二主键升序进行排序,得到的面积序列如下:S1、S5、S6、S4、S8、S2、S7、S3,然后将所有芯核按矩形面积大小分成2个集合:一个大面积集合Smax={S1、S5、S6、S4、S8},一个小面积集合Smin={S2、S7、S3}。将SoC测试调度抽象为装箱问题,将所有矩形装入具有固定宽度的箱子中,使得箱子的长度最小,即测试时间最小[3]。在实际使用TAM带宽不大于测试总线带宽TAMw_max的情况下,优先选择TAM宽度比较大和测试时间比较短的芯核,因为大的芯核很大程度上影响总测试时间,如果大的芯核分配的TAM带宽少,那么该芯核测试时间会延长,从而导致总测试时间延长。装填的第一步按排好的顺序选择Smax集合中的芯核,能满足最大的TAM的带宽,达到最小的测试时间,在填充时尽量占角靠边,使芯核放置得更整齐、紧凑;第二步按排好的顺序选择Smin集合中的芯核进行装填,小芯核本身TAM带宽和测试时间比较小,可以更灵活地放置,优化测试时间。8块芯核按上述方法装填后的效果如图4所示,测试时间为17,从图4可以看出该方法比图3所示的方法减少了测试时间,并且还有富余的空间可供其他芯核使用,测试时间能够得到很好的利用。该方法将TAM带宽分配由传统的连续固定分配变为根据TAM宽度和测试时间来调度分配,在不增加测试硬件开销的情况下,使得SoC内部各芯核的测试调度更灵活。

图4 SoC测试调度抽象为装箱问题的调度

2.3 功耗约束

三维堆叠集成电路的测试需要对每个芯核进行。减少TAT最主要的方法就是对尽可能多的芯核进行并行测试,而并行测试会激活芯片中的各个功能模块,会产生更高的功耗。测试模式下过高的功耗会影响电路的质量和性能,甚至会造成被测电路失效[8]。最大峰值功耗是测试过程中产生的最大瞬时功耗值。如果电路超过最大峰值功耗,就可能会产生错误甚至损坏。因此,本文设定的功耗约束条件定义如下:

(1)

式中:P(Ci)表示芯核Ci的测试功耗;n表示正在测试的芯核数;Ppeak_max表示最大瞬时功耗值。

3 算法描述

step 1:计算每块芯核Ci(1≤i≤N)可接受的TAM宽度TAMWi;

step 2:计算每块芯核Ci(1≤i≤N)的最小测试时间ti;

step 3:计算每块芯核Ci(1≤i≤N)的面积Si=ti×TAMWi;

step 4:将Si按TAMWi作为第一主键降序,ti作为第二主键升序进行排序,然后将所有芯核按面积大小分成2个集合Smax、Smin;

step 5:在实际使用的TAM带宽不大于测试总线带宽TAMw_max的情况下:

(1)当Smax≠∅,从Smax集合中按顺序对测试芯核根据式(1)判断是否满足功耗约束条件,是则进行TAM分配,计算测试应用时间,按装箱问题进行装填,在填充时尽量占角靠边,使芯核放置得更整齐、紧凑;否就从Smax中选择下一个芯核。从Smax集合中删除Si,从C集合中删除Ci;

(2)当Smin≠∅,从Smin集合中按顺序对测试芯核根据式(1)判断是否满足功耗约束条件,是则进行TAM分配,计算测试应用时间;否就从Smin中选择下一个芯核。从Smin集合中删除Si,从C集合中删除Ci。

step 6:在实际使用的TAM带宽大于测试总线带宽TAMw_max的情况下,没有芯核能够和已分配TAM带宽的芯核进行并行测试,待已测试芯核测试完后,返回step1,对余下的芯核重新分配TAM带宽,再次搜索满足条件的芯核进行并行测试。

step 7:直到Smax=∅并且Smin=∅,所有芯核均被测试,计算TAT;否则返回step5。

4 实验结果及分析

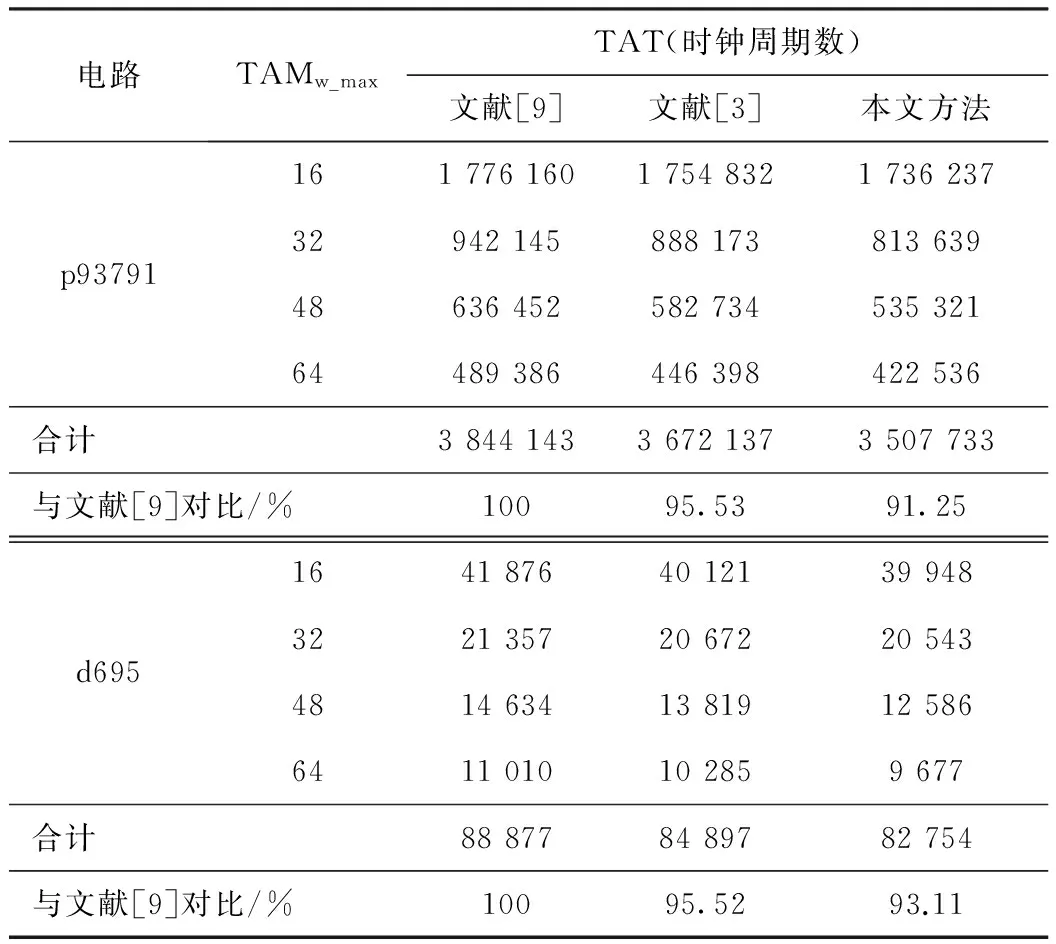

为了验证本文采用方法的有效性,选用2片ITC’02基准SoC进行仿真实验,分别是p93791、d695。p93791是标准电路中规模最大的电路,包含32个核,其中有18个存储器核,14个逻辑核,对电路测试的复杂度具有较强的代表性。d695包含8个时序电路及2个组合电路。本文算法采用MATLAB语言实现,实验用的计算机配置为联想Y400系列,内存为4 G,主频为2.6 GHz,采用与文献[3]相同的实验参数。表1的数据为在TAM带宽分别为16、32、48、64情况下,本文算法在p93791、d695电路上分别得到的最优TAT与文献[9]、文献[3]的对比。

表1 实验结果

从实验数据可以看出,本文提出的功耗约束下的TAM总线分配的测试调度算法在大多数情况下能够得到更好的测试结果。将3种方法在4种不同的TAM带宽下求得的最优TAT相加,把本文算法同文献[9]、文献[3]进行比较,相对文献[9],本文方法针对p93791电路测试应用时间减少为91.25%,比文献[3]对测试应用时间的减少多4.28%;针对d695电路测试时间减少为93.11%,比文献[3]对测试应用时间的减少多2.41%。

5 结论

针对3D-SICs测试调度问题,提出了一种功耗约束下的测试调度优化算法。该算法将测试调度在满足功耗约束条件下抽象为装箱问题,在装填时综合考虑TAM带宽和测试时间,对尽可能多的芯核进行并行测试。测试实验表明,该算法在不增加测试硬件开销的情况下,能较好地优化测试应用时间。

[1] WU X,CHEN Y,CHAKRABARTY K,et al.Test access mechanism optimization for core-based three-dimensional SOCs.Proceedings of IEEE International Conference on Computer Design,2008:212-218.

[2] 雷加,方刚.一种基于遗传算法的SoC测试调度方法.仪器仪表学报,2007,28(4):15-17.

[3] 邓立宝,俞洋,彭喜元.一种灵活TAM总线分配的SoC测试调度方法.仪器仪表学报,2011,6(32):1238-1244.

[4] MARINISSEN E J,VERBREE J,KONIJNENBURG M.A structured and scalable test access architecture for TSV-based 3D stacked ICs.Proceedings of IEEE Very Large Scale Integration Test Symp,2010:269-274.

[5] CHEN P W,WU C W,KWAI D M.On chip TSV testing for 3D IC before bonding using sense amplification.Proceedings of Asian Test Symposium,2009:450-455.

[6] 王伟,林卓伟,陈田,等.功耗约束下的3D多核芯片芯核级测试调度算法.电子测量与仪器学报,2012,7(26):591-596.

[7] LI J,LIN H,QIANG X.Test Architecture design and optimization for three-dimensional SoCs.Design,Automation & Test in Europe Conference & Exhibition,2009:220-225.

[8] 杨年宏.基于三维结构的SoC低功耗测试技术研究:[学位论文].合肥: 合肥工业大学,2011.

[9] HARMANANI H M,FARAH R.Integrating wrapper design,TAM assignment,and test scheduling for SoC test optimization.Montreal,2008:148-152.

Test Scheduling Optimization Algorithm for 3D Stacked ICs Under Power Constrains

JIAO Ge1,2,LI Lang1,LIU Hui1,ZOU Yi1

(1.Department of Computer Science,Hengyang Normal University,Hengyang 421002,China; 2.Department of Electrical Information Engineering,Hunan Institute of Traffic Engineering,Hengyang 421001,China)

This paper presented a test scheduling optimization algorithm for 3D stacked ICs under power constrains,which optimized test application time,TAM bus bandwidth and hardware expenses collaboratively.Using d695 and p93791 of the benchmark circuits ITC’02 to verify,the experimental results show that the test application time is reduced to 91.25% and 93.11% respectively.It proves that the proposed algorithm can effectively reduce the test application time and the test cost.

power constrains;3D-SICs;test scheduling

湖南省科技厅科技计划项目(2013FJ3077);湖南省教育厅资助科研项目(12C1084);衡阳市科技计划项目(2012KJ31);湖南省“十二五”重点建设学科资助项目(湘教发[2011]76号)

2014-11-05 收修改稿日期:2014-11-28

TP391.7

A

1002-1841(2015)02-0091-03

焦铬(1979—),副教授,博士生,主要研究领域:嵌入式系统及应用。E-Mail:jiaoge@126.com 李浪(1971—),教授,博士,主要研究领域:嵌入式系统。 E-mail:lilang911@126.com