基于FPGA的实时钢轨图像采集与预处理

马 俊,李春茂,郭 鑫

(1.西南交通大学电气工程学院,四川成都 610031;2.西南交通大学,牵引动力国家重点实验室,四川成都 610031)

0 引言

高铁的高速运行加大了对钢轨的磨耗,导致钢轨表面凹凸不平,影响列车在钢轨上的平稳运行,以致可能引发列车脱轨造成安全事故。因此需要对钢轨进行检测,传统钢轨检测主要依靠人工检测,效率低下,费时费力,本文提出实时采集钢轨图像并预处理,及时识别钢轨的各种形态缺陷并维护,保证钢轨表面的平整,使列车平稳安全运行。

实时钢轨图像动态数据量和运算量庞大,依靠传统的计算机和数字信号处理(DSP)进行图像数据采集和处理满足不了实时性要求。随着FPGA技术的不断发展和成熟,以及FPGA的低成本开发、动态灵活性强、并行数据处理能力快等优点[1],为实现大量钢轨图像的实时采集与预处理提供了可能。

本文提出一种基于FPGA的实时钢轨图像采集与预处理系统。在底层充分利用FPGA并行数据处理技术采集大量钢轨图像,并对钢轨图像作预处理,提取出钢轨图像轮廓减少图像数据量,进一步提高系统处理的实时性。

1 总体结构设计

总体结构框图如图1所示。CCD摄像机采集钢轨图像,并传输到解码芯片TW2867中,TW2867将模拟图像转换成数字图像;FPGA通过配置I2C总线采集数字图像,数字图像经过图像解析模块解析后通过图像读写模块存储在DDR2中;在图像处理模块中完成图像数据的色彩空间转换、快速中值滤波、边缘检测等预处理;预处理后的图像通过VGA控制模块产生行、场同步信号,最终在VGA上显示实时采集与预处理后的钢轨图像。

图1 钢轨图像采集与预处理总体框图

2 钢轨图像采集模块设计

本文中利用CCD摄像机采集钢轨图像,帧频30帧/s,输出分辨率为800×600的PAL制式模拟视频。视频A/D转换采用TW2867芯片,自动识别PAL/NTSC/SECAM制式视频,并输出8位数字视频信号,时钟频率27 MHz,同时用作整个采集模块的采样时钟。

本文使用I2C总线作为通信接口,对TW2867芯片的内部寄存器进行初始化设置[2],并根据 CCD摄像头参数设置TW2867输出的视频制式、大小、帧率等。

图像解析模块解析出数字图像的场同步、行同步、奇偶场等,输出16位图像数据,钢轨图像解析模块图如图2所示。

图2 钢轨图像解析模块图

3 钢轨图像读写模块设计

钢轨图像数据量大,同时为了提高采集和处理实时性,在系统中加入2片双倍速内存 (DDR2),带宽达10 Gb/s,容量达2 Gbit,满足图像处理过程中对高缓冲区的需求,通过读写模块将采集的图像数据写入DDR2中。

3.1 FIFO 模块设计

FPGA开发板时钟频率为50 MHz,TW2867输出的视频图像时钟频率为27 MHz,在系统中添加一个异步FIFO以解决系统数据缓冲和时钟不一致的问题[3],FIFO模块宽度16位,深度512。

3.2 图像写模块设计

钢轨图像数据在DDR2中的存储主要通过同步状态机将异步FIFO模块中的图像数据写入DDR2中。由于一帧图像数据的行消隐、场消隐处没有图像信息,将奇偶场消隐处图像剪切并合并为一帧后将图像的有效数据写入DDR2中,以提高写入速度。同步状态机如图3所示。

图3 钢轨图像写状态机

(1)BURST_IDLE:状态机空闲状态。当异步FIFO中数据快满时,开始从异步FIFO中读取数据,进入BURST_ONE_LINE_START状态,开始写一行的数据;

(2)BURST_ONE_LINE_START:一行的写操作开始。当BURST_ONE_LINE_START开始时,确认写操作,进入下一个状态BURSTING;

(3)BURSTING:写操作。如果图像数据写完后,则进入下一个状态BURST_END;否则继续BURSTING状态;

(4)BURST_END:写操作完成时确认一行数据是否已经完全写入。如果写完一行数据,则进入下一个状态BURST_ONE_LINE_END;如果尚未写完,则继续进入BURSTING中继续写数据。

(5)BURST_ONE_LINE_END:一行数据写入DDR2中,进入下一个状态BURST_IDLE。

4 图像预处理模块设计

4.1 色彩空间转换模块

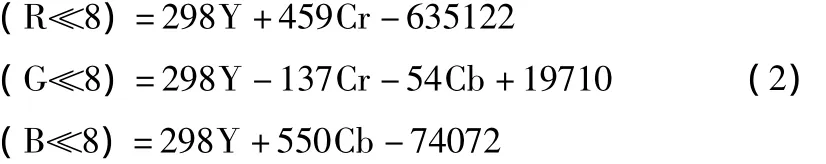

在FPGA内部,图像数据是以4∶2∶2 YCrCb格式传输,但现有显示设备采用RGB驱动。对图像数据进行色彩空间变换[4],实现YCrCb到RGB的转换。在计算机视觉系统中,修正后的转换公式如式(1)所示:

考虑到公式中的3位小数,为了方便计算,利用Verilog语言将小数左移8位化整,即乘以256,简化后如如式(2)所示:

4.2 快速中值滤波模块

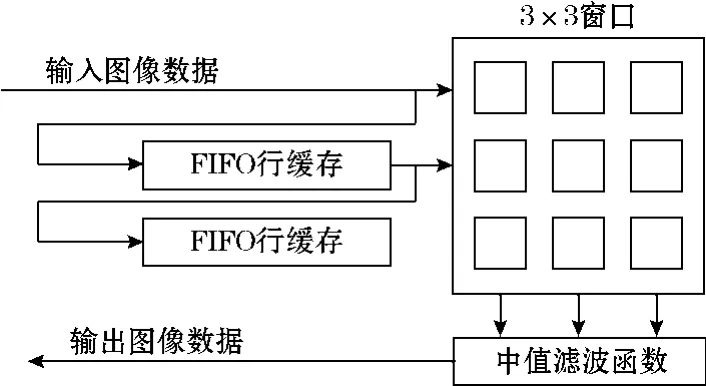

在钢轨图像的采集、解码、读写、空间变换等过程中产生了干扰噪声,降低了图像质量,本文采用快速中值滤波处理算法对图像数据进行滤波处理以消除噪声干扰。利用2个FIFO模块和3×3窗口对图像进行中值滤波处理,算法框图如图4所示。

图4 快速中值滤波模块

2行图像数据缓存在2个FIFO中,输入第三行图像数据时,3×3窗口在3行数据中滑动,中值滤波函数模块输出3行9个像素的中值。对于图像边缘数据的处理,默认为原始图像数据,不加处理。快速中值滤波模块Modelsim仿真结果如图5所示。

图5 快速中值滤波仿真波形图

4.3 边缘检测模块

在FPGA内采用Sobel算法对钢轨图像做边缘检测处理,提取出钢轨轮廓等有效图像数据以进一步减少运算数据量,提高系统实时性。

Sobel算法通过2个矩阵对钢轨图像作横向和纵向卷积得到图像的灰度值G,如式(3)、式(4)、式(5)所示:

再设置灰度阈值检测出钢轨图像的边缘,卷积原理图如图6 所示[5]。

图6 横向卷积运算原理图

在QuartusⅡ的MegaWizard Plug-In Manager中添加Shift register模块实现3行图像数据的缓存,添加ALTMULT_ADD模块实现图像横向和纵向的卷积运算,再添加PARALLEL_ADD和ALTSQRT模块实现开平方和根运算,得到图像的灰度值G。实验中设置灰度阀值为50,灰度值G大于50则输出为0,图像显示为黑色,反之则为白色。

5 VGA显示控制模块

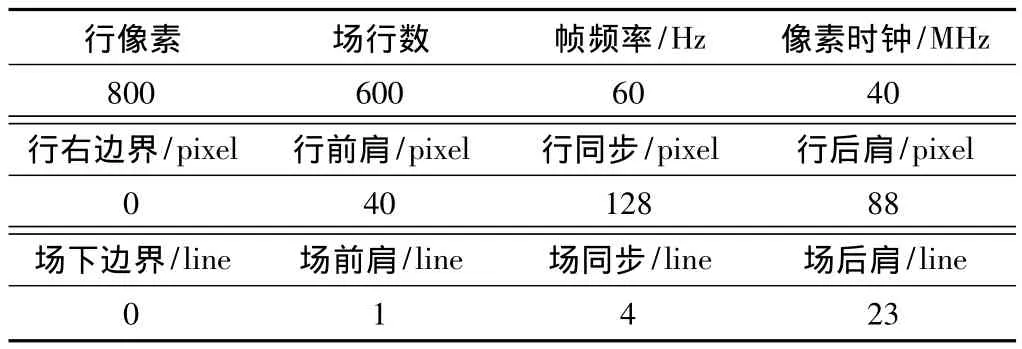

图像数据经过快速中值滤波和边缘检测处理后,通过VGA显示控制模块生成正确的时序,最终在VGA中实时显示采集并预处理后的钢轨图像[6]。VGA显示参数如表1所示。

表1 VGA显示参数

由表格1可知,像素时钟频率为40 MHz,行扫描周期为1 056个像素时钟周期,场扫描周期为628个行扫描周期。根据表1设计VGA控制模块,生成显示器所需的行同步时序和场同步时序。VGA时序仿真图如图7所示。

6 实验结果与性能分析

图7 VGA时序仿真图

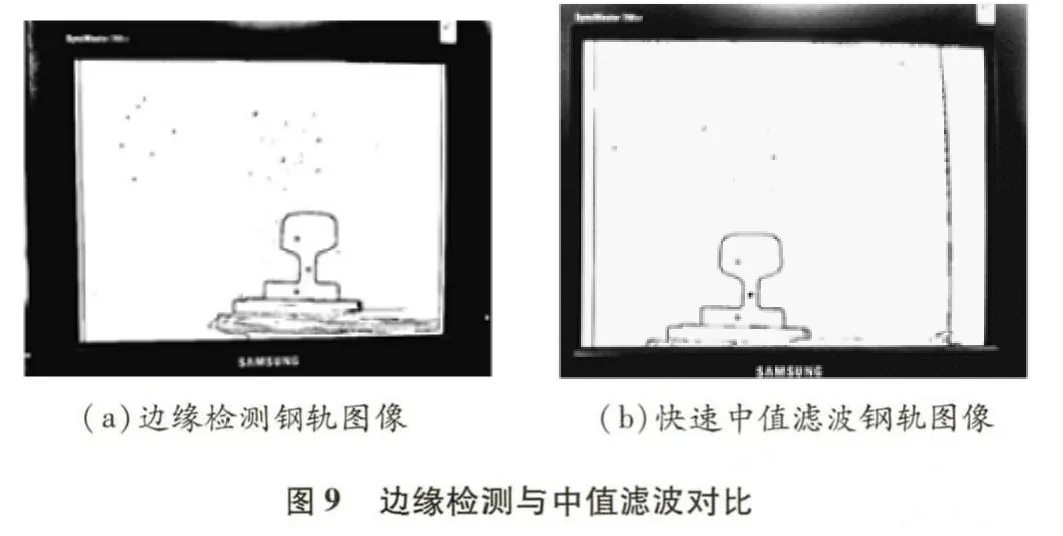

在Quartus II中采用Verilog HDL语言编写各模块,通过JTAG模式下载到FPGA中,实验结果如图8、图9所示。图8为CCD摄像头采集的实时钢轨图像,分辨率为800×600。图9为边缘检测和快速中值滤波后的钢轨图像,能够检测出钢轨的轮廓,采集的图像中有一些噪点,经过快速中值滤波后能够有效滤除钢轨图像周围的噪声,检测出的钢轨轮廓供上层算法作进一步高级处理。

图8 原始钢轨图像

将同一帧图像在Matlab中做快速中值滤波和边缘检测处理,调用Profiler Summary分析,处理1帧图像的时间为0.574 s,即574 ms。而在 FPGA中处理一帧800×600图像时间为480 416个时钟周期,即为9.608 ms,在FPGA上处理图像速度约为上位机处理软件的60倍,大大提高了系统的工作效率和实时处理性能。

7 结束语

针对CCD采集的钢轨图像数据量大等特点,提出了基于FPGA的实时钢轨图像采集与预处理研究,详细介绍了如何在FPGA上实现采集与预处理系统的各功能模块。对钢轨图像快速中值滤波和边缘处理后,实现了钢轨图像的去噪和快速提取,能够在VGA显示器中实时显示预处理后的钢轨图像。与基于PC机的上位机图像处理软件相比,图像处理速度更快,实时性更高。同时相比基于FPGA和DSP的图像处理模式,简化了系统设计,缩短开发周期,减少开发成本,且系统灵活性高。

[1]高迎慧,刘宾,王佳,等.基于DSP和FPGA的高速数据采集处理系统.仪表技术与传感器,2011(2):66-68.

[2]冯伟昌,林玉池,何东,等.基于FPGA的双通道实时图像处理系统.传感技术学报,2010,23(8):1118 -1112.

[3]卓浩泽,龚仁喜,谢玲玲,等.基于FPGA的多路高速数据采集系统的设计.电测与仪表,2011,48(9):65 -68.

[4]盛磊,徐科军.一种彩色空间变换的FPGA实现方法.仪器仪表学报.2005,26(8):378 -380.

[5]杨新华,寇为刚.基于FPGA的Sobel算子图像边缘检测算法.仪表技术与传感器,2013(1):102-104.

[6]李国刚,余俊,凌朝东.基于FPGA的VGA图形控制器的实现方法.信息技术,2006(7):25 -27.