调制激光干涉系统的嵌入式数据采集方法

王选择,王 刚,杨练根,曾志祥,肖康达

(1.湖北工业大学机械工程学院,湖北武汉430068;2.湖北省现代制造质量工程重点实验室,湖北武汉430068)

0 引言

在便携式测试系统信号采样中,高速、多路、集成的数据采集系统具有重要的实用价值。传统的数据采集系统在专业测试系统中的应用,一般需要繁琐的改造,难以满足高速与高集成度的要求,降低了测试系统的使用可靠性[1-2]。

在精密绝对距离测量方法中,基于电流调制的频率扫描干涉测量系统[3-4],需要在半导体激光器电流调制的过程中,同步采样至少两路干涉信号[5]。一路作为参考干涉信号,一路作为测量干涉信号,软件算法以两路采样信号为依据,通过信号处理,计算测量绝对距离。

这就要求专门的采样系统,能够按照系统要求,在满足软件触发开始的条件下,与电流调制过程协同进行,以较高的采样频率完成信号的A/D转换与存储。并在转换完毕后自动停止转换,并通知处理器取走数据,等待下一次转换启动命令的到来。这样的采样系统具有灵活的控制逻辑,达到与电流调制电路、缓存、A/D芯片、处理器的逻辑配合。

由于FPGA具有时钟频率高,内部延时小,编程配置灵活等一系列优点。在FPGA芯片内可以进行采集控制、缓冲、处理、传输控制、通信[6]。为此,本文针对频率扫描的测量系统,给出了一种基于FPGA的准同步、多路实时存储的数据采集方案。

1 测量系统测量原理

图1为设计采用的测量系统结构,该系统由2个迈克尔逊干涉系统组成,一个是测量干涉系统,一个是参考干涉系统。

准直的半导体激光器发出的激光通过分光镜BS1分成2束,一束进入比对干涉系统,形成干涉信号由光电探测器1接收;另一束进入测量干涉系统,形成干涉信号由光电探测器2接收。其中测量干涉系统的两臂长度差LM为测量距离,参考干涉系统的两臂长度差LR是已经标定的距离。

在半导体激光器上注入斜坡调制电流,实现激光波长线性调制。激光器输出波长调制的激光,经过偏振分光镜分为两束,进入臂长不相等的迈克尔逊干涉系统中,在调制电流量一定的条件下,干涉的光强相位变化量与光程差成正比。由于参考距离LR为已知,通过计算两干涉系统中干涉的光强相位变化量的比值便可得到被测距离,从而实现绝对距离测量[7]。

图1 绝对距离测量系统光路结构

2 电流正负调制电路、光电转换方法

电流正负调制电路由3部分组成,积分电路、激光器工作点调整电路和电压转电流电路,如图2所示。

积分电路的输入信号为FPGA提供的方波信号,通过编程,使FPGA的一个I/O口产生所需要的方波信号。方波信号高、低电平变化时,通过三极管Q1和Q2分别实现电容C1的充电和放电过程,用两个三极管分别控制是为了让充电和放电过程相互独立,互不影响。其中R6和R4的阻值相等,R7的阻值选择较大,是为了保证充、放电时间在一定范围内保持一致。

图2 电流正负调制电路

图中R8、R9、R10、C2组成激光器工作点调整电路,通过电容和调整电阻的阻值,可以滤掉直流信号和改变斜坡信号的大小。调整工作点是为了控制输入到激光器上的电流变化范围,保证这个变化范围满足波长随电流近似线性变化的要求。

经过激光器工作点调整电路,运放U3输入信号的电压在1 V左右,不在其工作范围,因此选择型号为TLC2272cp的满幅运放使其满足工作范围要求。运放U3和三极管Q4使经过调整后的电压转换成驱动激光器的调制电流。

为实现激光干涉光强信号转换成电流信号输出,进而将光电管的输出电流转换成电压并做相应噪声处理,设计了图3所示的光电转换电路。VCC为+3.3 V电源,D1为光电二极管,用于接收干涉光强信号,Q1为9013型三极管,用于放大光电二极管输出的电流,电阻R2用于将放大的电流转换为电压输出,电阻R1和电容C1用于过滤高频信号得到有效的输出电压。

图3 光电转换电路

3 FPGA数据采集系统

3.1 信号采集系统设计

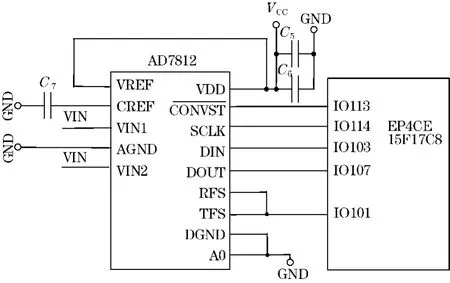

本数据采集系统由光电探测器1和2、光电转换电路、A/D模数转换模块、FPGA内部16位FIFO存取模块、串行通讯以及FPGA器件等构成。其中A/D芯片型号为AD7812,是一种高速、低功耗、8通道同步采样转换,采用2.7~5.5 V单电源供电的10位高速串行接口A/D转换芯片,采样频率为350 kHz,转换时间为2.9 μs,适合于集成式的高速采集系统要求。FPGA器件为EP4CE15F17C8,它控制数据转换、存储、读取等各个过程。

如图4所示,在系统中,由光电探测器1和2接收激光干涉信号,通过光电流转电压的方式完成光电转换,并通过选取适当元件参数,使转换电平处于0~3.3 V,以满足AD7812对输入信号幅值(0~3.3 V)的要求。FPGA主要控制A/D的初始化、启动、转换数据传输、存储的过程,且采样频率由FPGA内部时钟来设置。数据转换完成的同时FPGA发送写允许(wrreq)、写时钟信号(wrclk),触发FIFO读取数据。FIFO存储一定数量的A/D转换结果,存储完成后向FPGA发送满标志位(wrfull),通知FPGA停止A/D转换。然后将FIFO的数据通过串口通讯传输给上位机,进行实时显示。

图4 高速数据采集系统框图

3.2 FPGA控制模块

利用Verilog语言设计FPGA控制模块,主要包括A/D转换控制模块、存储模块、同步控制模块,分别实现了FPGA对A/D转换的时序控制、FIFO实时数据存储、电流调制和软硬同步触发。

3.2.1 A/D转换硬件连接方式

FPGA与AD7812硬件接口如图5所示。在本系统中,AD7812的VDD采用3.3 V电源供电,满足数据总线直接与FPGA(FPGA引脚的逻辑电平为3.3 V)连接要求。参考电压VREF引脚与VDD引脚直接相连。为避免AD7812外界噪音的干扰,将AGND、DGND引脚接地,CREF引脚接上一个10 nF的电容。AD7812的启动转换引脚convst,串行时钟引脚sclk,串行数据输入和输出引脚din、dout,同步发送和接收帧引脚tfs、rfs分别与FPGA通用I/O相连。

图5 AD7812与FPGA的电路连接图

3.2.2 A/D 转换控制模块

A/D转换过程的状态转移图如图6所示。

图6 状态转移图

通过上述有限状态[8]的转移来完成A/D转换的全过程。IDLE状态接收到有效信号strat,其中start为A/D的启动信号,由主程序产生;STRATN和CONVST状态控制了convst的电平变化低到高(其中低电平至少保持20ns);DELAY状态用来对convst电平变化延时2.3 μs,即92个 clk后启动转换,其中 clk来自FPGA内部晶振40 MHz;SCLK和RFS_TFS状态控制sclk电平变化低到高(其中低电平保持50 ns),分别置tfs和rfs的电平低到高、高到低;剩下状态用来控制sclk的下降沿,通过din引脚逐位写入操作A/D芯片的控制字符,并通过不同的字符来启动芯片内部电源和选择模拟信号的输入端口,sclk上升沿通过dout引脚逐位读出数据,数据转换完的同时产生FIFO写允许信号(wrreq)和写时钟信号(wrclk)。其中,AD7812转换的数据为16位,高10位有效,需要16个sclk,周期为100 ns,启动转换时间为 2.3 μs,整个 A/D 转换过程需要 3.9 μs完成,采样频率为251 kHz。

3.2.3 存储模块

如果利用AVALON总线边转换边读取,将消耗了Nios大量时间,也不能保证严格周期性的采样时间;单纯利用FPGA内部寄存器方式,则没有足够的存储空间;因此,为了满足A/D数据转换与存储器之间高速有效数据存储,通过异步FIFO[9-10]连接转换数据输出端口与数据读取端口。其中,FIFO数据输入端口与A/D转换数据输出端口相连,FIFO数据输出端口与Nios数据读取端口相连。

本文设计的异步FIFO位宽为16,深度(即FIFO可以存储16位数据的个数)为8 192。且FIFO缓存器配合A/D转换与指令读取进行写入与读出数据的过程如下:

写入时,在指令启动转换,等待外部触发出现后,开始连续的A/D转换过程。A/D转换每进行一次,向FIFO写进一个相应的转换数据,同时FIFO内部地址指针加1,直到满足缓冲区长度的数据采集要求。

读出时,在识别FIFO满空标志的条件下,逐个读取FIFO缓冲区的数据,每读一个数据,相应的控制线产生有效的读指针加1,完成FIFO的顺序读取。

3.2.4 同步控制模块

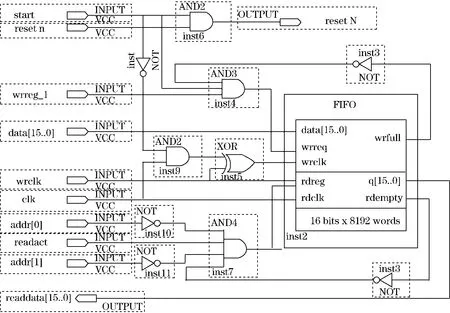

在Quartus_Ⅱ中设计实现同步数据采集接口控制模块原理图如图7所示。

在图7中,readdata、readact分别与AVALON总线相同命名的信号线相连;reset_n与AVALON总线中reset相连;start是启动A/D转换的信号线,为Nios主程序产生;clk是通过FPGA内部晶振40 MHz所得;wrreq_1和wrclk_1是由A/D转换模块产生,wrreq_1、start与wrfull共同控制FIFO的写请求信号wrreq,当start有效和wrfull为不满时,且wrreq_1为有效时,FIFO缓存器的写请求有效,否则为无效;wrclk_1、start和clk来控制FIFO的写时钟信号wrclk,其中wrclk_1是随着A/D转换的停止而停止,而start和clk是来让wrclk延续,为了让wrfull在读取一个数时变为无效;data是 A/D转换后的有效数据;readact、addr[0]、addr[1]、rdempty 共同控制 FIFO 的读请求,q 输出地址是0、wrfull的地址是1、rdempty的地址是2,这些地址位是Nios II中的自定义地址,地址偏移量是0到2,让偏移地址1(wrfull)和地址2(rdempty)为无效,为了保证rdreq为有效且q输出有效数据,并将q与wrfull、rdempty区分开来;reset_N与A/D转换模块的reset相连。

为了实现电流调制和软硬件的同步触发,利用Nios主程序产生一个有效信号给到FPGA,FPGA产生所需方波信号,通过I/O端口输给电流正负调制电路,再通过I/O口检测输入方波信号的下跳变,检测到下跳变时进入中断,产生一个有效start信号来启动A/D转换,同时也用来控制FIFO的写请求和写时钟,经过足够的时间后(T=3.9 μs),AD7812产生有效数据;同时输出写请求、写时钟信号,此时数据变为有效,此后在wrclk的上升沿将A/D转换器的数据读入FIFO。同时对FIFO的满标志进行判断,如果满标志有效,跳出中断,停止输入方波信号的产生,再将数据通过串口发送,发送完后等待下一次方波信号产生命令;如果满标志无效,则继续产生方波信号、进行A/D转换和数据存储。

图7 同步数据采集控制原理图

4 实验结果

在本实验中,注入激光器的电流周期T为10 ms,比对光路与测量光路进过光电转换后的信号作为被采集模拟信号的信号源,利用本系统将采集的8 192个数据的一部分进行显示。

如图8所示,依次为激光器电流信号、对比干涉信号、测量干涉信号。从电流正负调制开始同步进行数据转换,电流调制的2个周期对干涉信号采集了5 000个点,每个周期采集到的点数n为2 500个,每采集到一个数据点的时间为τ;本系统设计采样频率为251 kHz,采样时间为4 μs。则τ=T/n与本系统的采样时间一致,验证了该采集系统的有效性,满足高速采样的需求,有利于后面进行数据分析和处理。

图8 频率扫描干涉信号

5 结束语

本文设计了一种调制激光干涉系统的嵌入式数据采集方法,利用FPGA作为数据采集系统的控制核心,控制电流正负调制和软硬同步触发,通过软件变成控制硬件实现通道的选择。利用FPGA控制实现A/D转换,并给出控制转换状态图。利用FPGA内部16位的FIFO,实现了数据的缓冲存储,接口单元的写允许信号wrreq和写时钟信号wrclk充分利用系统资源,节约系统成本。利用上位机对转换数据的实时显示,验证该设计运行正常,完成可以满足信号高速采样的需求,为激光干涉系统的数据采集系统向智能行、便携式提供了条件,具有广泛的应用前景。

[1]王强,文丰,任勇峰.基于FPGA的高速实时数据采集存储系统.仪表技术与传感,2009(1):50-52.

[2]何元,张会新,刘波,等.基于FPGA的高速实时数据采集存储系统设计.仪表技术与传感器,2011(8):64-66.

[3]LI Z L,WANG X Z,BU P,et al.Sinusoidal phase - modulating laser diode interferometer insensitive to the intensity modulation of the light source .Optik,,2009,121(16):799 -803.

[4]WANG X F,WANG X Z,LIU Y M,et al.A sinusoidal phase - modulating fiber-optic interferometer insensitive to the intensity change of the light source .Opt Laser Technol,2003,35(3):219 -222.

[5]YANG H J,RILES K.High - precision absolute distance measurement using dual-laser frequency scanned interferometry under realistic conditons .Nucl Instrum Meth A,2007,575(3):395 -401.

[6]皮代军,张海勇,叶显阳,等.基于FPGA的高速实时数据采集系统设计.现代电子技术,2009,32(6):12 -14.

[7]王选择,张帅,翟中生,等.一种针对频率扫描测量系统的信号处理方法.计量学报,2013,34(6):513 -518.

[8]辛凤艳,孙晓晔.基于FPGA的AD转换控制器设计.中国科技信息,2012(5):78-79.

[9]熊洪兵,陈琦.基于FPGA的异步FIFO设计与实现.微计算机信息,2006,22(6):216 -218.

[10]罗先哲,张仁喆,付大鹏.基于FPGA的高速异步FIFO存储器的设计与实现.中国科技信息,2009,21(2):90-94.