声发射检测仪多路数据采集模块

王银玲,李华聪

(西北工业大学动力与能源学院,陕西西安 710072)

0 引言

保障现役飞机安全可靠飞行,延长其安全使用期限,首要任务就是要发现早期裂纹,通过早期预防性维护及修理。材料或者构件在外加载荷的作用下,其内部迅速释放能量而产生瞬态弹性波,这种现象称为声发射。声发射与常规无损检测技术相比有2个基本特点:一是对动态缺陷敏感,在缺陷萌生和扩展过程中能实时发现;二是声发射波来自缺陷本身而非外部,可以得到有关缺陷的丰富信息,检测灵敏度与分辨率高。因此,在飞机疲劳损伤检测中,声发射检测是一种重要检测手段。

为了得到较高的采样精度及传输速率,声发射测试仪器通常采用有线的传输方式,数据直接通过电脑的PCI插槽或者USB送至计算机。而在采样节点比较多,信道容量一定的情况下,必须降低采样速率;另外此类仪器只能测试相对物固定不动的目标,如果相对目标移动则无法测量;在现场条件恶劣的环境下,此类测量势必增加检测人员的劳动强度。为此本文设计一种基于FPGA控制的多路高速数据采集模块,将实时采集的数据存储到SDRAM中,等声发射事件结束后再将采集的数据通过无线方式发送出去。

1 总体设计方案

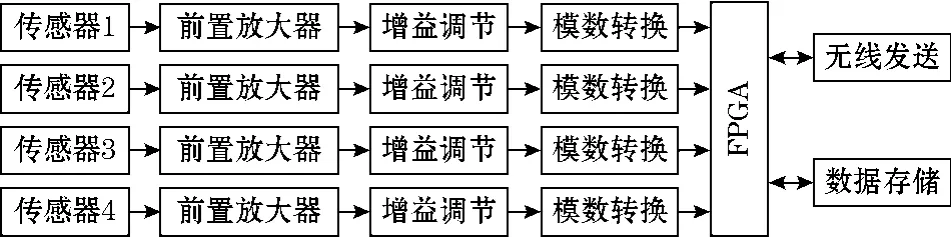

本设计要求传感器通道数为4路,带宽范围为100~300 kHz,采样分辨率不小于12 bit,各通道采样间隔时间不大于1 μs。声发射检测仪整体设计思想为:首先由传感器探头将弹性波信号变为微弱的电信号,再将该电信号进行放大处理,经放大后的信号为交流信号,需要再通过增益调节转变为一定幅值的直流信号;其次直流信号经过A/D转换转为数字量,再通过总线存入SDRAM中;最后等一个声发射时间结束后,将SDRAM中的数据通过无线方式送到上位主机,再对这些数据进行分析处理,整体模块设计框图如图1所示。

图1 声发射整体模块框图

2 系统的硬件设计

声发射信号的频率分布与材料或构件的具体特性有关,其范围可从次声波到超声波,使用频率在20 kHz~2 MHz之间。由于本设计针对金属构件,而裂纹的声发射信号检测的使用频率范围在100~300 kHz之间。针对这一点,检测系统选用频带在50~200 kHz的声发射传感器R15A,该传感器谐振频率为75 kHz,适合在高灵敏度的检测场合中使用。前置放大器选用1220系列,其可分为高通、低通及带通3种规格,根据检测目标的实际情况,最终选择增益20 dB、40 dB和60 dB可调,频率范围100~300 kHz,具有单端和差动两种输入方式(本设计选择单端方式),+28 V(0.2 A)DC供电型号为1220-100-300BP的带通前置放大器。

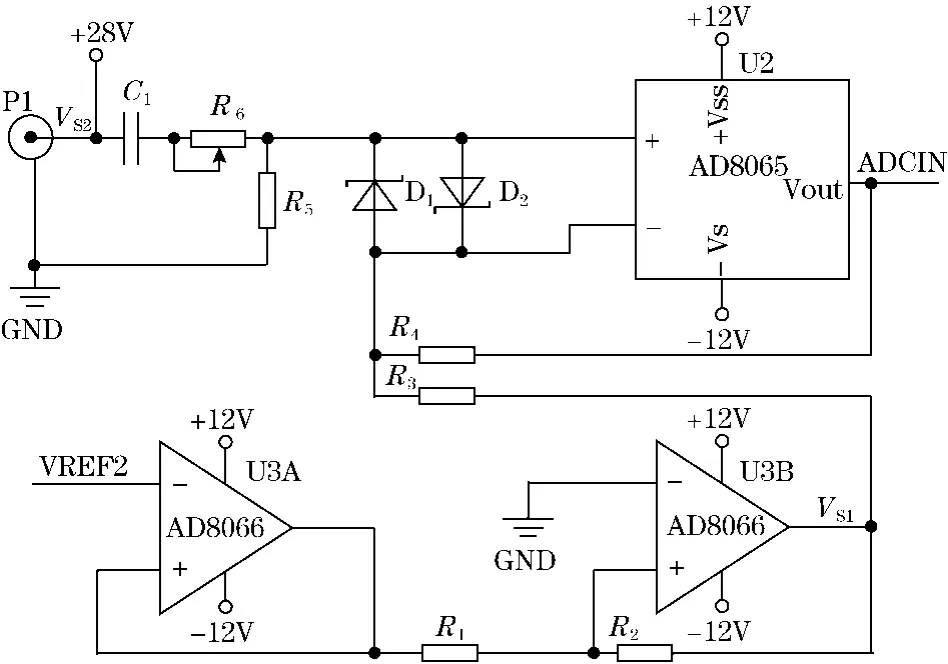

2.1 增益调节电路

经过前置放大输出信号的幅值在±10 V范围,所以要通过增益调节电路对其幅度进行调制,将±10 V的信号调制为一个直流电压信号。调制电路如图2所示,C1为隔直电容,VREF2为系统+2 V的参考电压,先通过前一级运放AD8066经过增益为1的电压跟随,然后再通过后一级运放AD8066进行翻转,输出-2 V的参考电压,最后将前置放大信号与-2 V的参考电压通过AD8065进行差分运算。在此电路图中,AD8065的3、4引脚压差可忽略不计,稳压二极管D1、D2起限压保护作用,经过AD8065放大后的输出电压计算公式如式(1)。通过电路图可得,要将输出信号 的范围设置在1~3 V,取R3、R4、R5为1 kΩ,R6为19 kΩ,其满足电路要求,R6为可变电阻,可以动态调节增益,而输出计算公式为

图2 增益调节电路

2.2 模数转换电路

通过增益调节将±5 V信号转变为1~3 V,接下来要进行A/D转换。由于放大器的范围为100~300 kHz,根据奈奎斯特采样定理和探头探测声发射信号的频率范围,则要求A/D的采样频率为600 kHz或以上,为了使重构信号波形完美,根据实际经验,A/D采样频率选择 2.5 MHz。A/D转换芯片选用AD9226,为单路数据转换,其采样精度为12 bit,最高采样速率为65 MSPS。A/D转换电路如图3所示。

图3 A/D转换电路

AD9226的1脚为FPGA发送的时钟信号,VINA和VINB为模拟量输入端,在本设计中采用单端输入模式,增益调节后的信号ADCIN通过33 Ω的电阻接入AD9226的23脚作为输入信号。AD9226的24脚通过33 Ω电阻接入VREF,电阻R11、R12起限流作用。AD9226的SENSE引脚接地,VREF输出2 V的标准电压;OTR引脚为信号幅值检测端,当AD9226输入信号幅值超出输入范围时将输出高电平1;通过MODE引脚设置输出数据格式,本设计接地则输出数据为二进制格式,BIT1~BIT12为输出的二进制信号。

由于多路ADC同时采集,要求各通道采样间隔时间不大于1 μs,直接通过MCU控制不能达到要求,因此在数字电路部分添加了可编程逻辑器件用于ADC采样时序控制与数据缓存,可编程逻辑器件可以真正实现各通道的并行同步采样。

2.3 FPGA及外围存储电路

可编程逻辑器件采用EP2C8Q208C8,此芯片是整个模块的核心,采用PQFP的封装形式,有208个引脚。EP2C8Q208C8的外部时钟源为50 MHz,可以通过PLL进行倍频。由于在A/D转换电路中选择AD9226的28引脚SSOP封装结构,优点是引脚较少,布线方便。但AD9226没有片选使能位,所以4路A/D转换中AD9226的输出引脚不能采用总线方式,需要占用较多的EP2C8Q208C8引脚资源,而好处是FPGA可以实现真正意义上的4路信号同步采集,达到零延时。

通常在数据吞吐量大的地方采用FIFO以实现数据缓冲,这种结构又称为乒乓结构。乒乓结构是一种典型的用于数据流控制的处理技巧,它通过对输入输出地址线的操作分别对输入输出数据块进行切换,把经过缓冲结构的数据不停留地送到后续单元进行传输或运算等处理。整个乒乓结构作为一个整体,对于输入数据流和输出数据流都是连续不停顿的,符合流水线处理的思想。但是数据采集速率只有2 MHz,而FPGA读写SDRAM的能力在正常工作时可以达到100 MHz,所以没必要添加FIFO,另外在一些数据量大的情况下,可以通过QuartusⅡ软件基于SOPC快速建立片内FIFO。

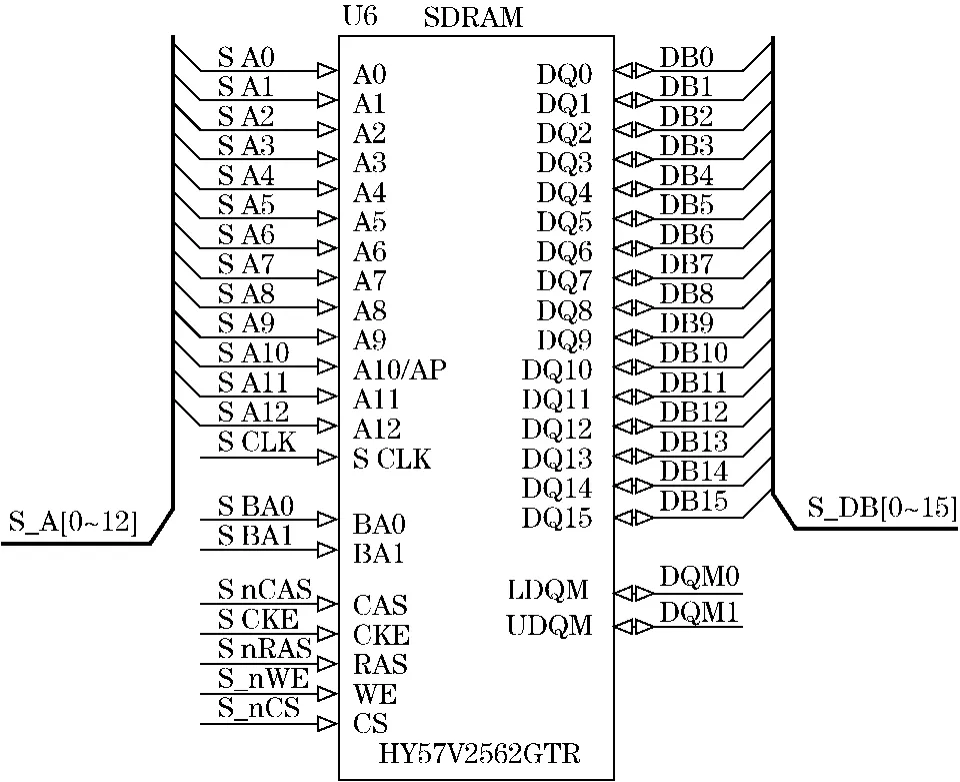

数据暂存单元选择SDRAM,其型号为HY57V2562GTR,容量 256 Mbit(16 M ×16 bit)、16 bit总线,工作频率133 MHz。本设计给其时钟引脚频率选择2倍频,也就是100 MHz。SDRAM在整个FPGA系统中扮演的角色相当于电脑中的内存条,是整个FPGA的缓存区,既存储FPGA运行时的程序,也存储A/D转换后的数据。SDRAM的连接方式如图4所示,S_A[0~12]为地址线接口,BA0和BA1为SDRAM的bank存储选择位;S_DB[0~15]为16位数据线接口。

2.4 网络接口电路

采集的数据需要通过以太网无线发射出去,EP4CE6F17C8可以通过SOPC配置网络接口,本设计网口芯片采用ENC28J60。ENC28J60是28引脚独立以太网控制器。目前市场上大部分以太网控制器的封装均超过80引脚,而符合IEEE 802.3协议的ENC28J60只有28引脚,既能提供相应的功能,又可以大大简化相关设计,减小板载空间。

图4 SDRAM接口

以太网接口电路如图5所示,ENC28J60的工作频率为25 MHz,晶振连接在OSC1和OSC2引脚之间。在差分接收引脚(TPIN+/TPIN-)上,需要一个专用于10BASE-T操作的1:1脉冲变压器;在差分发送引脚(TPOUT+/TPOUT-)上需要外接一个带有中心抽头的1∶1脉冲变压器,变压器应具有2 kV以上的电压隔离性能,来防止静电干扰。两个变压器均需要额外的2个50 Ω(精度1%)的电阻和1个0.01 μF的电容与特定端相连;由于ENC28J60内部模拟电路的需要,在RBIAS引脚与地之间接一个2 kΩ(精度为1%)的电阻。

图5 以太网接口电路图

3 软件设计及测试

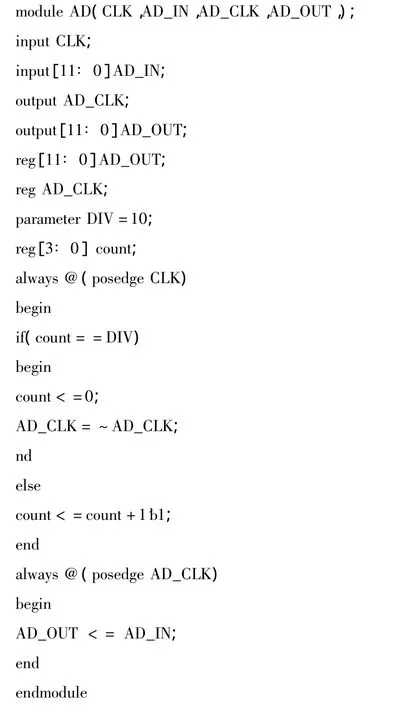

在整个数据采集模块中,核心控制功能通过FPGA完成,软件开发采用QuartusⅡ11.0开发环境。由于该模块放大、滤波以及增益调节已通过硬件完成,所以软件设计只需要从模数转换开始。由于FPGA采用的是一种模块化设计思想,各模块系统具有独立性及非时序性,使得完全意义的并行处理成为可能。本设计共计4路模拟输入,要求A/D采样精度12 bit,相互通道采样时间精度间隔1 μs以内。A/D采样4路独立输入,所以系统可以实现真正的零延时。首先要对A/D转换建模,AD9226给一个外部时钟信号,则进行一次A/D转换。对A/D转换模块1的建模程序如下所示,CLK为外部时钟源信号,本设计为50 MHz;AD_IN为AD转换得到的12 bit数据;AD_CLK为模数转换时钟信号,由于本设计采样最高频率为300 kHz,所以根据采样定理及实际经验,最终采样频率取2.5 MHz,所以要进行20倍分频。由于要对SDRAM以及网络接口控制,所以利用SOPC建立软核,SDRAM工作频率为100 MHz,需要通过PLL倍频,建立 PLL可以使外部时钟实现真正意义上的一致,SDRAM的读写与以太网接口软件设计请查阅相关资料。A/D转换建模如下所示,其余3个A/D模块与其类似:

AD_OUT输入到SignalTap中A/D转换的采集信号,Signal-TapⅡ是一款功能强大且极具实用性的FPGA片上debug工具软件,它集成在FPGA开发工具QuartusⅡ中,通过其实现软件调试。通过数字信号发生器给一个频率300 kHz,幅度为5.0Vpp的正弦信号,在通道0上通过SignalTap仿真输出的时序图如图6所示,可以看出采集的数据波形与输入相吻合。

图6 A/D转换功能仿真结果

4 结束语

目前在仪表检测及工业控制领域,多路数据采集系统的应用非常广泛。为了得到信息的细小特征,高采样速率、高精度将是数据采集的发展方向。本文介绍的多路数据采集模块,通过FPGA控制模数转换,实现了数据的高速采样、高精度、零延时这一声发射检测系统要求。此外,对该模块进行简单的修改,还可以应用于智能仪表数据采集、自动化设备检测中。

[1]岳丹,宋克非,张佩杰,等.高精度多通道数据实时采集与监控系统.仪表技术与传感器,2014(6):93-95.

[2]吴继华,蔡海宁,王诚.Altera FPGACPLD设计(高级篇).北京:人民邮电出版社,2011.

[3]徐洋,黄智宇,李彦,等.基于Verilog HDL的FPGA设计与工程应用.北京:人民邮电出版社,2009.

[4]Cyclone II Device Handbook.pdf.http://www.altera.com/,2007.

[5]H57V2562GTR Series(Rev0.1).pdf.http://www.hynix.com,2009.