基于噪声抵消技术的射频宽带低噪声放大器设计

韩冰杰, 张晓林, 申 晶

(北京航空航天大学电子信息工程学院 北京 100191)

引 言

低噪声放大器是射频接收机前端的第一级电路,它直接将天线耦合接收到的微弱信号进行放大,并将放大后的信号传递给其他电路进行处理。低噪声放大器的特殊位置决定了它在接收机中的重要性。

对于工作在多频段的射频接收机,一般采用多个相互独立的窄带低噪声放大器并行工作,这将不可避免地提高电路的复杂度,同时增加成本。本文的双频双系统导航接收机选用宽带低噪声放大器,降低了系统的复杂度及成本。

为实现低噪声放大器在工作频段内的输入阻抗匹配,常使用以下几种宽带匹配结构:电阻反馈共源结构、源极电感负反馈共源结构、分布式结构和共栅结构等。由于共栅结构仅需引入一个外加电感,即可实现较宽频带上的输入阻抗匹配,故被广泛应用在宽带低噪声放大器的设计当中。

一般而言,窄带系统的输入阻抗匹配性能要优于宽带系统,而阻抗匹配性能将直接影响噪声性能的好坏。因此,对于宽带低噪声放大器,需要采用噪声抵消技术来弥补阻抗匹配性能导致的噪声性能下降。噪声抵消技术的主要思想是,在原有电路的基础上增加一条新的路径,使有用信号通过两条路径后同相叠加,有用信号能量得到增强,而噪声信号在路径的输出端被反相抵消。

本文采用共栅结构设计了一款宽带低噪声放大器LNA(Low Noise Amplifier),并采用噪声抵消技术降低噪声系数,该LNA在1GHz~2GHz工作频带内的最大噪声系数为3.63dB。

1 电路设计

1.1 输入阻抗匹配

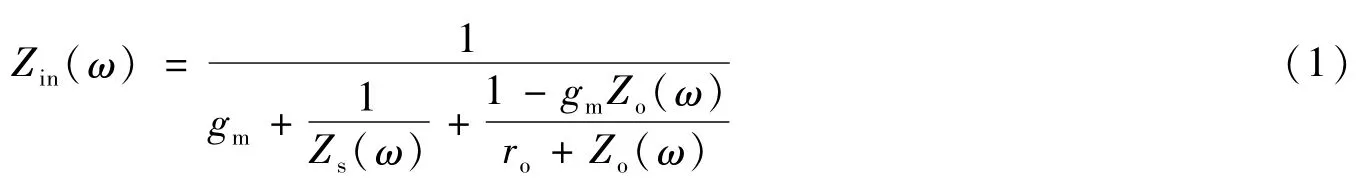

低噪声放大器作为射频接收机的第一级电路,必须实现输入阻抗匹配,降低反射系数。共栅结构具有良好的宽带阻抗匹配特性,可在较宽工作频带上实现50Ω的输入阻抗匹配。图1给出了共栅结构的原理图和小信号等效电路。

图1 共栅结构的原理图和小信号等效电路Fig.1 Schematic diagram and small-signal equivalent circuit of common-gate architecture

图1(a)中,ZL是共栅结构的漏极负载,Ls与NMOS管M的栅源电容Cgs构成并联谐振电路,以实现输入阻抗匹配。对图1(b)所示的小信号等效电路进行分析,同时考虑下一级电路的输入阻抗Zin1,可得到共栅结构输入阻抗的表达式为[1]

图1(b)中,假设构成Zs(ω)和Zo(ω)的电容和电感Q值很高,可将二者分别表示成实部和虚部相加的形式。其中Zs仅由Ls和Cgs构成,表现为纯电抗。令

将式(2)和式(3)代入式(1)并化简,可得

由式(4)可以看出,由于电路工作在1~2GHz,Zin(ω)的虚部主要取决于Xs(ω),Xo(ω)的影响不大。为使Zin(ω)匹配到50Ω附近,需要调整晶体管M的沟道尺寸和工作点,使gm值约为20mS,还需调整Ls值,使其与Cgs构成的并联电路谐振在工作频带的中心频点。

1.2 噪声抵消

共栅结构电路简单,其噪声主要来源是MOS管的热噪声,而晶体管的热噪声主要在沟道中产生。对于工作在饱和区的长沟道晶体管,可将此噪声源模拟成一个横跨在源极和漏极之间的电流源[2]。

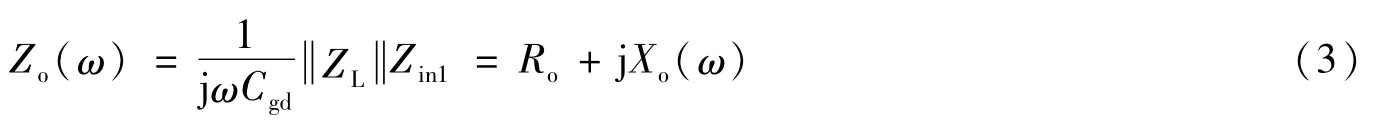

图2为共栅结构的噪声抵消原理图,图中晶体管M1为共栅放大电路,In,M1等效为M1的沟道热噪声源,M2和M3分别构成两个共源放大电路,噪声电流源In,M1分别在负载电阻RL和电源内阻Rs上产生两个大小不等、相位相同的压降,使得M2和M3的栅极电压相位相反,从而产生反相的漏极电流In,M2和In,M3,叠加后得到的输出噪声电流In,out减小,达到削减噪声的目的。

对噪声抵消电路的具体参数进行推导,使得In,M2和In,M3在输出端完全抵消,即In,out=0[3]

可得噪声完全抵消条件为Rsgm3=RLgm2。

图2 共栅结构的噪声抵消原理Fig.2 Schematic diagram of noise canceling in common-gate architecture

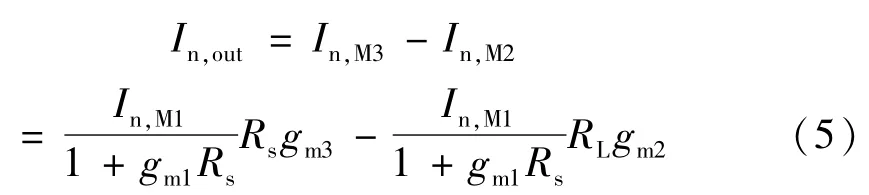

2 噪声优化设计

综合以上两种技术,设计基于噪声抵消技术的宽带低噪声放大器,电路原理图如图3所示,图中M1是共栅结构,源极电感Ls与M1的栅源电容Cgs1决定电路的输入阻抗匹配,M2和M3为两个共源结构,共同构成了M1的噪声抵消电路。

假设图3所示电路输入阻抗匹配良好,且噪声抵消结构可以完全消除M1的沟道热噪声,此时电路中的噪声主要是R1、R2和M2、M3的热噪声。由于R2阻值相对MOS管的输出电阻较小,其热噪声可忽略不计。要尽可能降低电路的噪声系数,可以调整R1的阻值和MOS管M2、M3的尺寸。但这些改变不可避免地会影响电路的增益、功耗等其他性能,因此需要在电路设计过程中找到合理的折中点,在实现噪声优化的同时,满足系统的整体性能要求。

图3 基于噪声抵消技术的LNA原理Fig.3 Schematic diagram of the proposed LNA based on noise canceling technology

2.1 沟道宽度优化

2.1.1 M2沟道宽度优化

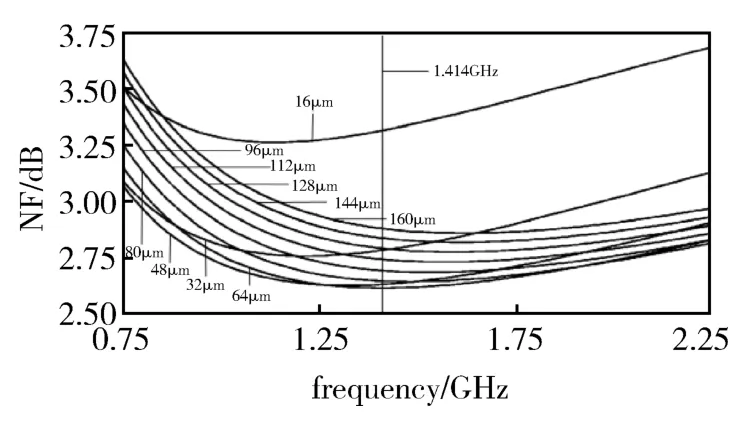

为实现具有优异噪声性能的LNA,对电路中以R1、M2、M3为主的各元器件参数进行优化设计。设计中发现,MOS管M2沟道宽度的改变会对噪声系数曲线产生较大的影响,其变化规律如图4所示。

选取图4中各噪声系数曲线中心频点1.414GHz对应的NF值,绘制如图5所示的中心频率噪声系数随M2沟道宽度变化的曲线图。由图5可知,M2的沟道宽度应在48μm~64μm之间选取。

图4 NF随M2沟道宽度的变化Fig.4 NF with different channel widths of M2

图5 中心频点NF随M2沟道宽度的变化曲线Fig.5 NF at center frequency versus channelwidth of M2

2.1.2 M3沟道宽度优化

由1.2节可知,为使M1的沟道热噪声完全抵消,M3应具有较大的跨导值gm3。在gm3增大过程中,电路会逐步逼近噪声完全抵消条件,但同时会使M3的漏极电流增加,带来功率损耗的大幅上升。因此,M3沟道宽度的选取要综合考虑噪声性能和功率损耗。

2.2 负载优化

随着负载RL阻值的增大,电路主放大结构的漏极电流减小,电路整体噪声系数降低。但RL阻值的改变会引起M1直流工作点和跨导的变化,影响电路的输入阻抗匹配。对负载RL的阻值进行优化,仿真得出不同的RL值对应的输入反射系数曲线,如图6所示。

选取图6中各输入反射系数曲线的最高点,绘制如图7所示的S11最大值随RL阻值变化的曲线。为实现电路的噪声优化,选取图7中S11max在-10dB左右对应的最大负载值,约825Ω。

图6 S11随R L阻值的变化Fig.6 S11 with different R L values

图7 S11最大值随R L阻值的变化曲线Fig.7 Maximum S11 versus R L value

以上述噪声优化得到的参数为基础,对电路中其他元器件的参数进行调整,可以得到LNA的具体参数,如表1所示。

表1 LNA的参数选取Table 1 Parameters of the proposed LNA

2.3 版图设计优化

设计图3所示低噪声放大器电路对应的版图,依据后仿结果对电路参数进行调整,得到LNA的最终参数,如表2所示。

表2 LNA的最终参数选取Table 2 Final parameters of the proposed LNA

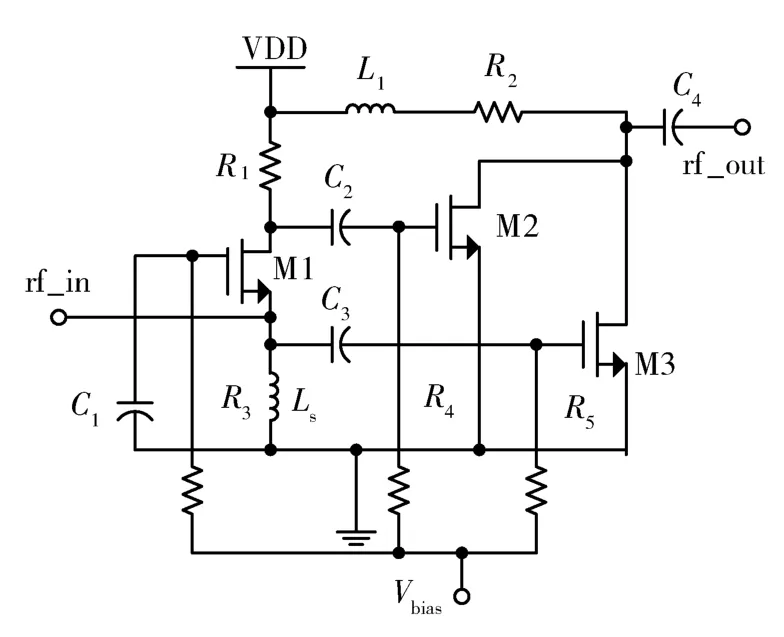

本文设计的低噪声放大器应用于接收机射频前端,工作频率比较高,寄生效应对电路影响很大。为尽可能减小版图后仿结果与电路前仿结果的差异,本文设计带有PAD的宽带低噪声放大器,其核心电路版图如图8所示。

为减小信号干扰对电路的影响,版图采用左右对称设计。本设计将电路中三个NMOS管分别拆分成两个等尺寸小单元的并联,在版图中对称放置;在参数选择过程中,将四个耦合电容设置成两两数值相等;布线及PAD的放置也尽可能地满足电路的对称性。

本设计在版图外围采用双层电源环进行保护,以减小信号串扰和衬底噪声对电路噪声系数的影响。

图8 带有PAD的LNA版图Fig.8 Layout of the proposed LNA with PAD

3 仿真结果

本文中低噪声放大器采用SMIC 0.18μm 1P6M RF CMOS工艺实现,设计与仿真均使用Cadence软件完成。LNA的噪声系数仿真结果如图9所示,输入反射系数仿真结果如图10所示,功率增益仿真结果如图11所示,1dB压缩点仿真结果如图12所示。仿真结果显示,该宽带低噪声放大器在1GHz~2GHz工作频带内,输入1dB压缩点在1.414GHz处为-6.93dBm,输入反射系数S11小于-10dB,噪声系数NF小于3.63dB,功率增益S21大于7.49dB,在1.8V电源电压下,主体电路功耗为18.8mW。

图9 噪声系数仿真结果Fig.9 Simulation result of the noise figure

图10 输入反射系数仿真结果Fig.10 Simulation result of the input reflection coefficient

图11 功率增益仿真结果Fig.11 Simulation result of power gain

图12 1dB压缩点仿真结果Fig.12 Simulation result of the 1dB compression point

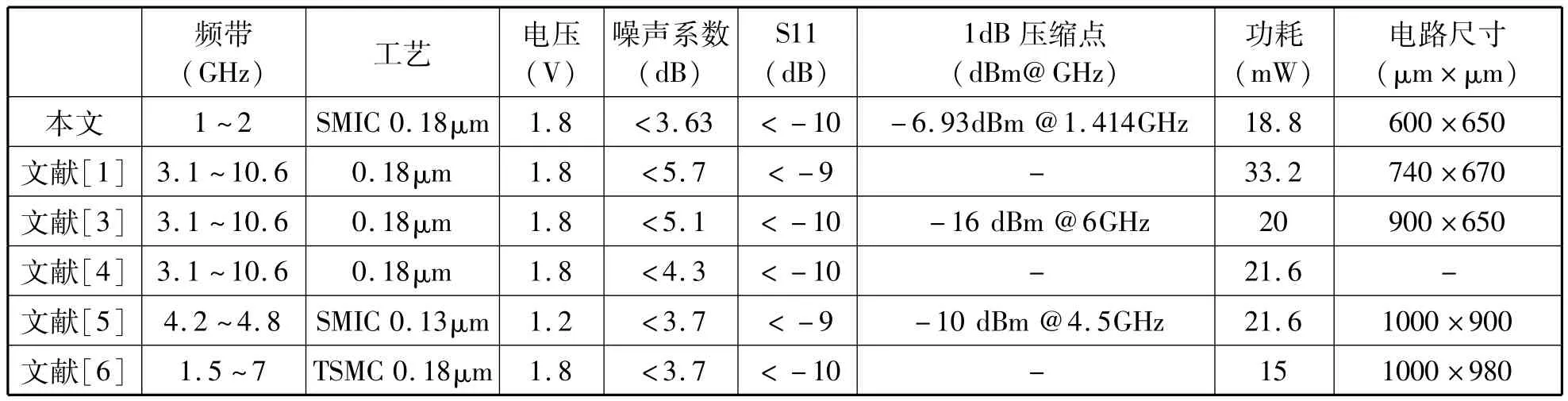

表3给出了本文设计的低噪声放大器与其他低噪声放大器的性能对比,可以看出本文设计的LNA具有良好的输入阻抗匹配特性和较高的线性度,并实现了较低的噪声系数。

表3 本文LNA与其他LNA性能对比Table 3 Performance comparison of the proposed LNA and other reported LNAs

4 结束语

本文采用共栅结构,利用噪声抵消技术,设计了一款可工作在1GHz~2GHz频带内的宽带低噪声放大器。该低噪声放大器电路复杂度较低,具有良好的输入阻抗匹配特性和较高的线性度,并且噪声系数较低,可广泛应用于航空航天领域的射频接收机。

[1]Lu Y, Yeo K S, Cabuk A, et al.A Novel CMOS Low-noise Amplifier Design for 3.1-to 10.6-GHz Ultra-wide-band Wireless Receivers[J].Circuits & Systems I Regular Papers IEEE Transactions on, 2006, 53(8):1683 ~1692.

[2]Thomas H Lee.CMOS射频集成电路设计[M].余志平,译.第二版.北京:电子工业出版社,2004:37~38.Thomas H Lee.The Design of CMOS Radio-frequency Integrated Circuits[M].Yu Zhiping, translate.Second Edition.Beijing:Publishing House of Electronics Industry,2004:37~38.

[3]Liao C F.A Broadband Noise-canceling CMOS LNA for 3.1-10.6-GHz UWB Receivers[J].IEEE Trans.on Solid-State Circuits,2007,42(2):329~339.

[4]徐国明.基于0.18μm工艺CMOS超宽带低噪声放大器设计[J].电子与封装,2011,11(4):31~34.Xu Guoming.Design of an Ultra Wideb and Low Noise Amplifier Based on 0.18 μm CMOS technology[J].Electronics&Packaging,2011,11(4):31~34.

[5]Chen FH, Lin SY, Li L Y, et al.4.2-4.8 GHz CMOS Variable Gain LNA for Chinese UWB Application[C]//Microwave and Millimeter Wave Technology(ICMMT),2010 IEEE International Conference on.Chengdu:IEEE,2010:1922~1924.

[6]Hung W H, Lin K T, Hsieh JY, et al.A 2-6GHz Broadband CMOS Low-noise Amplifier with Current Reuse Topology Utilizing a Noise-shaping Technique[C]//Circuits and Systems(ISCAS), 2011 IEEE International Symposium on.Rio de Janeiro:IEEE,2011:1291~1294.