基于FPGA的IRIG-B(DC)时码解码设计

郗海燕,王 娟

(中国电子科技集团公司第39研究所 陕西 西安 710065)

基于FPGA的IRIG-B(DC)时码解码设计

郗海燕,王 娟

(中国电子科技集团公司第39研究所 陕西 西安 710065)

IRIG-B(DC)码为普遍应用于航天测控领域的一种标准时间码,测控系统内的设备单元需要从IRIG-B(DC)码中解调出时间信息,传统的IRIG-B(DC)解码单元大多采用单片机来实现,结构复杂,易受干扰,文中提出了一种基于FPGA技术的IRIG-B(DC)解码设计方案及详细的设计方法,用MAX+plus II仿真软件对该解码设计进行仿真,并应用工程实例验证该设计的正确性。仿真及工程应用结果表明该设计能准确地从IRIG-B(DC)码中提取时间信息,该设计具有器件少、结构简单、设计灵活、解码精度高、可靠性高等特点。

IRIG-B 码;串行码;FPGA;解码;VHDL

航天测控系统在对航天器进行测量及控制时,时统设备使航天测控系统在统一的时间尺度下工作。时统设备的功能就是使本地时间与标准时间在一定同步精度范围内保持一致并按工程任务要求的标准码制对时间信息进行编码。纵观我国及国外的时间码应用情况,IRIG-B格式时间码(简称B码)是目前应用最为普遍和广泛的一种标准时间码[1]。IRIG-B格式时间码分IRIG-B(DC)和 IRIG-B(AC),文中详细地介绍 IRIG-B(DC)码的时间信息基于FPGA的一种解调方法。

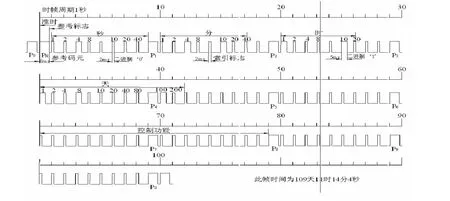

图 1 IRIG-B(DC)码波形图Fig.1 Waveform of IRIG-B(DC)

1 IRIG-B(DC)码

IRIG-B(DC)码为一串行码,每秒一帧,每帧包括100个码元,每个码元的宽度为10ms。码元中包含秒、分、时、天及控制功能等信息。IRIG-B(DC)码的示意图如图1所示[2]。

1.1 IRIG-B(DC)码时间信息解码

IRIG-B(DC)码时间信息解码单元的主要功能是从IRIG-B(DC)码源中提取出积日、时、分、秒、豪秒等时间信息,并形成1 Hz、20 Hz、40 Hz等各种同步脉冲信号,根据需要显示并送至需要时间信息的各设备单元。传统的IRIG-B(DC)解码器大多采用单片机来实现,器件较多,结构复杂,在受到外界干扰的情况下还可能出现死机等故障。而基于FPGA技术的IRIG-B(DC)码时间信息解码方案具有硬件设计简洁、调试灵活方便、运行稳定可靠及解码精度高等特点,同时,为了充分利用芯片资源,节省硬件设计,时码解码功能通常与其他功能集成设计在同一FPGA芯片上。

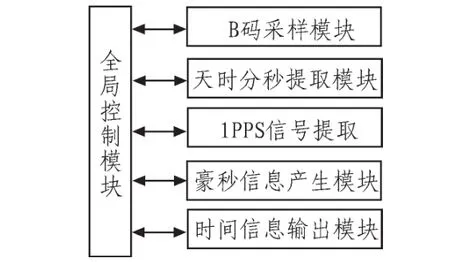

IRIG-B(DC)码时间信息解码方案示意图如图2所示。

图2 IRIG-B(DC)码时间信息解码方案示意图Fig.2 Schematic diagram of IRIG-B(DC)decoder

IRIG-B(DC)码时间信息解码的重点和难点是如何在IRIG-B(DC)串行码中准确提取秒同步信号 (即跳秒的时刻),以保证时间信息的精确度及准确度。该IRIG-B(DC)码解码机理是根据IRIG-B(DC)码串行码的格式和原理使用状态机和计数器来实现完成的,其中会涉及到多个时钟信号,这些时钟信号都是由FPGA外部的20 MHz晶体形成的。其软件设计模块的基本框图如图3所示。

图3 IRIG-B(DC)码时间信息解码单元软件设计框图Fig.3 IRIG-B(DC)decoder software block diagram

时间信息的解码及提取具体方法是将一20 MHz的标准频率信号作为时钟信号接入FPGA,标准频率信号的选择是依据不同的测控体制及测控精度对时间同步精度的要求来确定的。依据IRIG-B(DC)码的特征,在输入时钟信号的每个上升沿判断IRIG-B(DC)码码元高电平持续的时间。当出现连续两个8 ms宽高电平的码元(P0和PR)时开始提取秒信息,在秒信息码元中,码元高电平宽度为5 ms时代表二进制‘1’,2 ms时代表二进制‘0’和索引标志,秒值就每个码元代表的二进制值与其权值乘积之和。图1中每个码元上方的数字就是此码元的权值。在码元P1出现后,开始提取分信息。时和天信息的提取方法依此类推。FPGA在P5出现后将其解出的天、时、分、秒等时间信息输出,存储到数据缓冲器以便读取。

豪秒信息的产生根据数据信息中对豪秒数据的需求有两种产生方法,一种方法是设计一脉冲计数器,根据记录的脉冲数量,形成豪秒数。另一种较为精确的毫秒产生的方法是利用 的时钟信号设计一与秒同步信号同步的时间计数器,该方法形成的毫秒计数器精度高、抗干扰能力强。

为提高设备的可靠性,增强系统的抗干扰能力,考虑到B码源及20 MHz时钟源的准确度,在测量码元高电平宽度的程序设计中必须加入容错设计及输入信号的数字滤波设计,容错范围控制在±5%,同时判断正常脉冲信号的时,舍弃杂波信号及干扰的尖峰脉冲。

1.2 IRIG-B(DC)码时间解码单元的详细设计

本设计采用了VHDL语言,运用自顶向下的设计方法,实现了工程的层次化管理[3]。为了使得设计稳定、可靠,采用全同步设计方法,使整个工程都在一个时钟上升沿时刻改变状态,这样可以避免冒险和其他不定态的出现。

程 序 中 涉 及 的 变 量 有 :current_level,prior_level,cnt,sub_cnt,count,prior_pulse_width,second_buf,minute_buf,hour_buf,date_buf等,由FPGA外部20 MHz时钟源分频出的10 MHz为解码程序的敏感量。

各变量具体解释如下:

2 仿真结果

根据上述设计,运用MAX+plus II仿真软件对IRIG-B(DC)码解码进行仿真,设计输入分别为正常的IRIG-B(DC)码及混有杂波的IRIG-B(DC)码。其仿真结果如图4、5所示。

图4 IRIG-R(DC)解码仿真波形Fig.4 Simulation waveform of IRIG-B(DC)decoder

图5 混有杂波的IRIG-B(DC)解码仿真波形Fig.5 Simulation waveform of IRIG-B(DC)with noise wave decoder

图4是正常IRIG-B(DC)码得解码仿真图,从图4的仿真结果可以看出,该程序可以准确地从IRIG-B(DC)码中提取时间信息。

由于IRIG-B(DC)码时间解码程序设计中包含有容错设计及软件滤波器设计,可防止由于码元中混有杂波而引起的误解码。图5是码元中混有杂波时的解码仿真图。从图5的仿真结果中可以看出,在30 ms和40 ms之间出现的杂波信号并没有引起FPGA内部状态机的切换。

依据仿真效果,可以得出该设计完全能准确地从IRIGB(DC)码中提取时间信息。

3 结束语

上述详细介绍了一种基于FPGA的IRIG-B(DC)码解调方案及设计实现方法。文中介绍的实现方法已经得到成功应用,并应用于多种测量站的实时控制设备中。工程应用结果表明该实现方法具有简单实用、精度高、抗干扰性强及可靠性高等特点。

[1]陈芳允.卫星测控手册[M].北京:科学出版社,1996.

[2]童宝润.时间统一系统[M].北京:北京国防工业出版社,2007.

[3]徐志军,徐光辉.CPLD/FPGA的开发与应用[M].北京:电子工业出版社,2002.

[4]王彦.基于FPGA的工程设计与应用[M].西安:西安电子科技大学出版社,2007.

[5]姜雪松 刘东升.硬件描述语言VHDL教程[M].西安:西安交通大学出版社,2004.

[6]王辉.MAX+plus和QuartusⅡ应用与开发技巧[M].北京:机械工业出版社.2007.

Design of decoding IRIG-B(DC)based on FPGA

XI Hai-yan,WANG Juan

(The 39th Institute,Electronic Science and Technology Group Corporation of China,Xi′an 710065,China)

IRIG-B(DC)code is a standard time code,which is widely used in the aerospace measurement and control area.The equipment unit in the control system need to demodulate time information from IRIG-B(DC).The normal IRIG-B(DC)decoder is mostly designed based on microcontroller system,its configuration is complex and easy to be interferred.A new design of decoding IRIG-B(DC)by programming on FPGA is presented in this paper.The simulation of the decoder design using MAX+plus II simulation software is alao given.The design is proved to be corrent and effective in many applications.The results have demonstrated that the design can precisely demodulate time information from IRIG-B(DC),and the design is simple,flexible,highly reliable and highly precisie.

IRIG-B timing-code;seral code;FPGA;decode;VHDL

TN92

A

1674-6236(2014)13-0182-02

2013-09-16 稿件编号:201309122

郗海燕(1968—),女,陕西蓝田人,高级工程师。研究方向:伺服系统控制与微电子技术应用。