一种应用于时间交织模数转换器的低抖动延迟锁定环

汪雨雯,叶 凡,任俊彦

(复旦大学专用集成电路与系统国家重点实验室,上海201203)

模数转换器(Analog-Digital Converter,ADC)是混合信号系统中必不可少的关键模块,其性能好坏直接影响到整个系统,时间交织ADC作为高速高精度ADC的一种实现方案被广泛应用,该方案使用多路ADC并行对输入信号进行转换,子ADC的采样时间均匀错开,系统在整体上等效为一个高速的模数转换器.应用时系统需要给子ADC提供多路均匀相位的时钟控制信号,这些时钟控制信号通常由锁相环(Phase-Locked Loop,PLL)和延迟锁定环(Delay-Locked Loop,DLL)提供,其中DLL常用于纠正片外时钟偏移,PLL常用于片内分布时钟的同步[1-2].

由于PLL系统的特性,环路参数对工艺、温度十分敏感,因此稳定性较低,此外PLL结构中必需的压控振荡器会引入额外的抖动并在环路中累加,对PLL的输出相位噪声造成影响.而在DLL结构的时钟发生器中,压控延时链取代了压控振荡器,与PLL相比,DLL没有压控振荡器引入的附加噪声,因而有更好的噪声性能,同时结构的改变也使得DLL的环路更容易稳定.但是,传统DLL中非理想鉴频鉴相器(Phase Frequency Detector,PFD)和电荷泵(Charge Pump,CP)带来的静态相位误差,会在DLL结构的时钟发生器中产生固定抖动.常见的解决方案是在电荷泵中引入校准电路[3],或是带误差检测的反馈回路[4],但这些做法并不能有效地消除静态相位误差,实现代价也很高.本文针对这一问题提出了一种切换型鉴频鉴相器,通过定时切换鉴频鉴相器中的信号通路,大幅减小了DLL结构中的静态相位误差,优化了环路的抖动性能.

1 时间交织ADC中的时钟

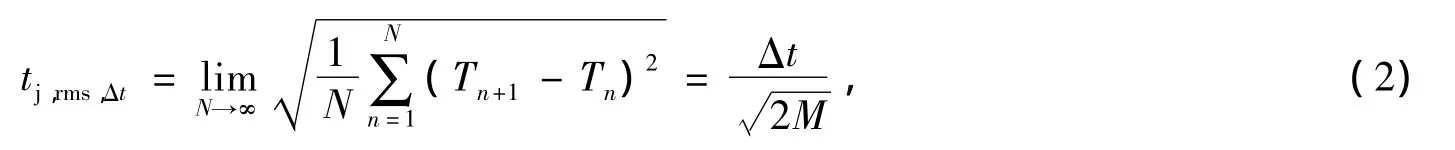

在时间交织模数转换器中,用多路子ADC并行对输入信号进行转换,对于包含M路的时间交织ADC,需要提供M个依次相差2π/M相位的子时钟(图1).实现高精度转换的关键在于保证通道间采样时钟信号相位的均匀性,采样时间信号与理想时钟信号之间的误差越小,ADC的有效位数(Effective Number of Bits,ENOB)越高.通常用孔径抖动(Aperture Jitter)来描述这项性能,文献[5]中给出了时钟抖动与时间交织ADC有效位数之间的关系:

其中tj,rms为ADC通道时钟间的均方根抖动,fs为时间交织ADC的采样频率,N为ADC有效位数.本设计应用于6-bit 600-MS/s12通道时间交织ADC,为保证至少6比特的有效位数,根据式(1)可得ADC所需时钟均方根抖动的上限为 tj,rms=8.29 ps.

图1 时间交织ADCFig.1 Time-interleaved ADC

2 系统结构

本文设计的基于延迟锁定环的时钟发生器整体结构如图2所示,系统主要包括压控延时链(Voltage-Controlled Delay Line,VCDL),PFD,CP,环路滤波器和倍频输出模块5个部分,其中前四个部分构成基本的DLL,环路的输入参考时钟与经过VCDL延时的时钟信号经过PFD比较后,两信号之间的相位误差转化为数字电压,经过电荷泵驱动后转换为模拟电流信号.这一电流信号在环路滤波器的电容上积累形成电压信号,而环路滤波器抑制了电流信号中的高频分量,仅把直流分量作为控制电压送到VCDL,调整VCDL的延时以减小VCDL输出信号与输入参考时钟之间的相位误差.环路锁定时,DLL部分产生一组12个与参考时钟频率相同,相位依次相差π/6的时钟信号φdll,φdll通过倍频输出模块后得到一组连续均匀相位的时钟φ1,φ2,…,φ12作为时间交织ADC的时钟控制信号,以及一个高频时钟φout用于测量抖动性能.

图2 基于延迟锁定环的时钟发生器结构框图Fig.2 Architecture of DLL-based clock generator

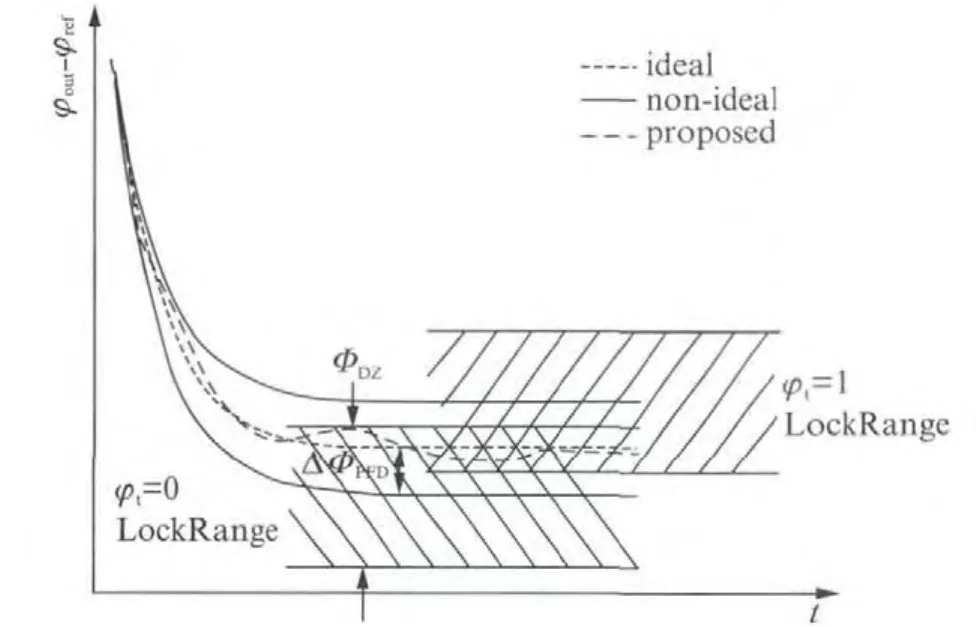

DLL系统中,输出信号是对输入参考时钟的延迟,因此输入参考时钟的每一个有效沿都会将相位误差清零,各模块产生的相位误差不会积累到下一个周期,具有较好的抖动性能,但DLL锁定时的静态相位误差会对输出产生一定影响.图3给出了非理想情况下,静态相位误差对DLL结构时钟发生器的影响:由于存在静态相位误差,反馈环路不得不将时钟沿推迟(或提前)一段时间以满足相位平衡条件.由于这种周期性的时钟沿推迟(或提前),DLL的输出波形就会产生周期性的异常宽度脉冲,输出相位也会出现周期性波动,有时还会导致输出时钟缺少或多出沿.

根据图3中的波形,可以估算基于DLL的时钟发生器中静态相位误差部分对输出时钟抖动的贡献:

图3 静态相位误差在DLL中的影响Fig.3 Static phase offset in DLL

其中M为时钟发生器提供的子时钟的数量,Δt为DLL结构中的静态相位误差.从式(2)可以看出,静态相位误差会给输出时钟带来直接影响,抑制静态相位误差能有效提高时钟发生器的抖动性能.本文中M=12,tj,rms,Δt=0.204Δt,静态相位误差对输出时钟抖动的影响系数为 0.204.

3 电路设计

3.1 电荷泵

为了减小静态相位误差,本设计使用了带误差放大器负反馈的低电流失配CP(图4).误差放大器的正负两端分别连在CP输出端和内部的A结点,当CP输出端电压Vout变化时,由于运放的钳位作用,A点的电压将会随输出端电压变动,使得VA=Vout,Idn=Ibias=IA和Iup=IA两组电流镜得以精确复制参考电流,避免了输出端电压变化导致的充放电电流失配问题.但引入负反馈放大器相当于在环路中增加了一个极点,需要考虑环路稳定性问题.为了保证环路的稳定性,在运放的输出端加入电容进行相位补偿,以免产生振荡.仿真结果表明,该结构的CP在输出电压0~0.9 V的范围内,充放电电流失配均小于2.5%.

3.2 鉴频鉴相器

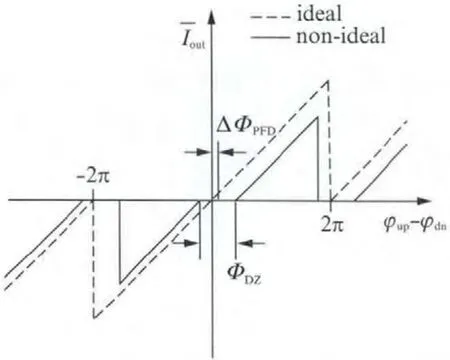

上文提到的静态相位误差主要来源于环路中的非理想PFD/CP结构,模拟CP充放电流失配和PFD的死区效应是电路中主要的非理想因素.PFD通常由D触发器构成,在触发器建立反馈通路时,PFD的两个输出同时有效,驱动后级的CP同时进行充电和放电,这会在VCDL的控制电压VVCDL上产生纹波,从而影响到VCDL的输出和最终的输出时钟.在输入相位误差很小的情况下,CP每个周期都会有一段时间同时进行充放电,VVCDL上产生周期性纹波,环路无法有效地控制输出相位,这就是PFD的死区效应.

图5给出了理想PFD/CP和非理想PFD/CP的相位-电流传递函数.理想情况下,PFD/CP结构传输曲线的斜率在-2π~2π区间内为常数,曲线关于原点中心对称.而在非理想PFD/CP的情况下,传输曲线在原点附近有一段宽度为ΦDZ,斜率为零的死区.在输出电流为零、系统稳定时,理想PFD的两个输入之间相位差为零,非理想PFD的两个输入之间相位差是一个常数ΔΦPFD,在时间域上对应Δt(如图3所示).

图4 低电流失配电荷泵Fig.4 Charge pump with minimum current mismatch

图5 PFD/CP的相位-电流传递函数Fig.5 Characteristic of PFD/CP

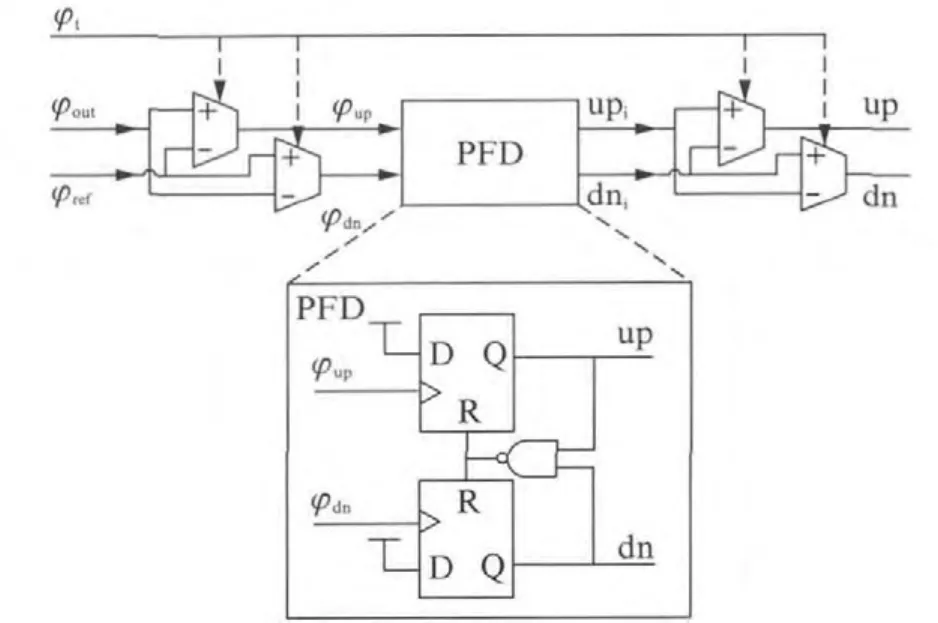

由于环路中存在非零静态相位误差,传统DLL的输出相位锁定在小幅超前(或滞后)于精确值的位置,输出时钟相位包含周期性纹波.为了减小上述非理想因素的影响,本文提出了一种切换型鉴频鉴相器(Transecting PFD,TPFD),在原有PFD的输入和输出通路上分别加入一对多路选择器,并引入一个定时切换时钟φt控制信号通路的选通(图6).

φt为高电平时,输入信号与输出信号顺序连接,图6中各信号间连接关系为φout-φup,φref-φdn,upiup,dni-dn.φt为低电平时,分别交换两个信号通路的连接,信号间连接关系为 φout- φdn,φref- φup,upidn,dni-up.通过每隔一段时间交换一次信号通路,在φt为高电平时TPFD的输入相位差ΔΦ=φout-φref,在φt为低电平时ΔΦ=φref-φout,因此环路在切换时钟φt电平不同的情况下有不同的可锁定范围,如图7所示.

图6 切换型鉴频鉴相器Fig.6 Circuit of transecting PFD

图7 环路使用不同PFD时的锁定过程Fig.7 Locking process of DLL with different PFDs

图7中的点线表示了理想PFD的情况下环路相位差的变化情况,如果切换时钟φt保持高电平或低电平不变,环路相位差变化情况如实线所示,阴影部分表示锁定范围,可以看出这种情况下锁定中心偏离理想位置较远,锁定范围较大.实际工作时,切换时钟φt定时交换PFD信号通路,因此锁定范围是两块阴影的交叠部分,锁定中心落在理想位置,锁定范围也很小.本设计中,PFD为上升沿有效,为了保证TPFD进行正确的相位比较,切换时钟φt的升降沿应当避开参考时钟的有效沿,与参考时钟的下降沿对齐.为了避免环路相位差锁定在两个锁定范围中的某一范围内,而不是二者的交叠部分,φt应当在保证相位比较结果正确的前提下尽可能地提高切换频率,因此切换时钟φt的频率取输入参考时钟频率的一半,信号通路以fref/2的频率进行切换.

使用TPFD的环路,其锁定范围为φt保持高电平或低电平两种情况下锁定范围的交集,可表示为:

由此可见,TPFD通过定时交换信号通路,将环路锁定范围从ΦDZ减小到ΦDZ-2ΔΦPFD,有效减少了PFD、CP模块带来的时钟抖动.

3.3 压控延时链

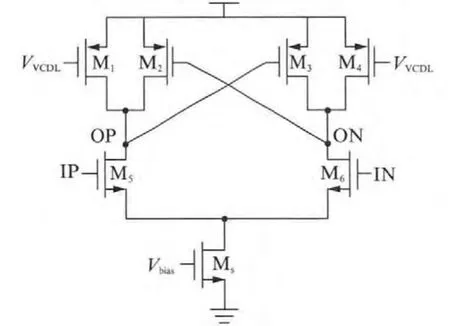

本设计中的VCDL采用了12级交叉耦合负载并联压控管的差分结构延时单元(图8).压控管M1、M4与负载管M2、M3并联,控制电压通过压控管栅极调整负载阻抗大小,改变VCDL的延时.由于交叉耦合的负载管带来的正反馈效应,延时单元有较好的信号再生性.在电源电压不变的情况下,使用交叉耦合负载的延时单元能获得较大的输出摆幅和更陡的信号边沿,这样的信号有助于减小输出时钟的抖动.另外,差分结构电路对共模噪声有良好的抑制作用,减小了电源和衬底耦合噪声对VCDL模块的影响.

3.4 倍频输出模块

对基于DLL的时钟发生器来说,延迟锁定环输出的信号与输入参考时钟频率相同,仅相位不同,因此产生高频信号时会用到额外的边沿组合电路(Edge Combiner,EC).常见的边沿组合电路有门电路型[6]和模拟电路型[7]两种,其中门电路型边沿组合电路功耗较低,但无法避免不同信号路径间的延时失配,在这一点上模拟电路型边沿组合电路可以做到较好的匹配.

图8 压控延时链中的延时单元Fig.8 Circuit of delay cell in VCDL

图9 边沿组合电路Fig.9 Circuit of edge combiner

图9给出了本设计中使用的边沿组合电路.延迟锁定环的输出φdll通过输出缓冲器后得到一系列时钟脉冲φ1,φ2,…,φ12,用于驱动边沿组合电路.电路工作时,同一时间有且仅有一个NMOS管导通,交叉耦合的负载管M13、M14根据输入管的导通情况,对输出节点进行充放电,由此得到一对经过倍频的差分信号φout和 φoutb.

4 版图设计和仿真结果

本论文采用65 nm CMOS工艺设计了一个基于DLL结构的时钟发生器,实现了12相位时钟输出,能为时间交织ADC提供所需的多相位时钟信号.为了测量多相时钟间的孔径抖动,将12个多相时钟合并为一个6倍频时钟输出进行测量.核心电路的版图面积为90μm×110μm(如图10),不同工艺角下在40~110 MHz的频率范围内可锁定,锁定时间小于1.2μs.图11给出了输入参考时钟50 MHz情况下的后仿结果,复位信号Vrst无效后1μs,环路滤波器的输出,即VCDL的控制电压VVCDL达到稳定,环路完成锁定.

图10 延迟锁定环版图Fig.10 Layout of DLL

图11 锁定过程中环路滤波器的输出电压Fig.11 Locking process of VCDL control voltage

图12给出了使用TPFD的DLL以及传统DLL的版图仿真结果比较.50 MHz输入下,使用TPFD的DLL 输出静态相位误差 Δt为 34.1 ps,峰峰值抖动 tj,pk-pk为 49 ps,均方根抖动 tj,rms为 8.1 ps 可满足模数转换器对时钟的要求.使用传统PFD的DLL输出静态相位误差为133 ps,峰峰值抖动为92 ps,均方根抖动为27.4 ps.从仿真结果来看,新结构的PFD使静态相位误差Δt减小了98.9 ps,峰峰值抖动减小了43 ps,均方根抖动tj,rms减小了19.3 ps,本文设计的DLL获得了较好的抖动性能.计算静态相位误差对均方根抖动的影响系数,Δtj,rms/Δt=0.195≈0.204,与理论值相符.为了比较不同工作频率的DLL静态相位误差性能,引入了归一化静态相位误差Δtnorm的概念:

图12 本设计和传统DLL的后仿结果比较Fig.12 Post-layout simulation of proposed DLL and traditional DLL

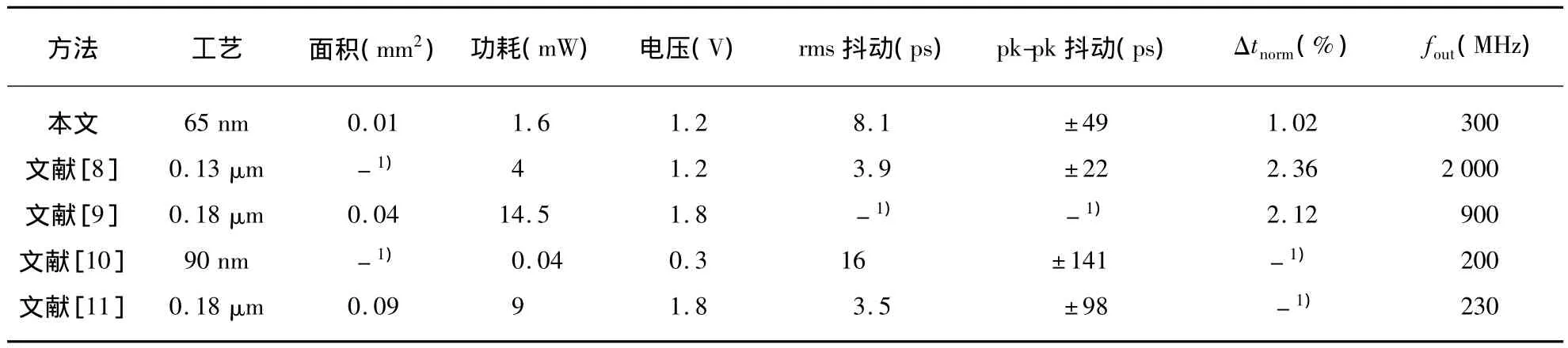

其中fout为DLL时钟发生器的输出频率.本设计中fout=300 MHz,Δtnorm=1.02%.表1比较了文献中的DLL与本设计的性能参数,本设计在面积、功耗、输出时钟抖动及静态相位误差几方面具有一定优势.

表1 本设计与参考文献中的DLL性能比较Tab.1 Comparison with state-of-the-art works

[1]Kurd N,Douglas J,Mosalikanti P,et al.Next generation Intel core micro-architecture(Nehalem)clocking[J].IEEE Journal of Solid-State Circuits,2009,44(4):1121-1129.

[2]Allen A,Desai J,Verdico F,et al.Dynamic frequency-switching clock system on a quad-core Itanium processor[C]∥IEEE International Solid-State Circuits Conference Digest of Technical Papers.San Francisco,CA,USA:IEEE Press,2009:62-63.

[3]Huh H,Koo Y,Lee K Y,et al.A CMOS dual-band fractional-N synthesizer with reference doubler and compensated charge pump[C]∥IEEE International Solid-State Circuits Conference Digest of Technical Papers.San Francisco,CA,USA:IEEE Press,2004:100-101.

[4]Maulik P C,Mercer D A.A DLL-based programmable clock multiplier in 0.18-μm CMOS with 70 dBc reference spur[J].IEEE Journal of Solid-State Circuits,2007,42(8):1642-1648.

[5]Parkey C R,Mikhael W B,Chester D B,et al.Modeling of jitter and its effects on time interleaved ADC conversion[C]∥IEEE AUTOTESTCON.Baltimore,MD:IEEE Press,2011:367-372.

[6]Kim JH,Kwak Y H,Kim M,et al.A 120-MHz 1.8-GHz CMOS DLL-based clock generator for dynamic frequency scaling[J].IEEE Journal of Solid-State Circuits,2006,41(9):2077-2082.

[7]Ok S,Chung K,Koo J,et al.An antiharmonic,programmable,DLL-based frequency multiplier for dynamic frequency scaling[J].IEEE Transactions on Very Large Scale Integration(VLSI)Systems,2010,18(7):1130-1134.

[8]Park JH,Jung D H,Ryu K,et al.ADDLL for clock-deskew buffer in high-performance SoCs[J].IEEE Transactions on Very Large Scale Integration(VLSI)Systems,2013,21(7):1368-1373.

[9]Kuo K C,Hsu Y H.A low power multi-band selector DLL with wide-locking range[C]∥IEEE International Conference on Integrated Circuit Design and Technology and Tutorial.Minatec Grenoble,France:IEEE Press,2008:25-28.

[10]Chang M H,Chuang L P,Chang I M,et al.A 300-mV 36μW multiphase dual digital clock output generator with self-calibration[C]∥IEEE International SOCConference.Newport Beach,CA,USA:IEEE Press,2008:97-100.

[11]Hsiao K J,Lee T C.The design and analysis of a fully integrated multiplying DLL with adaptive current tuning[J].IEEE Journal of Solid-State Circuits,2008,43(6):1427-1435.