针对植入式应用的8位100 kS/s的逐次逼近型模数转换器设计

闫 潇,王俊宇

(复旦大学专用集成电路与系统国家重点实验室,上海201203)

随着集成电路技术的发展,片上系统(System on Chip,SoC)因其在功耗、面积及成本上的优势逐渐替代了分离器件.在植入式医疗电子应用领域,为了实现无线可植入的应用需求,生物医疗电子系统应尽可能地降低能量消耗[1-2].作为生物医疗电子系统必不可少的模块,模数转换器(Analog-to-Digital Convertor,ADC)将反映人体生理特征的电化学模拟信号转化为数字信号,以便后续电路的处理.由于医疗电子领域的生物信号具有低频特性并且容易受到人体内外噪声的干扰,因此一个低功耗、中等精度和速度的逐次逼近型(Successive Approximation Register,SAR)模数转换器非常适合于医疗电子领域的应用[3].

本文针对植入式医疗电子的应用设计了一款低功耗8位逐次逼近型模数转换器(SAR ADC),并且进行了流片验证.为了降低功耗,SAR ADC采样开关采用无源的NMOS和PMOS对,子数模转换器由没有任何静态功耗的电容阵列构成,比较器采用了优化的动态比较器.为了减小动态比较器的失调电压,在保持比较器MOS管总尺寸不变的情况下,对动态比较器的各个MOS管的尺寸进行了优化.设计的SAR ADC在采样速率为100 kS/s时功耗为3.2μW.

1 SAR ADC设计

1.1 SAR ADC 架构

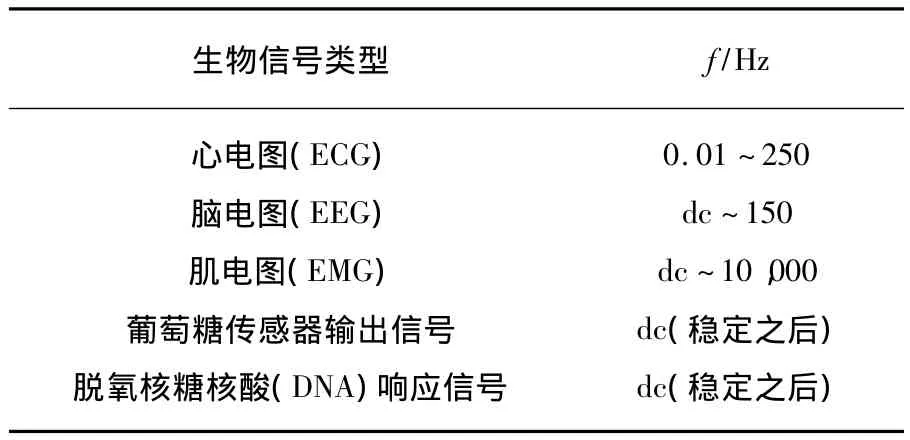

植入式医疗电子系统中的ADC一般不需要很高的采样率[4],例如心电图(ECG)、脑电图(EEG)、肌电图(EMG)、葡萄糖传感器输出信号、脱氧核糖核酸(DNA)响应信号等的频率一般都低于100 kHz(表1).此外,这些生物信号容易受到体内外各种噪声的干扰,8位分辨率的SAR ADC足以满足精度要求.因此,本论文的设计目标为低功耗中等精度的SAR ADC.采用差分结构的SAR ADC虽然能获得更高的精度但会有更多的功耗,因此所有子电路都采用了单端结构.SAR ADC结构如图1所示,包含采样保持电路、二进制权重的电容子数模转换器阵列(DAC)、动态比较器(Comparator)和逐次逼近逻辑控制器(SAR Logic Controller).

图1 SAR ADC电路结构Fig.1 Architecture of proposed SAR ADC

1.2 采样保持开关

本文设计的SAR ADC的采样保持开关分为两类(图1):开关S0,与电容阵列上极板及比较器输入端相连;开关S1~S9,与电容阵列下极板或者低阻源(输入信号源或者参考电压源)相连.SAR ADC中开关的沟道电荷注入效应和时钟馈通效应等非理想特性有可能会引起电路的非线性,从而使得SAR ADC精度下降.当比较器工作于比较周期时,开关S1~S9由于沟道电荷注入效应以及时钟馈通效应产生的非理想电荷会被参考电压源吸收,因而不会影响比较器的输出.所以开关S1~S9不需考虑其自身非理想效应的影响,只需采用NMOS和PMOS互补结构,以保证其导通电阻在0~Vdd(电源电压)范围内基本保持恒定即可.与S1~S9不同,在比较器的比较阶段,开关S0产生的非理想电荷会被电容阵列的上极板保持,使得电容阵列的输出值与采样信号的实际值产生一个偏差,从而影响比较器的输出,降低SAR ADC精度.为了减小沟道电荷注入效应以及时钟馈通的影响,在NMOS和PMOS互补开关(M1,M2)的基础上添加了两个额外的MOS管(M3,M4)(图2),其中M3与M4的尺寸分别为M1,M2的一半.后仿真结果表明,开关S0的有效位为10.1位,满足了SAR ADC的精度要求.

表1 人体生物信号及其频率Tab.1 Frequencies of biomedical signals in human body

图2 开关S0电路图Fig.2 Schematic of switch S0

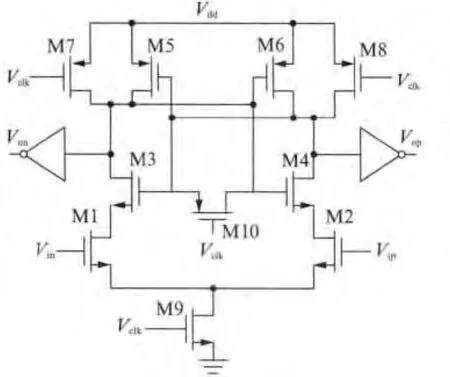

1.3 动态比较器

相比于静态比较器,动态比较器没有静态功耗,并且其动态电流只存在于比较周期的最初阶段,因而非常适用于低功耗的应用.本文设计了一个低功耗、低失调电压的动态比较器(图3).此动态比较器有两个工作周期:复位周期和比较周期.当Vclk为低电平时,比较器处于复位周期,此时输出端Von和Vop被复位到低电平;由于MOS管M9关断,整个比较器没有静态电流流过;MOS管M10用来消除前一个周期的迟滞效应.当Vclk为低电平时,比较器处于比较周期,此时M3~M6构成一个正反馈回路,该回路检测输入端Vin和Vip信号的电压差,并将此电压差进行放大和锁存,从而使得Von和Vop分别输出高电平或者低电平;当比较器输出稳定时,整个比较器模块不再消耗任何电流.

动态比较器面临的最大问题是具有较大的随机失调电压(包含静态失调电压和动态失调电压)[5].失调电压一般包含MOS管阈值电压(VT)的失调、MOS管尺寸(W/L)的失调以及工艺(Cox)的失调等.这些失调可以通过加大MOS管的尺寸来减小,但是大的尺寸意味着电路具有更大的寄生电容以及更多的功耗.本设计采取的策略是,分析动态比较器中各MOS管对失调电压的贡献大小,在保证总尺寸不变的情况下,对各MOS管的尺寸进行优化,以实现比较器在面积、功耗以及失调电压之间的折衷.各MOS管对失调电压的贡献用等效输入失调电压来分析.由公式(1)可见,输入MOS管对(M1和M2)对等效输入失调电压的贡献最大.

图3 动态比较器电路图Fig.3 Schematic of dynamic comparator

其中ΔVT为M1和M2的阈值电压失调,Vgs为M1和M2的栅极源极之间的电压差,ΔRL/RL和Δβ/β分别为比较器的负载失调和增益因子失调.由于比较器的等效输入失调电压随着过驱动电压(Vgs-VT)的改变而改变,故将M1和M2的尺寸设置为最大.对于M3~M6,它们对等效输入失调电压的贡献为自身的失调除以M1和M2的电压增益,因而M3~M6对等效输入失调电压的贡献相对较小,所以设计为中等尺寸.对于控制管M7~M10,它们对等效输入失调电压的贡献几乎可以忽略不计,因而采用最小的设计尺寸.此外,比较器的失调电压还取决于负载电容的失配.为解决此问题,两个反相器被嵌入到比较的输出结点以隔离负载电容不匹配对等效输入失调电压的影响,同时反相器还能对比较器的输出波形进行整形,增加比较器的驱动能力.

除失调电压外,还需考虑比较器的速率限制.对于8位100 kS/s的SAR ADC而言,其每一次转换需要10个时钟周期来完成,这意味着比较器的速率不能小于1 MHz.这里,考虑到比较器的输出精度在0.1%时,其建立时间必须为时间常数的7倍.综合上述因素,比较器的延时实际应小于100μs.

1.4 二进制电容子数模转换器

SAR ADC中子数模转换器可以由多种方式实现,比如电阻串、电流舵或者电容阵列.其中电容阵列子数模转换器不消耗静态功耗,因而非常适用于低功耗的实现.对于实际的工艺实现而言,电容的匹配性比电阻好,因而容易获得相对高的精度.二进制电容子数模转换器的电路实现如图1所示.二进制电容阵列由单位电容C0组合而成,C0电容值的选取需要在面积、功耗和失配之间进行折衷.

二进制电容子阵列虽然功耗低,但其微分非线性(DNL)和积分非线性(INL)往往较大[6].DNL最坏的情况出现在最高位和次高位的转换过程中,此时最高位2N—1个的电容关断/连接,低位的2N—1-1的独立电容连接/关断.假设单位电容C0的偏差符合高斯分布并用σ(C)表示,那么最高位和次高位的转换误差可以表示为:

σ(ΔC)可以表征电容失配对DNL的影响.显然,最高位σ(ΔC)的值大于其余低位的值.公式(3)中的σ(C)/C可以表示为:

其中W和L分别为单位电容C0的宽和长,S为面积.在0.13μm 1P8M工艺中,S的值为0.496μm2.在本文中,采用金属-绝缘层-金属(Metal-Insulator-Metal,MIM)实现的C0的值选定为40 fF,以实现功耗、面积和精度的折衷.后仿真结果表明,DNL标准偏差为0.2 LSB.

1.5 逐次逼近型逻辑控制器

SAR ADC产生各类控制信号用于控制采样保持开关,动态比较器以及子数模转换器.此8位SAR ADC每完成一次数据转换需要10个时钟周期:第一个周期为采样周期;第二个周期到第9个周期,SAR ADC依次产生D8~D1八位数字输出,并保存在寄存器中;最后一个周期,寄存器输出8位数字信号.SAR ADC由标准CMOS工艺实现,其功耗为[7]:

其中,fclk表示时钟频率,Ctot为电路的电容(包含电容阵列以及寄生电容),α(Vin)为与输入信号相关的开关频率因子.显然,随着Vdd(电源电压)的下降,逐次逼近逻辑控制器功耗下降.为降低功耗,SAR ADC的逻辑门采用了最小尺寸.

2 测试结果

芯片在0.13μm CMOS工艺下流片,SAR ADC为整个植入式葡萄糖传感器接口电路芯片的一部分,因而SAR ADC芯片的显微镜截图不含输出引脚.整个SAR ADC的面积为0.08 mm2(图4).

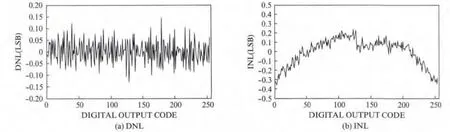

2.1 静态性能测试

图5给出了SAR ADC DNL和INL的测试结果.测试激励信号为峰值Vpp为1.2倍的满摆幅(1 V),频率为377 Hz的正弦信号,ADC采样频率为100 kHz.测试结果表明,DNL的值为 -0.15 LSB/+0.15 LSB,INL的值在-0.35 LSB 和 +0.23 LSB.

图4 SAR ADC芯片照片Fig.4 Photo of SAR ADC chip

图5 SAR ADC静态测试结果Fig.5 Measured DNL and INL of SAR ADC

2.2 动态性能测试

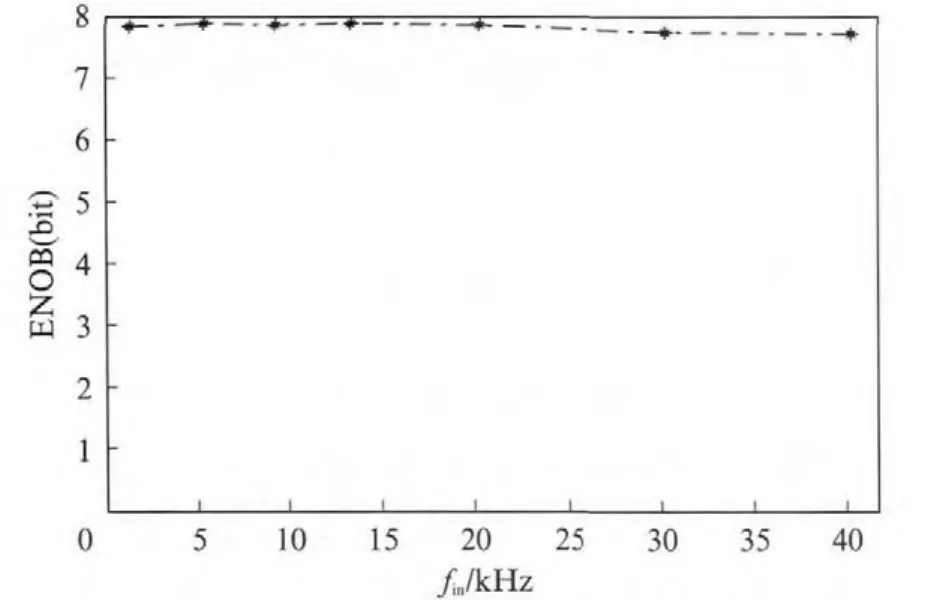

输入信号为接近满摆幅(1 V),频率为9.37 kHz的正弦信号输出频谱如图6所示.该SAR ADC的信号噪声失真比(SNDR)为49.2 dB,动态无杂散范围(SFDR)为63 dB,有效位(ENOB)为7.8位.

图7给出了有效位(ENOB)与输入频率之间的对应图.有效位(ENOB)即使在输入信号接近奈奎斯特频率时也没有明显的衰减,这意味着SAR ADC具有很大的有效位带宽(ERBW).

图6 SAR ADC输出频谱Fig.6 Measured output spectrum of SAR ADC

图7 ENOB随输入频率变化图Fig.7 Measured ENOB versus input frequencies

ADC的优值(Figure of Merit,FoM)衡量了模数转换器转换一步所消耗的能量.FoM的定义式为:

该SAR ADC在电源电压为1.2 V且采样频率为100 kHz时,功耗为3.2μW.那么该SAR ADC的FoM为143 fJ/conversion-step.

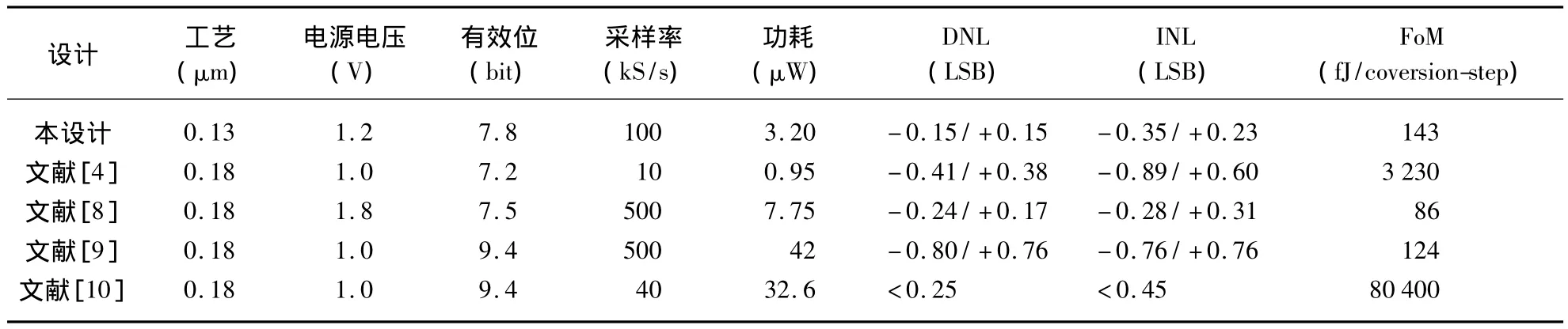

表2给出了该SAR ADC与其他医疗电子应用的SAR ADC的性能比较.该SAR ADC获得的有效位数较高,同时DNL和INL的测试结果都比较小.但是功耗和FoM介于所比较的SAR ADC[4,8-10]之间.

表2 与其他植入式医疗电子的SAR ADC的性能比较Tab.2 Comparison of SAR ADCs in biomedical applications

3 总结

本文针对植入式医疗电子应用设计了一款低功耗的8位100 kS/s SAR ADC,并且进行了流片验证.SAR ADC采样开关采用无源的NMOS和PMOS对,子数模转器为二进制电容阵列,比较器采用了优化的动态比较器.测试结果表明,当输入测试信号为9.37 kHz时,该SAR ADC的信号噪声失真比(SNDR)为49.2 dB,动态无杂散范围(SFDR)为63 dB,有效位(ENOB)为7.8位.其微分非线性(DNL)和积分非线性(INL)分别为 -0.15/+0.15 LSB 和 -0.35/+0.23 LSB,优值(FoM)为143 fJ/conversion-step,在电源电压为1.2 V 时,SAR ADC 功耗为3.2μW.

[1]Lee K H,Kung S Y,Verma N Verma,N.Improving kernel-energy trade-offs for machine learning in implantable and wearable biomedical applications[C]∥ Acoustics,Speech and Signal Processing,IEEE International Conference on(ICASSP).Prague,Czech Republic:IEEE Press,2011:1597-1600.

[2]Kim H,Yazicioglu R F,Kim S,et al.A configurable and low-power mixed signal SoC for portable ECG monitoring applications[C]∥Symposiumon VLSI Circuits.Honolulu,HI,USA:VLSI,2013:1-11.

[3]Scott M D,Boser B E,Pister K SJ.An ultralow-energy ADCfor smart dust[J].IEEE Journal of Solid-State Circuits,2003,38(7):1123-1129.

[4]Lee SY,Cheng C J,Wang C P,et al.A 1-V 8-bit 0.95mW successive approximation ADC for biosignal acquisition systems[C]∥IEEE International Symposium on Circuits and Systems(ISCAS).Taipei,China:IEEE Press,2009:649-652.

[5]He J,Zhan S,Chen D,et al.Analyses of Static and Dynamic Random Offset Voltages in Dynamic Comparators[J].IEEE Transactions on Biomedical Circuits and Systems,2009,56(5):911-918.

[6]Van den Bosch A,Borremans M A F,Steyaert M S J,et al.A 10-bit 1-GSample/s Nyquist current-steering CMOSD/A converter[J].IEEE Journal of Solid-State Circuits,2009,36(3):315-324.

[7]Hong H C,Lee G M.A 65-fJ/conversion-step 0.9-V 200-kS/s rail-to-rail 8-bit successive approximation ADC[J].IEEE Journal of Solid-State Circuits,2009,42(10):2161-2168.

[8]Chang Y K,Wang CS,Wang CK.A 8-bit 500-KS/s low power SAR ADCfor bio-medical applications[C]∥Solid-State Circuits Conference of Asia(ASSCC).Jeju,Korea:IEEE Press,2007:228-231.

[9]Pang W Y,Wang CS,Chang Y K,et al.A 10-bit 500-KS/s low power SAR ADCwith splitting comparator for bio-medical applications[C]∥Solid-State Circuits Conference of Asia(ASSCC).Taipei,China:IEEE Press,2009:149-152.

[10]Chow H C,Chen Y H.1V 10-bit successive approximation ADC for low power biomedical applications[C]∥18th European Conference on Circuit Theory and Design(ECCTD).Seville,Spain:IEEE Press,2007:196-199.