无线衰落信道下基带系统性能评估实验平台

朱秋明,陈小敏,戴秀超,黎 宁,虞湘宾

(南京航空航天大学电子信息工程学院,江苏南京 210016)

“通信原理”是信息工程专业的重要基础课程[1,2]。数字基带系统是该课程研究的重要内容,理论性比较强。近年来,基于Matlab、SystemVIEW和LabVIEW等仿真软件可视化辅助教学得到广泛应用,取得了较好的课堂教学效果[3,4]。

本文结合我校信息工程专业落实教育部提出的“卓越工程师教育培养计划”,开发了一套用于辅助“通信原理”实践教学的基带系统性能评估硬件实验系统[5]。学生在该实验系统中,通过动手操作演示、硬件电路修改和创新、嵌入式软件部分功能完善以及结合自己的兴趣开发新功能等,使他们对数字通信系统有实际的感受和直接的经验。

1 系统模型

考虑到数字基带系统的误码率分析是“通信原理”课程的难点之一,本文设计了一个如图1所示的基带系统性能评估综合实验系统。

为便于在实验系统的接收端进行误码率及误帧率性能测试,发射端对数据源进行组帧后才进行基带调制发送。为模拟实际无线信号传播过程中受到信道衰落和噪声的失真影响,该系统采用等效复基带信道进行建模:

其中,(t)和(t)分别为发送和接收的复基带信号(t)表示信道时变复衰落,它包含了路径损耗、阴影衰落和多径衰落等多种因素。通常可采用瑞利或Nakagami衰落分布建模;(t)表示等效的信道噪声,通常设为复高斯噪声。

2 基于FPGA的综合实验系统

2.1 硬件平台

数字基带实验系统的硬件平台包括基带处理模块、显示模块、A/D/D/A模块和外围接口模块等。由于本校通信专业学生已学习过FPGA相关课程,基带处理模块的主处理器选择采用了美国Xilinx公司的FPGA器件Virtex4-SX25,该芯片集成了4个DCM模块、128个 Xtreme DSP,128个 18kB的BLOCK RAM,最大的BLOCK RAM容量为2304kB。外围电路包括SRAM和FLASH等存储器件、拨码开关、LED以及数码管等。

2.2 基于FPGA的基带系统

为了正确识别每一帧的开始位置和结束位置,我们在发送端每一帧信息序列之前加入同步序列。常用的同步序列包括全0码、全1码、1和0交替码和巴克码,其中巴克码具有尖锐的自相关函数,很容易与随机序列区分开来,所以本系统采用13位巴克码序列1111100110101作为帧头。另外,发送信息序列采用1024位的m随机序列,FPGA实现时可采用10级线性反馈移存器产生。

综合实验系统的采样率设为10MHz,码元速率1.25MBaud。基带成型可有效减小信道带宽受限导致的码间干扰,脉冲成型滤波器采用32阶根升余弦波形,滤波器长度为4个符号周期(32个采样点)。接收端匹配滤波器与成型滤波器成复共轭关系,两者级联后满足升余弦特性,可以消除码间串扰。

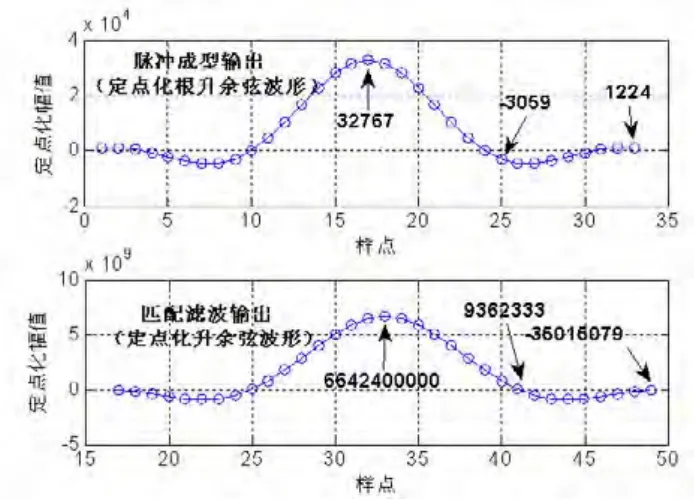

定点化后的根升余弦滤波器单位冲激响应以及匹配滤波后的输出波形如图2所示。由图可见,发射端脉冲成型后,前后两个码元对当前码元存在码间串扰,串扰值为最大样值的9.34%和3.74%。当接收端匹配滤波后,前后两个码元串扰影响分别降为0.14%和0.53%,可认为基本没有码间干扰了。

图2 根升余弦滤波器和匹配滤波输出波形

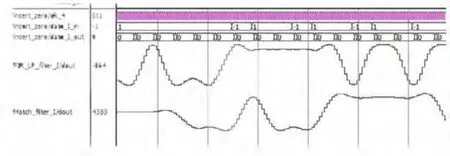

图3给出了上述实验参数下BPSK调制后基带系统ModelSim时序仿真图。

图3 基于ModelSim的仿真图形

图中data_I_in表示星座映射后的符号;data_I_out表示内插后的符号序列;两支路dout分别对应发射机脉冲成型和接收机匹配滤波后的输出波形,将该两路信号通过ISE(Integrated Software Environment)内嵌的逻辑分析仪ChipScope将数据导出,并利用Matlab工具获得眼图如图4所示。由图可见,发射端根升余弦脉冲滤波后输出波形存在码间串扰,但经过匹配滤波后的基本没有码间串扰,这与“通信原理”课程中非常重要的无码间串扰理论—奈奎斯特准则吻合。

图4 基于FPGA的基带系统输出眼图

2.3 基于FPGA的无线信道模拟

(1)SoS定点模型

谐波叠加方法SoS(Sum of Sinusoids)是指通过有限个具有特定幅度、频率和初始相位的正弦波叠加产生高斯随机过程,该方法具有明确的物理含义且易于FPGA硬件实现[6]。

谐波叠加方法的定点实现模型可表示为

其中,N为谐波数量;W表示每路余弦信号输出位数;θn表示初始相位且满足[0.2π]内均匀分布;fd表示最大多普勒频移,αn为各支路入射角,可采用如下取值方法

式中,θk为一微小的偏移量。

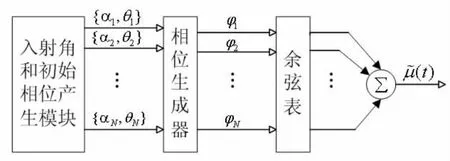

SoS模型的硬件实现框图如图5所示,各支路余弦信号采用查表法产生,余弦表深度和宽度位数分别为D=12和W=16。若直接存储,消耗的硬件资源较大,考虑到余弦波与其四分之一周期波形之间的相位转换关系,将查找表缩至只存储四分之一的波形大小,并且所有支路共享同一个表,通过时分方式进行访问,可大大节省FPGA存储资源。

图5 SoS模型硬件实现原理图

(2)瑞利衰落模块

瑞利衰落随机过程可由复高斯随机过程产生

式中,u1(t)和u2(t)表示相互独立的高斯随机过程。由于SoS模型输出位宽与散射支路数目及数据宽度有关,实验中采用16条散射支路即N=16,且每条支路输出位数W=16,对应SoS模型输出高斯随机变量的位宽为

对应瑞利衰落的平均功率则为2PGauss。

3)高斯噪声模块

为了模拟和验证不同信噪比情况下的数字基带系统误码率情况,需要根据瑞利衰落后信号的功率实时产生信道噪声。实验中的高斯噪声也由SoS模型产生,通过乘以特定的系数k,得到满足用户指定信噪比的高斯噪声。假设无信道衰落情况下,接收端匹配滤波后采样输出的信号电平为A。瑞利信道衰落功率为2PGauss,高斯噪声功率为PGauss,则输出信噪比可表示为

利用上式可获得不同信噪比情况下的系数k值。为简化FPGA实现噪声功率的调整,可灵活设置信噪比,使得k尽量满足2的整数次幂关系,从而通过对SoS高斯噪声模块输出序列的移位实现。

3 实验结果与讨论

基于上述系统模型和关键模块的定点算法,我们在以FPGA为核心的硬件平台上实现了数字基带系统演示及性能评估综合实验系统。学生可以通过Xilinx公司的集成软件环境ISE开发平台内嵌的逻辑分析仪ChipScope实时观测衰落信道前后的信号波形及星座图,从而加深对衰落信道及其对通信系统影响等理论知识的理解。

图6给出了四种不同信道情况下输出QPSK基带信号的星座映射图。由图可见:①对于无衰落无噪声信道,输出信号应为理想的四个点;②当信道仅存在衰落时,星座图变成了四条线,即幅值发生变化但相位不变;③当信道存在加性噪声时,相位也发生随机变化,星座图变成了四簇,且当噪声越大映射点分布越散乱,接收端误判的可能性也增加。

图6 不同信道条件下接收信号星座图

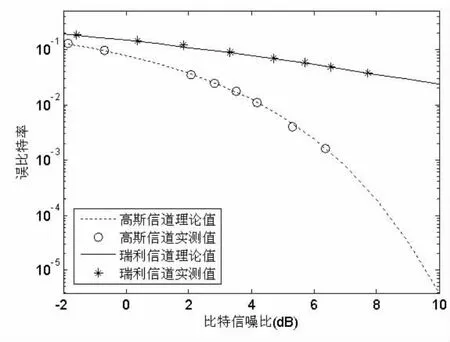

图7则给出了BPSK调制不同信噪比下接收端误比特统计结果,为便于比较图中还给出了无衰落情况下的性能曲线,此时学生可定量的理解信道衰落对基带通信系统性能的影响。

图7 BPSK实测误比特率性能曲线

4 结语

我们基于FPGA硬件平台开发了一个数字基带系统演示教学及性能评估综合实验平台,它以直观图形和数据方式展示硬件系统中基带通信各点波形的实时变化,使学生能从硬件角度去深入理解调制/解调、脉冲成型/匹配滤波以及无线信道衰落等特点,有效地提高了学生动手能力,从而提高了教学质量和效果。

[1]宋铁成.“通信原理”课程的系统级实验建设[J],南京:电气电子教学学报,2004,26(4):66-68

[2]樊昌信,曹丽娜.通信原理(第6版)[M],北京:国防工业出版社,2008.

[3]陈丽娜,基于SystemView的通信原理系统软件实验设计[J],上海:实验室研究与探索,2009,28(9):62-64.

[4]黄葆华,臧国珍,袁志刚,带限最佳数字基带系统误码性能分析[J],南京:电气电子教学学报,2012,34(3):16-18

[6]刘云等.基于蓝牙系统的基带处理仿真教学实验的设计与实现[J],南京:电气电子教学学报,2003,25(4):35-40

[7]朱秋明.非均匀散射空时频相关MIMO信道建模与仿真研究[D],南京航空航天大学,2011.