基于LVDS技术的雷达视频信号传输系统设计

朱 平,董荣果,黄光华

(1.船舶重工集团公司723所,扬州 225001;2.解放军91181部队,青岛 266405)

0 引 言

在目前舰载雷达系统中,由信号处理分机形成的多路数字视频信号通过数字/模拟(D/A)转换后形成模拟信号,再通过低损耗电缆传输至本雷达显控分机,由显控分机进行数字A/D采样处理。而随着传输距离及视频信号通道数的增加,会导致模拟视频信号衰减、相互间干扰等问题。针对此问题,本设计引入低电压差分信号传输技术即低压差分信号(LVDS)技术,构建信号传输系统。

LVDS技术使用非常低的幅度信号(100~450mV)通过1对平行的印制板走线或平衡电缆传输数据[1]。在2条平行的差分信号线上流经的电流及电压振幅相反,噪声信号同时耦合到2条线上,而接收端只关心2个信号的差值,于是噪声被抵消。由于LVDS信号本身只能在短距离情况下实现高速传输,因此本设计中通过在发送端增加信号驱动、接收端自适应均衡提供信号补偿来实现信号的长距离、高速率传输[2]。

1 传输系统总体设计

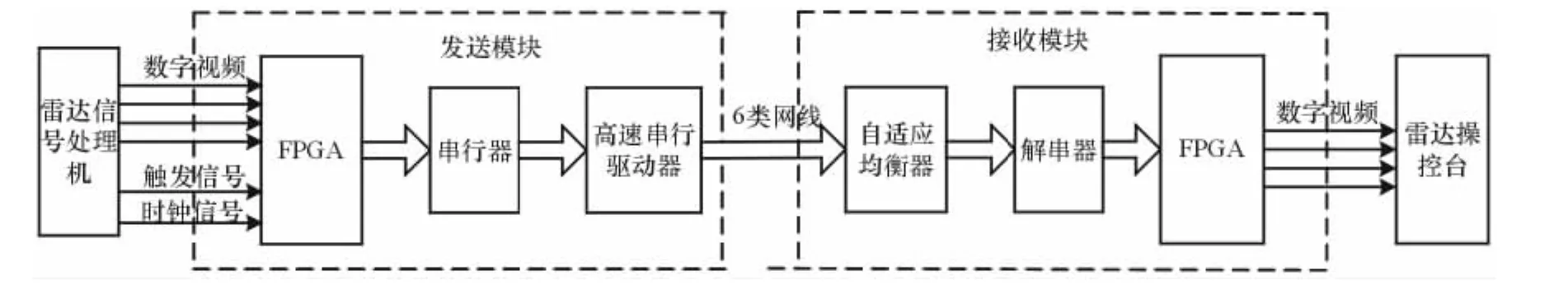

本文根据项目总体设计要求,需将4路视频信号编码后通过串行LVDS接口传送到雷达操控台,编码后传输速率达到400Mb/s,传输距离40m以上。据此,设计了本系统的总体框图,其由发送模块、接收模块及传输介质组成,如图1所示。

如图1所示,在发送模块中,将多路雷达视频信号通过并行总线传送到现场可编程门阵列(FP-GA),经过同步编码、8B/10B编码后,输入到串行器完成并行数据到串行数据的转化,形成高速数字串行流,再经过高速驱动器对信号驱动,以实现长距离传输;在接收端,首先通过自适应均衡器对信号强度进行恢复处理,再使用解串器恢复为并行信号,输入到FPGA中进行解码处理,将恢复后的数字视频信号输入到雷达操控台。

图1 雷达视频信号传输系统总体框图

2 传输系统硬件设计

本系统的硬件包括发送端和接收端2个部分,各自包括FPGA处理器、LVDS接口电路以及相应的外围电路等。其中FPGA处理器选择ALTERA公司Cyclone II系列的EP2C35;LVDS接口电路包括串行器/解串器、高速驱动器、自适应均衡器等,主要实现LVDS信号的转换和传输,是本系统设计的关键部分。

2.1 发送单元LVDS接口电路设计

本系统发送单元主要由串行芯片DS92LV1021和驱动芯片CLC006组成。DS92LV1021是美国国家半导体公司推出的一款10位并/串转换芯片,将10位并行TTL/CMOS信号转换为内嵌时钟的高速串行LVDS数字流。其主要特性为:时钟频率16~40MHz,内嵌数字锁相环,提供同步检测功能,低功耗等。由于串行器输出的LVDS信号差分压差约为100mV,一般情况下仅能传输几米,所以需要通过芯片CLC006对信号驱动,其输出压差可从0.7Vp-p调整到2Vp-p,以使信号传输更远的距离。其主要特性为:能在最高400Mbps的速率下驱动50Ω传输线,具有可控的输出信号上升沿和下降沿时间,能使传输引入的抖动最小[3]。发送单元接口原理图如图2所示。

图2 发送单元LVDS接口原理框图

2.2 接收单元LVDS接口电路设计

本系统接收单元主要由解串芯片DS92LV1212和自适应均衡芯片CLC014组成。解串芯片DS92LV1212与DS92LV1021为一组芯片,其接收高速差分数据流并将它们转换为并行数据,同时重建并行时钟。这组器件在进行数据串/并转换时采用的是内嵌时钟,这样可有效地解决由于时钟与数据的不严格同步而制约高速传输的瓶颈问题。自适应均衡芯片CLC014用于对远程传输后的接收数据进行均衡,它能自适应地对不同长度的双绞线进行均衡,适用的速率范围为50~650Mbps,且具有极低的抖动性能,为数字数据链路提供了很宽的噪声容限。接收单元接口电路原理框图如图5所示。

图3 接收单元LVDS接口原理框图

3 传输系统软件设计

在本系统中,软件部分主要指在FPGA芯片中的程序设计,包括对4路雷达视频信号的编码、解码时序设计,8B/10B编解码算法设计,并串/串并转换芯片的驱动以及相关传输协议的设计等。本文重点介绍8B/10B编解码的设计以及传输协议的制定,这是本系统能否正常工作的关键。

3.1 8B/10B编解码设计

在本系统中,由于所选择的串行/解串芯片DS92LV1021、DS92LV1212不具备直流平衡功能,因此在应用中要运用软件进行编解码,以保证数据传输的稳定性。本设计采用8B/10B编码方式,可使得发送的“0”、“1”数量保持基本一致,连续的“1”和“0”不超过5位,从而保持信号直流平衡。在发送端将8bit数据信号经过编码后形成保证直流平衡的10bit信号进行传输,在接收端,再按照编码规则进行解码以恢复出原信号[4]。

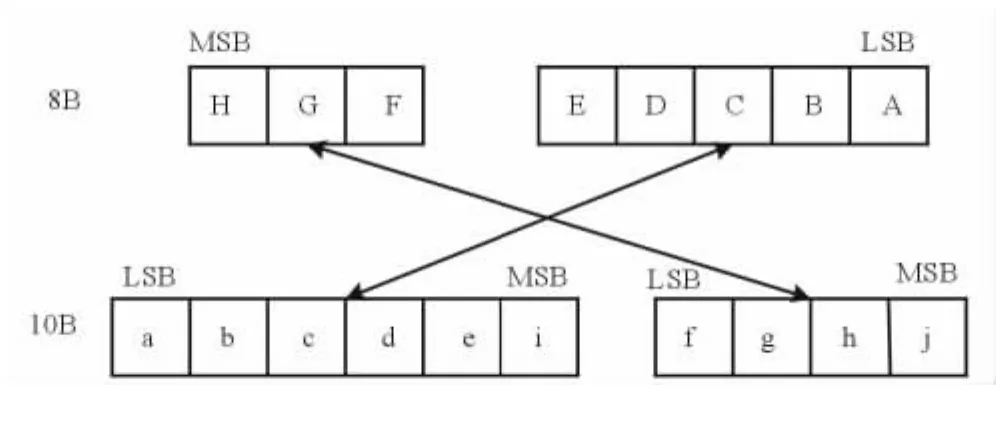

8B/10B编码时将拟发送的8bit字节ABCDEFGH分割成EDCBA和HGF两部分,其中E和H为这两部分的最高位,而编码后生成对应的jedcba和ihgf两部分字符,其中i和j为这两部分的最高位。即将8B/10B编码分为5B/6B编码和3B/4B编码两部分,编码的映射规则如图4所示。

图4 编码映射规则

在8B/10B编码中,通过设计游程值RD来保持编码的直流平衡。将10位编码输出分为正游程值RD+和负游程值RD-,其中RD+表示编码输出中1的个数大于0的个数,RD-表示编码输出中1的个数小于等于0的个数。0、1个数相等的编码输出称为完美平衡码。编码器通过游程值控制位选择当前的编码输出,游程值控制位受前一周期的输出码及前一周期游程值控制位的影响。

如图5所示,编码器复位后,游程值初始化为RD-,编码器编码时选择负的编码输出结果,同时判断是否为完美平衡码,若是则游程值控制位保持不变,输出到下一字节的编码中,否则游程值控制位取反。同理,当游程值控制位为RD+时,选择正的编码输出,再根据输出是否为完美平衡码决定下字节游程控制码的取值。这样通过交替使用RD+和RD-的编码输出来保持输出的直流平衡。

图5 RD有限状态图

3.2 传输协议制定

根据信号传输内容及8B/10B编码协议,制定本系统信号传输协议,传输内容主要包括4路数字视频以及雷达信号处理机与显控台之间的部分控制信号等,协议具备一定的可扩展性。

根据信号编码原理,以8B/10B编码表的控制字符作为监督码元,由于监督码元具有唯一性,可以作为传输数据的帧头和帧尾,以此来判断接收到的数据,制定的传输协议如图6所示。

图6 数据传输结构

如图6所示,将4路视频信号以及控制信号分成不同字段,每个字段包括帧头、传输数据、帧尾,帧头、帧尾均采用8B/10B编码表的控制字符,控制字符具有唯一性。以4路视频传输为例,可选择帧头、帧尾如下:第1路视频信号帧头选择控制字符为K28.0(0010111100)、帧尾为 K28.1(1001111100);第2路视频信号帧头选择控制字符为K28.2(1010111100)、帧尾为 K28.3(1100111100);第3路视频信号帧头选择控制字符为K28.4(0100111100)、帧尾为 K28.5(0101111100);第4路视频信号帧头选择控制字符为K28.6(0110111100)、帧尾为 K28.7(0001111100)。

4 系统测试

本文对传输系统进行了测试,在软件中编写发送数据序列,利用嵌入式逻辑分析仪SignalTapII来观察接收端是否接收到数据,且是否正确。在FPGA中通过编写计数器产生发送序列,作为发送数据源,编码、驱动后通过100m6类网线发送;接收后,经过自适应均衡器,解码后输入到FPGA中,同时在FPGA中产生同样结构的数据序列作为比较信号,通过判断后实现数据同步并开始比较,如有不同则使误码计数器加1[5]。其信号传输测试框图如图7所示。

在并行速率40MHz(即串行速率400MHz)时,利用嵌入式逻辑分析仪SignalTapII观察发送端和接收端的数据,可见发送数据经过一定延时后都能正确接收,验证了该方案设计的可行性。 其数据发送、接收时序图如图8所示。

图7 信号传输测试框图

图8 数据发送、接收波形图

经过连续1h的测试,没有误码出现,表明该系统工作正常。同时,利用软件对延时时间进行了测试,测试结果如图9所示。

图9 软件延时图

如图9所示,当采用100m电缆传输时,通过内嵌逻辑分析仪对传输数据进行抓取,可测得延时时间为800ns左右。经理论计算,传输电缆的延迟时间、芯片的转换时间、编解码时间之和在800ns左右,所以验证了本传输系统的正确性。

5 结束语

本文介绍了LVDS技术在雷达视频信号传输中的应用,通过软硬件设计、数据传输测试等验证了高速LVDS信号长距离传输在雷达设备中应用的可行性。该系统具有走线简单、抗干扰能力强等特点,通过数字信号传输解决了模拟信号长距离传输的信号衰减等问题,具有很好的应用价值。

[1] 王晓君,宇文英,罗跃东.基于FPGA的CPCI和LVDS接口技 术 及 应 用 [J].半 导 体 技 术,2007,32(3):248-251.

[2] 宋燕星,袁峰,丁振良.LVDS技术在高速多信道数据传输中的应用[J].电子技术应用,2006(10):75-76.

[3] 布明恩,杨文荣,张启平.8位LVDS串行器的设计应用[J].微计算机信息,2005,21(1):103-104.

[4] 毛继志,李建周,许家栋.基于FPGA的高速数传系统研究[J].微计算机信息,2005,22(1):104-107.

[5] 吴迪.应用LVDS技术解决多信道高速数据传输问题[J].计算机与信息技术,2007(17):568.