11位数控延迟线组件的设计

程翔

(海军驻南京924厂军事代表室,江苏 南京211100)

数控微波延时组件在信号处理系统、雷达系统和相控阵系统等许多领域中具有广泛的应用。为了提高雷达的测距精度,补偿不同工作频率引起的相位差,n位数控延时组件经常在现代宽带雷达系统中获得应用[1-2]。

传统的时间延迟线包括静磁波延迟线、声表面波延迟线和光纤延迟线。但较高的损耗和大的体积限制了这些传统延迟线的应用。

本项目采用微带集成电路形式,用PIN微波开关二极管作为控制元件,配合数控电路,实现对微波信号延迟时间的控制。与传统的静磁波延时线、声表面波延时线和光纤延时线相比,本设计具有损耗小、体积小和重量轻的优点。

1 设计要求与原理

1.1组件指标

综合设计要求,11位数控延迟线组件的设计指标为:

(1)输入信号频率范围:0.6 GHz~3.0 GHz;

(2)延迟范围:0 ns~10 ns;

(3)延迟步进:5 ps;

(4)增益:≥0 dB;

(5)输出幅度变化:≤±1 dB(最大延时与最小延时状态比较);

(6)输入/输出驻波:≤1.5;

(7)延时切换时间:≤80 ns。

1.2组件原理框图

数控延迟线的每一位由2个SPDT开关和延迟线构成,整个数控延迟线由11个代表不同延时的单元组成。原理框图如图1所示[3]。

2 组件设计

2.1 延迟线设计

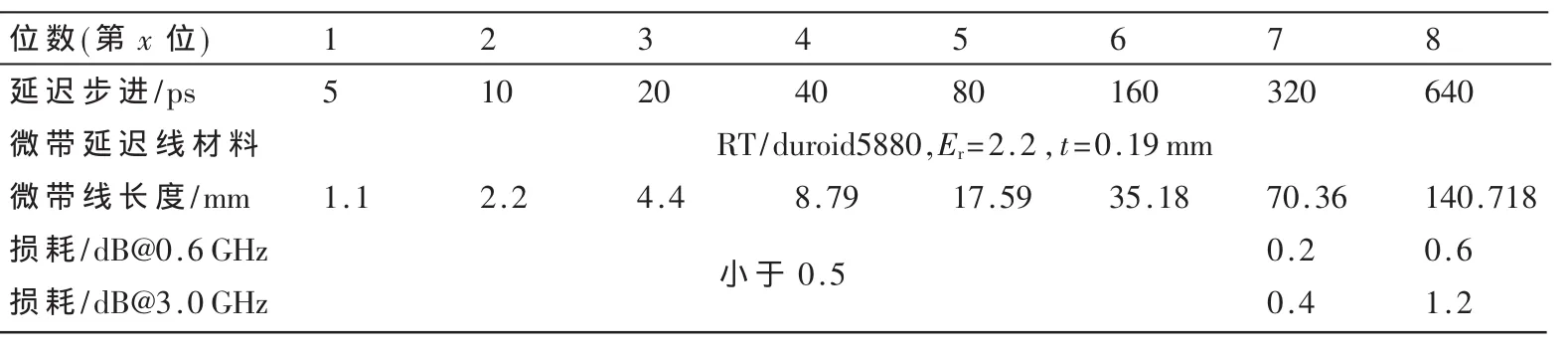

前8位延迟线因延时小、精度高、损耗小,拟采用微带线设计,其长度、损耗如表1所示。

图1 原理框图

表1 前8位延迟线设计表

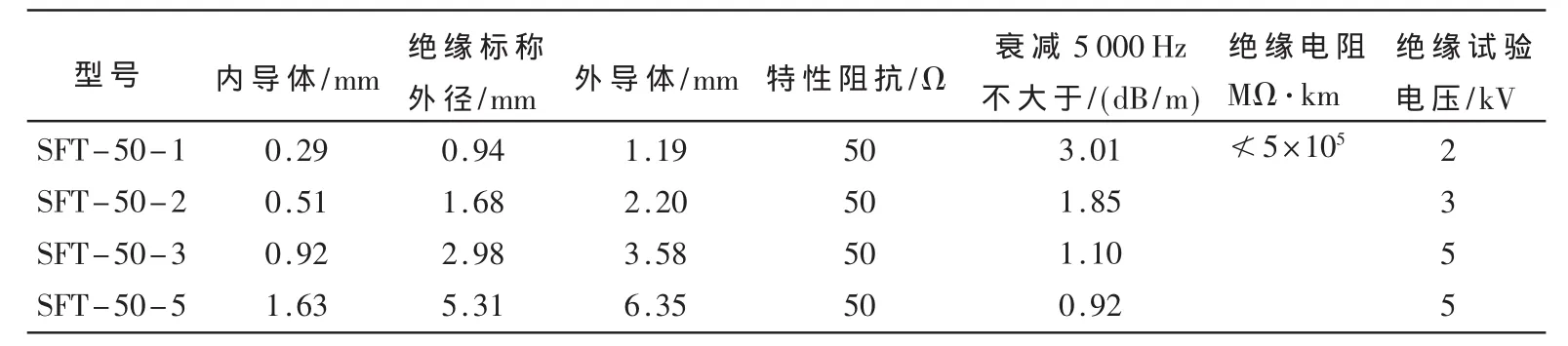

表2 SFT-50-2电缆性能表

其中微带线长度可由下式计算而得:

式中,L为长度,单位为m;t为延迟时间,单位为s;v为介质中传播相速,单位为m/s。

后3位延迟线的延迟时间较长,若再采用便于混合集成的微带线结构,则会导致体积增加,损耗相对于直通通道增大很多。设计时考虑常用的硬同轴电缆SFT-50-2作为延迟线,其特性如表2所示。

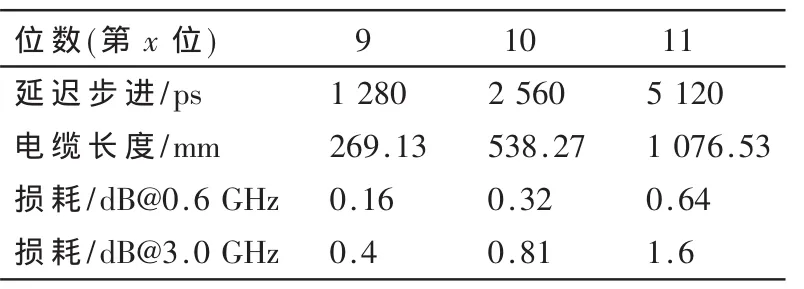

后3位共延时 8 960 ps,需要电缆长度为 8.960÷4.756≈1.883 9 m。每一位的计算情况如表3所示。其中常数4.756为每米延迟时间,单位为ns/m。

表3 后3位延迟线设计表

2.2 延迟线幅度调整设计

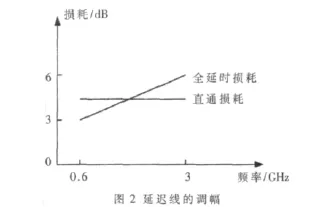

若采用以上设计方法,延迟线总的损耗约为:6 dB@3 GHz、3 dB@0.6 GHz,该值为全延时状态与直通状态之间的损耗差,此时差值较大,需改善延时的调幅性能。考虑在延迟损耗较大的每一位直通通路添加阻性衰减器,每一位添加的衰减量控制在它的3 GHz延迟损耗和0.6 GHz延迟损耗之间,那么整个数控延迟线的直通与全延时状态之间的损耗差将在2 dB以内,如图2所示。

通过添加损耗与延迟线损耗相似且对传输相位几乎没有影响的电路,可以达到比添加阻性衰减器更好的效果。仿真电路及结果如图3~图6所示。本文仅给出第7位的电路仿真图。

2.3 开关设计

开关设计需保证在不同延时状态之间进行切换时不出现谐振现象。由于有很多位开关串联,应综合考虑开关隔离度以及控制、线圈圈数等。本文选用串并联结合的开关形式。

2.4均衡器设计

由于频带较宽,覆盖范围为 0.6 GHz~3.0 GHz,因此在高低端的损耗存在差异,需要引入均衡器对幅度进行均衡,从而达到整个频带内的波动要求。本文选成熟的均衡模块,减少重复设计,缩短设计周期,提高设计效率。

2.5增益补偿

由于整个组件需要实现0 dB的增益要求,所以在组件内部还需添加放大器来补偿由延迟线带来的损耗。本文选用单片放大器SNA-386来实现该要求。

通过以上设计,本文较好地实现了11位数控延迟线组件的小型化设计。通过本文的研究,基本掌握该频段数控延迟线组件的设计方法和关键工艺技术突破,对以后其他频段数控延迟线的设计具有一定的指引作用。

[1]清华大学《微带电路》编写组.微带电路[M].北京:人民邮电出版社,1976.

[2]BAHI I,BHARTIA P.微波固态电路设计(第二版)[M].郑新,赵玉洁,刘永宁,等译.北京:电子工业出版社,2006.

[3]汪霆雷,魏文博,刘其中,等.小型化5位数控延迟线的设计[J].西安电子科技大学学报,2008,35(2):258-261.