伪随机数发生器

孙福玉,曹万苍

(赤峰学院,内蒙古赤峰024000)

伪随机数发生器

孙福玉,曹万苍

(赤峰学院,内蒙古赤峰024000)

文章分析了555电路、74HC160计数器、CD4511译码器等器件的基本工作原理,用555电路产生高频脉冲信号,用74HC160计数,通过CD4511译码后送入数码管显示一个随机数.

随机数;伪随机数;发生器

1 引言

随机数在我们的生活中随处可见,例如掷一枚色子所得到的点数、任何一个班级的学生数、某一路段的车流量或者是迎面行驶而来的车辆的车牌号等等.伴随随机事件而产生的随机的数字称为随机数.因为随机数的不可预知性,单一或者小规模的试验是不能正确的估算出随机数的规律的,试验次数越多,则得到的结果越接近真正的答案.本文利用555电路产生脉冲信号,用74HC160计数,通过CD4511译码后送入数码管显示一个随机数.

2 基本器件介绍

2.1 CD4511的功能介绍

首先,我们介绍一下支持数字输出的7段译码器CD4511.图1为七段显示译码器的管脚图.

图1 七段显示译码器的管脚图

4管脚BI管脚为消隐输入控制端子,如果BI为0,不论其它管脚输入什么值,七段显示数码管处于熄灭状态,也称为消隐状态,七段显示数码不显示数字.如果BI为1,各笔段均正常显示.

3管脚LT管脚为测试输入端子,当BI为1,LT为0时,译码输出全为高电平,不论输入端子输入何值,七段显示译码器均工作,从而显示数字8.各笔段均被点亮,以检查显示是否有故障发生.

5管脚LE管脚为锁定控制端,CD4511中的译码器的锁存电路由传输门和反相器组成,传输门的导通或截止由控制端LE的电平状态.当LE=0时,允许译码输出.LE=1时译码器是锁定保持状态,译码器输出被保持在LE=0时的数值.

A1、A2、A3、A4为译码器输入端.a、b、c、d、e、f、g为译码输出端,用于驱动共阴极数码管工作,输出为高电平1时有效.

另外,译码器在显示数“6”时,a段消隐;显示数“9”时,d、段消隐,所以显示6、9这两个数时,字形不太美观.所谓共阴LED数码管是指7段LED的阴极是连在一起的,在应用中应接地.限流电阻要根据电源电压来选取,电源电压5V时可使用300欧姆的限流电阻.

由以上关于CD4511的介绍可知,它能够根据外部信号使LED点亮或者熄灭,从而达到译码输出的功能.

2.2 74HC160的功能介绍

74HC160是74系列的4位同步式十进制计数器,74HC160管脚图如图2所示.

图2 74HC160管脚图

74HC160的具体功能如下:

CLK:时钟脉冲输入端.引入外部时钟控制脉冲的输入端,无时钟脉冲输入时,无法使用计数功能.74HC160接入电路后与译码器等电路元件共用同一时钟脉冲.

CLR:复位端,低电平有效,当CLR=0时,输出端异步归零.

ENP:禁止计数端,低电平有效,当ENP=0时,计数器失去计数功能.

ENT:计数和RC禁止端,低电平有效,当ENT=0时,计数器失去计数和RC功能.同时,ENP失去作用.也就是说,当ENT为低电平时,无论ENP是高电平还是低电平,都无法实现计数功能.

LOAD:寄存/计数端,低电平寄存,高电平计数,即当LOAD=0时,计数器处于寄存状态,存储的是前一时钟周期的状态,当LOAD=1时,计数器处于计数状态.

由以上有关于74HC160功能的介绍,我们可以了解到:使用两个74HC160级联可以达到我们要求的37进制计数器,还要利用LOAD端的寄存/计数功能来设计数字显示的伪随机数发生器的复位功能.

2.3 555定时器的功能介绍

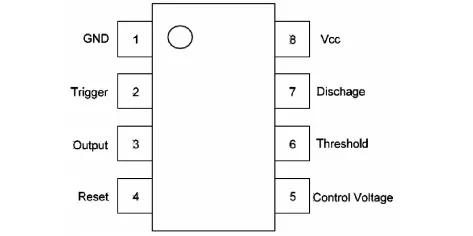

在通常的集成电路中,要使电路的各个元件良好地工作在同一状态下,必须对其时钟控制电路进行设计和改善.在本电路中,我们使用555定时器产生时钟脉冲.接下来,我们对NE555作一介绍.NE555管脚图如图3所示:

图3 NE555管脚图

555定时器的各个引脚功能如下:

管脚1为接地端.管脚8为外接电源VCC端子,一般用5V电源.管脚3为输出端子.管脚2为低触发端.管脚6为高触发端子.管脚4为直接清零端.当该端子接低电平0时,时基电路不工作,这时不论TH处于何电平,时基电路输出均为0,该端不用时应接高电平1.管脚5为控制电压端子.若此管脚外接电压,则可改变内部两个比较器的基准电压,当不用该管脚时,应将该管脚串入一只电容接地,以避免外部干扰.管脚7为放电端子.该管脚与放电三极管集电极相连,用做定时器时电容的放电.

555定时器在本电路设计中,应使4、8脚接VCC,1脚接地,5脚加电容接地以防外部干扰,7、8脚、6、7脚间加滑动变阻器以改变输出时钟脉冲的频率,以达到产生时钟脉冲的作用.时钟脉冲的频率如下式所示,通过调节R1,R2,C1可以得到不同频率的时钟.

3 用数字显示的伪随机数发生器电路的分析

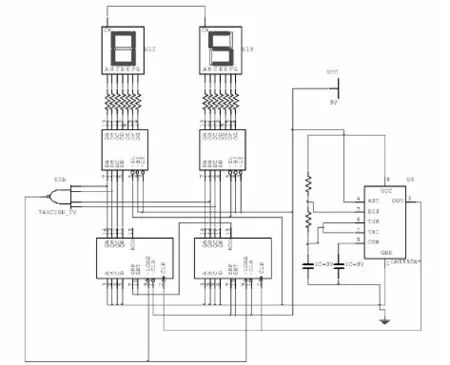

图4是伪随机数发生器的电路图.由于只是使用计数器,所以并不复杂.

在此电路的设计过程中,首先由555定时器产生控制74HC160计数的时钟脉冲.因此,在具体电路的制作与焊接过程中,可以在555定时器与计数器的连接线上加一开关.开关按下,则开始计数,开关松开,则停止计数并显示上一状态的数字.同时,可以通过调节其外接电容来控制其输出时钟脉冲的高低.在具体电路的制作过程中,作者使用的是0—10K的滑动变阻器,在安装焊接前,调节电阻到5K,可以正常显示数字.

然后,由两个74HC160构成该电路的计数器.注意,由于我们只要求计数到36,所以在设计时,由两个74HC160的LOAD端接出一个74HC30(八输入与非门)来进行置位,设计我们对计数的要求,我们可以把个位的DB、DC端,十位的DA、DB端接入74HC30的输入端,其余输入端口则全部接VCC,则可以达到异步置位的功能.

接下来,要将74HC160的输入端接入CD4511的输入端,把四位二进制数译码为供数字显示的7位数据.在数字显示器和CD4511间,要加入能使数字显示器正常发光的电阻,在具体电路的测试中可知,使用475欧姆的电阻可以使数字显示器正常发光.

这种设计方案所制作出的伪随机数发生器的使用方法很简单.按下接通电源的启动开关后,LED就显示各种数字.计数器的内容从0开始按序号变化,不是随机的.所以可以使用稍快的时钟脉冲.在按下停止开关后的一段时间内,计数器照样工作,然后停止在某一数字上.这个数字就是得中的数字.

图4 伪随机数发生器电路图

4 结束语

文章分析了555电路、74HC160计数器、CD4511译码器等器件的基本工作原理,用555电路产生高频脉冲信号,用74HC160计数,通过CD4511译码后送入数码管显示一个随机数.

〔1〕汤山俊夫.数字电路设计与制作[M].北京:科学出版社,2009.

〔2〕黄智伟.电子电路计算机仿真设计与分析[M].北京:电子工业出版社,2009.

〔3〕孙余凯.传感器应用电路300例[M].北京:电子工业出版社,2008.

〔4〕张庆双.LED应用电路精选[M].北京:机械工业出版社,2010.

TP212

A

1673-260X(2013)12-0030-02