500fps图像采集及实时显示关键技术研究*

侯宏录,高伟平

(西安工业大学 光电工程学院,陕西 西安 710021)

引 言

高帧频相机是研究物体的高速运动或瞬态流逝现象的有效工具,广泛应用于航空、航天以及武器系统等领域,研究高速运动物体的运动规律,在武器试验领域可对舰载、机载导弹发射姿态进行实时记录与跟踪,对其性能进行分析等,为武器系统试验验证提供决策依据。

长期以来,中国的高帧频相机主要依赖于进口,尽管进口相机的帧频达到了1 000fps,可分辨率很低,且使用条件仅限于民用,所采用的技术不对外公开,可借鉴的文献极少。国内目前研究高帧频相机的单位极少,长春光机所在2008 年研制的高帧频互补金属氧化物半导体(complementary metal oxide semiconductor,CMOS)实时图像采集系统能够满足高速图像数据的采集与处理,且画面清晰,但该系统采用Camera Link接口实现数据的传输,通过PCI图像采集卡将数据采集到计算机上进行处理及显示,系统体积较大,不符合机载相机体积小的要求[1]。

本文所研究的高帧频图像采集系统的分辨率为1 024×1 280,采集帧频为500fps,对实时图像采集和数据处理的要求很高。采用Cypress公司130万像数的LUPA1300-2型CMOS图像传感器捕获图像信息,以现场可编程门阵列(field-programmable gate array,FPGA)为核心处理单元来完成500fps的图像数据采集及实时显示,对图像数据的采集,色彩复原,先入先出队列(first in first out,FIFO)缓存,同步动态随机存储器(synchronous dynamic random access memory,SDRAM)存贮及VGA 显示进行的研究,可满足机载、舰载和车载环境下高机动性、小型一体化的需求。

1 图像采集系统的总体方案分析

由于要对高速运动物体的瞬态图像进行拍摄,如爆炸瞬间,导弹发射瞬间等,需要较高的分辨率及帧频,为满足需求,所研究的500fps图像采集与实时显示系统的主要技术参数有:

拍摄帧频:500fps;

采集像素数:1 024×1 280;

数据位宽:10bit。

由系统的主要技术参数可以计算出高帧频数字图像传感器的图像信息输出速度为781.25 MB/s,并且LUPA1300-2图像传感器输出格式为Bayer格式,需要转化为RGB格式,格式转化后在FPGA 内部的传输速度为2343.75 MB/s[2]。由此可见,系统的数据处理量很大,对FPGA、缓存器件的性能及数据处理算法的要求很高。由于帧频很高,不需要人眼实时观察全过程,仅观察变化规律即可,因此在实时显示环节,采用抽帧显示的方式,可以减小系统的数据处理负担,增加系统的稳定性。

本文选用Altera公司的Cyclone II系列EP2C35型号的FPGA 芯片作为核心处理单元,系统有低压差分信号(low-voltage differential signaling,LVDS)支持,接收端最高805 Mbit/s 数据速率,支持SDRAM、DDR2SDRAM 器件,使系统的硬件结构更为简单。系统的总体框图如图1所示。

图1 图像采集系统的总体框图Fig.1 The general block diagram of image acquisition system

系统工作时首先通过键盘启动数字图像传感器LUPA1300-2,FPGA 通过串行外设接口(serial peripheral interface,SPI)总线将默认参数传输到LUPA1300-2,如曝光时间、像素数、开窗区域等,并对整个系统进行初始化设置。系统启动完成后由LUPA1300-2捕获高速运动目标的瞬态图像信息,通过高速LVDS接口将Bayer格式的图像传输到图像采集模块,由色彩复原模块对完成图像色彩重建,转化为RGB格式图像。图像抽帧模块每20帧抽取一帧图像,且通过FIFO1缓存存储到SDRAM 中,由FIFO2读取SDRAM 中暂存的图像信息并传输到VGA 接口,最终在LCD 上实时显示[3]。

2 图像采集模块设计

图像采集模块对LVDS信号进行串行数据解析,得到同步信息码,还原出正常的图像同步信息。如行有效信号,场有效信号等,最终完成对图像信息的采集。

LUPA1300-2是Cypress公司推出的针对机器视觉和运动分析的高性能的CMOS图像传感器,它能够提供无失真图像并执行快速读出。LUPA1300-2在1 024×1 280分辨率下可实现500fps的图像采集,利用视窗或子采样读取模式可以达到更高的帧速率;采用12路10位ADC 的LVDS以DDR 方式输出,每通道像素率最大为630Mbit/s;采用管线化全局同步快门成像,可有效避免拍摄高速运动所产生的影像模糊和图像畸变;通过SPI接口对CMOS 传感器内部寄存器配置,控制传感器的工作状态,控制方式简单、灵活;输出图像格式为Bayer格式,要在传感器外部完成色彩重建[4]。

2.1 LUPA1300-2工作时序

LUPA1300-2 的工作流程分为如下几步:初始化复位、训练模式、配置片内寄存器、像素光积分、图像信号放大和量化输出。

LUPA1300-2在工作时首先通过RESET_N 对传感器的片载序列发生器、内部寄存器和时序电路进行复位;复位完成后启动训练模式,确保读出图像数据的正确性;然后通过SPI总线对片内寄存器进行配置,主要包括传感器的帧频、曝光时间、开窗、光积分模式等;寄存器配置完成后开始对图像进行捕获、图像信号放大、LVDS量化输出。

2.2 SPI总线时序驱动

FPGA 通过SPI总线对LUPA1300-2内部105个寄存器进行配置,以使传感器能够正常工作。SPI总线有CS、CLK、IN、OUT 四条信号线。CLK 提供接口同步时钟,最高速率为主时钟的三十分之一。每组数据有16位,第1位为读写控制命令位,第2~8位为内部寄存器的地址位,第9~16位为数据位,对应于传感器的寄存器配置参数。其中SPI读时序的仿真图如图2所示。

图2 SPI总线读时序仿真图Fig.2 The simulation of SPI bus read timing sequence

2.3 LVDS信号接收

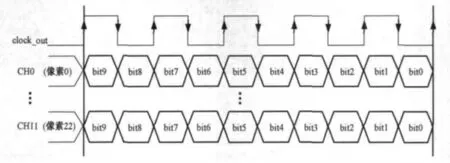

LUPA1300-2输出的图像数据通过LVDS接口以DDR方式输出,每24个像数为一个核单元,每一行总共有54个核单元。每个核单元按照一定的次序,分2次在12个通路中,以双倍数据速率串行输出。先输出第0、2、4…22个像数,再输出第1、3、5…23个像数,接着再输出47、45、43…25个像数,再输出第46、44、42…24个像数,以此类推,直至输出1行的所有像数数据[5]。数据通道与像素时钟的相位关系如图3所示。

FPGA 在接收到LUPA1300-2 的图像数据后,进过串行数据解析和像素重组,得到场标识信号iFVAL,行标识信号iLVAL和像素信号[11:0]iDATA,复位信号iRST,开始信号iSTART 和结束信号iEND,然后通过对这些信号的时序控制,接收到正确的图像数据。

最终在ModelSim 中仿真得到图像采集仿真图如图4所示。

图3 数据通道与像素时钟的相位关系Fig.3 The phase relationship of the data channel with the pixel clock

图4 图像采集模块仿真图Fig.4 The simulation of image acquisition modules

3 SDRAM 缓存设计

在实时显示图像信息时,尽管进行了抽帧,但数据处理量仍然很大,仅靠FPGA 内部的存储空间无法满足需求,需要高速、大容量的存储器来缓存图像数据,采用SDRAM 对图像进行缓存。但FPGA 的时钟,SDRAM 的时钟及VGA 的时钟均不相同,需要采用FIFO 将两个工作频率不同的器件进行数据的交互。FIFO 是一种先进先出的数据缓存器,分为同步FIFO 和异步FIFO 两种,异步FIFO 是跨时钟域系统设计中比较常见的模块组成,它的主要作用是使2个工作频率不同的器件在进行数据交互时实现数据的平稳传输[6]。

人眼的极限分辨时间为1/24s,每20帧抽取一帧,抽帧后帧频为25fps,此时RGB 格式图像的传输速率为117.187 5 MB/s。为满足实时性需求,SDRAM 缓存时,采用乒乓交替读入和写出完成数据的缓存,每个SDRAM 的容量需大于一帧图像的大小,即4.687 5 MB,存一帧数据需要的时间为0.04s。因此,选用的SDRAM 的容量应大于4.687 5 MB,读写速度应大于117.187 5 MB/s。设计中选用的2片SDRAM,型号为IS42S16320B,容量为64 MB,读写速度为286 MB/s。

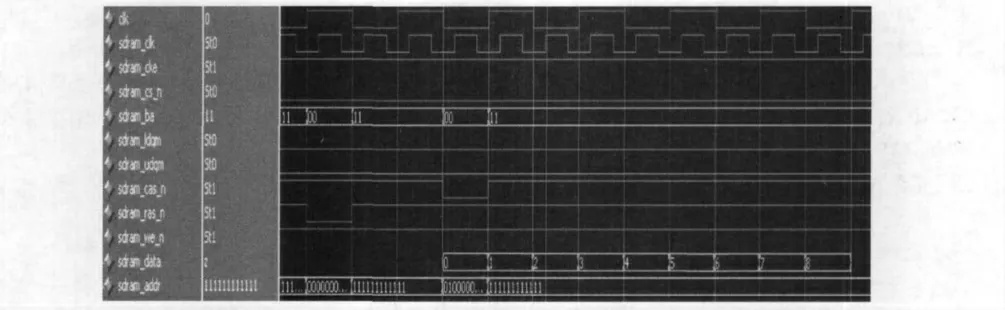

SDRAM 在上电时,首先要进行初始化,包括200μs的输入稳定期,L-Bank预充电,8次自刷新,模式寄存器设置。初始化完成后进入工作状态,其工作时序为空闲状态→行有效状态→行有效等待状态→读/写数据准备状态→读等待潜伏期→读/写数据状态→读/写完后预充电等待状态→空闲状态[7]。用ModelSim 对其读/写时序进行仿真,读操作与写操作的仿真图如图5和图6所示。

图5 SDRAM 读操作时序图Fig.5 The timing diagram of SDRAM read

图6 SDRAM 写操作时序图Fig.6 The timing diagram of SDRAM write

4 实时显示系统设计

VGA 时序控制模块的作用是将缓存于SDRAM 中的图像数据在VGA 显示器上实时显示。VGA 工作时采用逐行扫描的方式,扫描从屏幕的左上方开始,从左到右,从上到下,逐行扫描。每扫完一行,用行同步信号进行行同步,电子束对显示器进行消隐,并使其回到屏幕下一行的起始位置。当扫描完所有行时,用场同步信号进行场同步,使扫描回到屏幕左上方扫描起始位置。同时进行场消隐,并预备下一帧的扫描[8-9],图7所示为用ModelSim 所做的VGA 显示时序仿真图。

图7 VGA 显示时序仿真图Fig.7 The timing simulation of VGA display

在此时序图中,有VGA 时钟vga_clk,行有效信号hsync和帧有效信号vsync,在其都为高电平并且在VGA 时钟的上升沿输出图像颜色信息vga_r,vga_g,vga_b。

5 系统测试

为了验证系统设计的正确性,依据总体设计方案制作了采集、记录与显示电路,设计了采集软件,对运动目标进行实际拍摄。

在满分辨率条件下对静态物体(花盆)进行实时图像采集与显示,如图8所示,能够很清晰地将物体图像显示在显示器上。

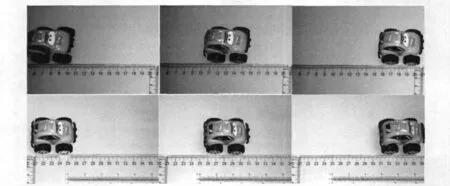

以电动小车为目标,移动速度约为4.5km/h,在一段时间内对小车的移动过程进行拍摄,选取其中连续的6幅图像进行分析,如图9所示。通过图9可以看出,本文所论述的500fps图像采集及实时显示系统能够完成对高速运动的目标进行高速的图像采集并实时显示,满足现场实时性的需求。

图8 静态图像采集Fig.8 Stationary image acquisition

图9 连续图像采集Fig.9 Continuous image acquisition

6 结 论

本文对分辨率为1 024×1 280的500fps高帧频图像采集及实时显示的关键技术进行了研究,提出了实现该技术的基本方案。在设计过程中对各模块进行仿真,验证其可行性,最终设计完成后对整个系统进行性能测试,实现了对视频图像的实时采集、缓存与显示,满足国防与科研试验中对高速视频采集与记录显示的需求。

[1] 杜 鹃.基于FPGA 的高帧频CMOS相机数据传输系统设计[D].西安:西安工业大学,2011:2-3.

[2] 杨莉珺,刘铁根,朱均超,等.基于CMOS图像传感器的嵌入式图像采集与格式转化[J].电子产品世界,2008(6):96-98.

[3] 侯宏录,杜 鹃.基于乒乓操作的千兆MAC中的FIFO 设计[J].光学仪器,2011,33(1):36-42.

[4] 杨会伟.高帧频CMOS相机图像采集系统研究[D].西安:西安工业大学,2009:10-13.

[5] 郭文豹.高速CMOS智能相机研究[D].长春:长春光学精密机械与物理研究所,2010:13-21.

[6] 张 涛.高帧频CMOS相机实时压缩与传输关键技术究[D].西安:西安工业大学,2012:24-25.

[7] 张文芳.基于FPGA 的SDRAM 控制器设计方案[J].兵工自动化,2012,31(2):57-60.

[8] 孙 艳,孙爱良,王紫婷.基于FPGA 的VGA 显示控制器的实现[J].自动化与仪器仪表,2008,6(7):106-107.

[9] 董 兵,朱齐丹,文 睿.基于FPGA 的VGA 图像控制器的设计与实现[J].应用科技,2006,33(10):42-45.