深亚微米CMOS 电路多电源全芯片ESD 技术研究*

杨 兵 ,罗 静,于宗光1,

(1.江南大学物联网学院,江苏 无锡214122;2.中国电子科技集团公司第五十八研究所,江苏 无锡214035)

大规模集成电路面临的一个普遍的可靠性问题是由ESD((Electro-Static-Discharge)静电引起的芯片失效问题,行业有足够多的报道及实践证明,至少35%的芯片失效是由ESD 失效引起的[1]。所以ESD 防护设计是值得电路设计师高度关注的一个焦点。并随着芯片制造工艺技术向亚微米、深亚米及纳米级发展,芯片的规模与复杂度呈指数级增长,ESD 防护设计受工艺、器件、电路以及系统等各个层面因素的影响越来越大,设计也变得更加复杂,且因为其设计与电路相关性极强,也是电路设计师所面临的一个关键设计挑战。常规ESD 设计往往在输入、输出PAD 以及电源、地PAD 附近放置ESD 防护结构,但即使已有这些适当的ESD 防护电路,仍会出现芯片内部电路因ESD 失效而发生的异常损伤问题[2]。近年来我们研制的多个电路实验也证明,常常带有ESD 保护结构[3-6]的端口在ESD 试验之后都很正常,但芯片内部已经出现很多问题。所以ESD 防护设计必须要注意全芯片防护架构的设计,才能够真正避免内部电路发生异常操作问题[6]。

1 ESD 保护原理

ESD 保护电路设计的目的就是要避免工作电路成为ESD 的放电通路而遭到损害,保证在任意两芯片引脚之间发生的ESD,都有适合的低阻旁路将ESD 电流引入电源线[8]。这个低阻旁路不但要能吸收ESD 电流,还要能箝位工作电路的电压,防止工作电路由于电压过载而受损。在电路正常工作时,抗静电结构是不工作的,这使ESD 保护电路还需要有很好的工作稳定性,能在ESD 发生时快速响应[9],在保护电路的同时,抗静电结构自身不能被损坏,抗静电结构的负作用必须在可以接受的范围内,并防止抗静电结构发生闩锁。

2 全芯片ESD 设计难点

2.1 芯片概况

全芯片ESD 方案验证电路是一款为某整机用户定制的专用VLSI 电路,采用SMIC 0.35 μm 2P4M Polycide 混合信号CMOS 工艺流片。电路内部集成有一个32 bit CPU、一个用户专用IP、两个全定制10 bit 模数转换、一个数字锁相环DPLL、64 kbit×32 SRAM、64kbit×32 ROM,还包括通用USB2.0 与CAN等接口模块,是一个典型的数模混合IC 芯片,规模约为150×104门,IO 端口391 个。该芯片采用双电源供电(5 V 与3.3 V),具有3 组不同电压的电源组及3 组地线组,由于多电源、混合电压的特性,给全芯片ESD 设计带来很高的设计难度。

2.2 全芯片ESD 设计难点

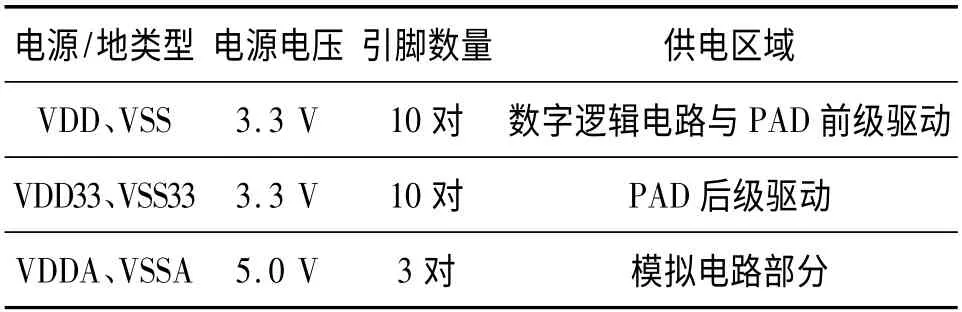

该芯片内部有3 组不同的电源,在片内电源铝线完全隔断;地线组也分为3 组,在片内铝线互不相连,但通过衬底相连,电源与地的分组情况如表1。通过对芯片工作模式分析,输出管脚上大驱动器上的快速翻转必将在电源总线上引入较大的噪声,为了减缓驱动器引起的电源噪声对芯片内部逻辑及端口TTL 电平的影响,两组3.3 V 的电源组(VDD33/VSS33,VDD/VSS)都被从压点分别引入芯片,鉴于模拟电路对噪声的高敏感性,需进行分开供电设计。

表1 芯片电源、地分组情况

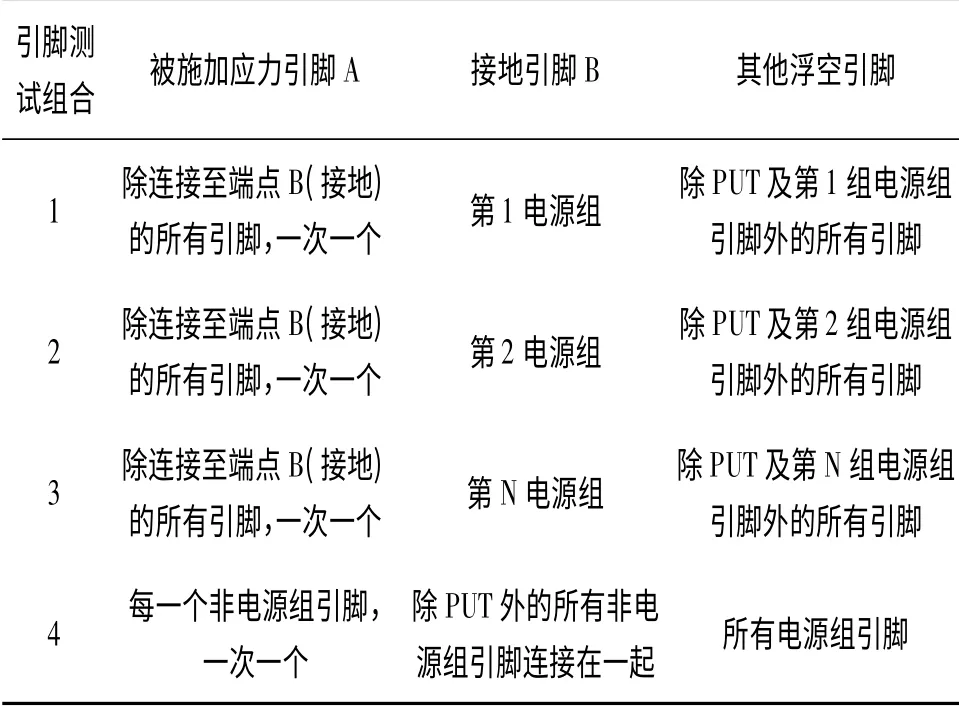

由于复杂的电源分组,使该芯片的ESD 设计相当地有难度。表2 是HBM(Human Body Mode)标准中给出的Ic 进行ESD 试验时的引脚测试组合说明。从这张表中我们可以看出,ESD 测试时,电源分组越多,ESD 测试组合就将越多。如果依照为每一种组合提供有效的ESD 电流泄放通路的原则进行全芯片ESD 防护设计,那么芯片的ESD 设计难度不言而喻了。

表2 集成电路ESD 引脚测试组合(Pin Under Test,PUT)

该芯片的3 个电源由于片内铝不相连,所以必须分为3 个电源组;3 个地线片内虽然通过衬底相连,但由于单晶材料衬底的电阻不会低于2 Ω,所以按标准规定也是必须分成3 个组。流片后的芯片地线之间电阻测量数据显示,VSS-VSS 间:1.8 Ω ~1.9 Ω,VSS-VSS33 间:8.6 Ω ~9.0 Ω,VSS-VSSA间:20 Ω ~21 Ω,VSS33-VSSA 间:23 Ω。这些数据足以说明通过衬底相连的3 个地线在进行ESD 测试时不能分为一组。

通过以上分析可知:该芯片将面临7 种ESD 测试组合((1)Al1-to-VDD;(2)Al1-to-VDD33;(3)Al1-to-VDDA;(4)All-to-VSS;(5)All-to-VSS33;(6)Allto-VSSA;(7)IO-to-IO),如果不仔细分析这些测试组合发生时ESD 电流的放电通路,并精心设计合理的ESD 防护结构,那么任何一个通路的问题反应为芯片的ESD 故障临界电压,后果就可想而知了。

同时全芯片ESD 的设计难点还体现在其他几个方面:必须在高电平与低电平之间提供合理的ESD 防护器件;不同电源、不同地线引脚之间既要提供足够多的防护器件,又需保证满足要求的噪声隔离;需要消除电源、地线寄生电容及电阻对ESD的负面影响;由于模拟电源及地引脚仅有一对,放置在芯片一角,所以ESD 防护结构加入时有难度,需要合理解决。

3 全芯片ESD 设计方案

全芯片ESD 设计思路按照先工艺、再器件、再电路3 个层次进行的:

(1)充分理解制造工艺ESD 方面的能力及局限,为全芯片ESD 设计做准备;

(2)理清芯片电源地线网络,并根据ESD 设计要求统一规划;

(3)根据ESD 测试组合基本原则,分析设计全芯片ESD 防护架构;

(4)结合目标工艺状况,决定有效防护器件的设计及选用;

(5)考虑电源、地线寄生电容及电阻的影响,合理安排防护电路在芯片中的摆放位置。

3.1 工艺ESD 评价分析

该电路流片基于Polycide 工艺,所以工程师无需考虑该工艺对ESD 的负面影响;同时工艺厂家也提供目标工艺的ESD 防护器件的特征化报告,并给出了详细的ESD 设计规则,因此工艺可保证无需采用ESD 注入版。基于这种针对ESD 有特别设计的生产工艺,工程师设计的重心将是对已有防护器件评价及选用、芯片特定所需防护器件的设计及全芯片ESD 架构设计。

3.2 ESD 防护器件设计

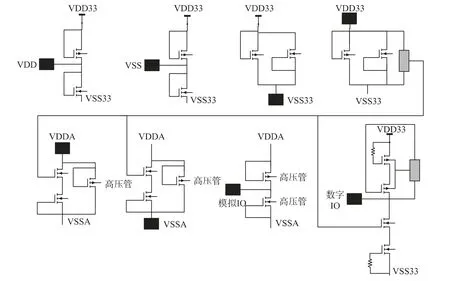

该电路采用全正向设计流程(模拟IP 除外),I/O 端口及标准单元部分逻辑直接采用目标工艺提供的库。根据经验及对目标工艺的分析,选用了库中如图1 所示一些ESD 结构实现整个芯片I/O 端口的保护及电源至地之间的保护。

图1 电路各端口压点ESD 结构

3.3 电源地线网络ESD 设计

该电路是大D 小A 型设计,模拟电路只占据芯片内核面积的2/7 大小,放置在芯片左下角,仅有一对电源组提供供电,并规划这组电源(VDDA)及地(VSSA)线仅围绕模拟模块布线。当进行Al1-to-VDDA 或All-to-VSSA 组合测试分析时发现,假设位于芯片右上角的引脚被破坏,向芯片左下角的VDDA 引脚放电,其放电路径将长得无法忍受,结果通常是端口未坏而电路内部已损伤。为了解决这个问题,设计时在芯片外围设计了一个宽为20 μm,由顶层铝线及其下一层铝线叠层设计的VDDA 环,尽量减小该环的寄生电阻,连接至片上唯一VDDA 引脚,并通过环再与芯片其他电源引脚之间放置多组电源至电源的保护电路。

3.4 多电源之间ESD 设计

由于不同组电源VDD33、VDD、VDDA 之间在片内是物理隔断,VSS33、VSS、VSSA 之问片内也没有铝线短接它们,仅通过衬底相连,如果在不同组电源间、地间不考虑直接的ESD 静电电流的泄放通路,极易导致片内损伤。所以在VDD 与VDD33,VDD与VDDA 之间都特别设计了专门的保护结构;同样,通过直接放置有效的PPP(Power-to-Power Protection)结构在VSS33 与VSS,VSS 与VSSA 之间,也可以提高整个芯片的ESD 水平。

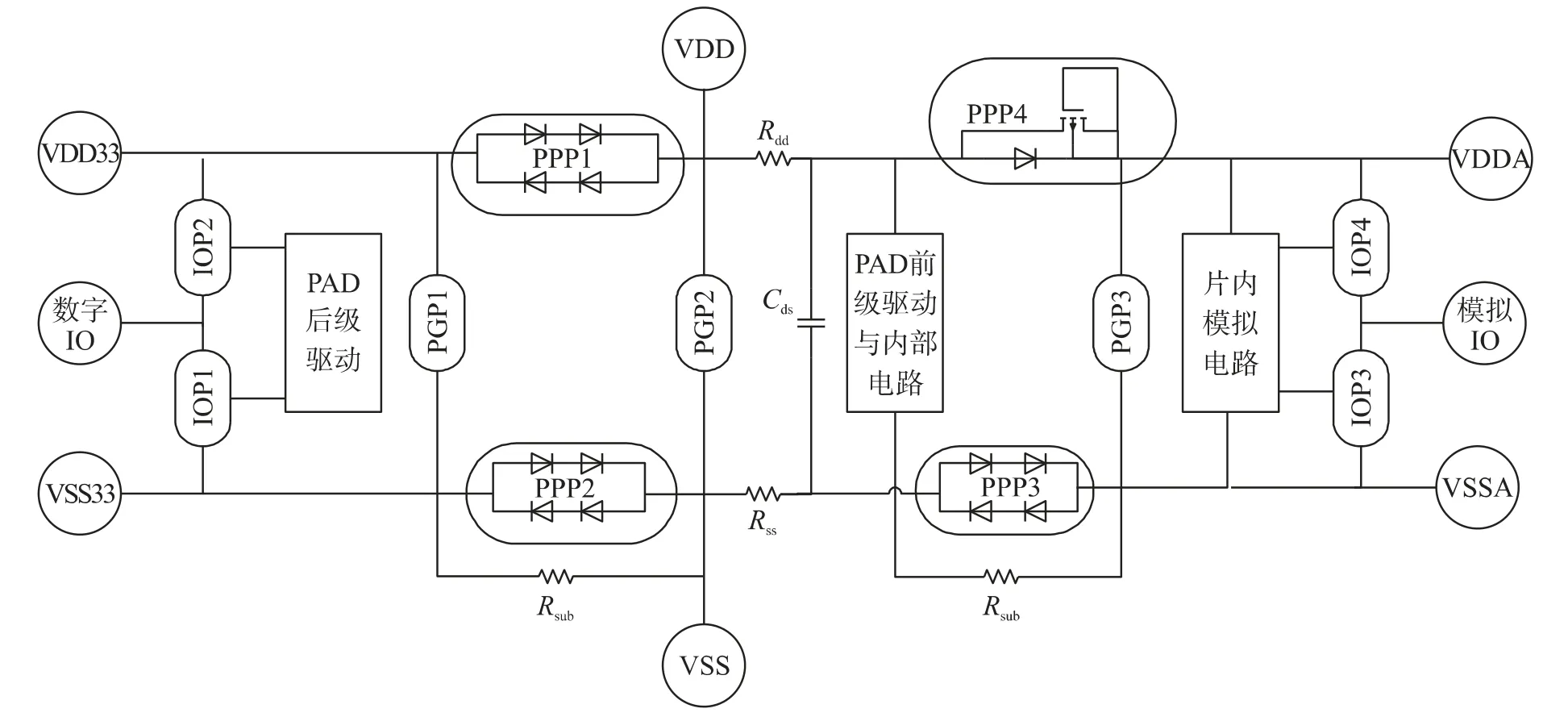

在防护结构的选择上,设计了阳极与阴极头尾连接的二极管串,将完全分离的电源线连在一起,详见图2。由于单向二极管串联后的导通电阻会影响ESD 静电电流泄放效率,所以虽然多级二级管串联对电源间的噪声隔离有益,在选择二极管串联级数时仍需慎重。设计时要参考工艺方面提供的二极管的特性参数,如一级、二级甚至更多级串联时的导通电阻及正向导通电压,同时结合电路情况平衡ESD防护与电源噪声隔离的双重需求。3.3 V 的VDD与5 V 的VDD33 之间采用了PMOS 器件,可见图2,在正或负ESD 静电打击时,该器件可以提供双向放电通路。

图2 全芯片ESD 防护构架

3.5 全芯片ESD 架构设计

该电路所采用的全芯片ESD 防护架构见图2,图中IOP(I/O Protection),PGP(Power-to-Ground Protection)及PPP 的标识用法借鉴了国外惯用做法。在完全了解了电路制造工艺ESD 能力与完成芯片电源/地线网络规划后,决定了全芯片ESD 防护架构,设计了有效IOP、PGP 及PPP 防护器件。但是全芯片ESD 设计还有一个较重要的方面需高度重视,研究结果显示,在内部芯片之间的电源与地,由于有很长电源线、地线寄生电阻、寄生电容的引入,将严重影响ESD 防护电路的有效性,所以必须合理安排防护电路在芯片中的位置。电路设计师必须估算被破坏引脚至接地放电引脚之间最长路径、最坏情况下的泄放通路上的寄生电阻,以保证其间放置了有效的ESD 保护电路。基于此原则,在该芯片外围端口之间的空余位置,每间隔2 000 μm~2 500 μm 处放置了多组“冗余”的ESD 防护电路,以达到消除电源线、地线寄生电容及电阻对ESD的负面影响。

4 实验结果与分析

全芯片ESD 方案验证电路为一款专用VLSI 芯片,芯片本身情况见本文3.1,电路内部具有数字与模拟电路两部分,采用双电源供电方式(5 V 与3.3 V),具有三组不同电压的电源组及三组地线组。该电路采用SMIC 0.35 μm 2P4M Polycide 混合信号CMOS 工艺实现,电路ESD 试验结果为HBM ESD等级达到了4 500 V,表明了该全芯片ESD 防护构架方案切实可行。

5 结论

全芯片ESD 设计是一个系统工作,芯片设计师应当谨慎地站在全芯片角度上,系统地考虑ESD 防护设计。本文提出了全新的深亚微米CMOS 电路多电源全芯片ESD 方案,流片试验表明具有良好的ESD 防护效果,但存在的缺憾是由于方案复杂必然占用较多的芯片面积,希望在以后的研究中进行改进。

[1] Ker Ming-Dou. Whole-Chip ESD Protection Design with Efficient VDD-to-VSS ESD Clamp Circuits for Submicron CMOS VLSI[J].IEEE Trans.on Electron Devices,1999,46(1):34-37.

[2] Dabral S,Aslett R,Maloney T. Designing on-Chip Power Supply Coupling Diodes for ESD Protection and Noise Immunity[C]//EOS/ESD Symp,1993:239-249.

[3] ATLAS User’s Manual,Silvaco Internationa1[S]. USA:San-ta Clara,2005.75-79.

[4] Amerasekera A,Duvvury C. ESD in Silicon Integrated Circuits[M].John Wiley & Sons,1995:18-27.

[5] Feng H,Zhan R,Wu Q,et al. Mixed-Mode ESD Protection Circuit Simulation-Design Methodology[C]//Proceedings of the International Symposium on Circuits and Systems,2003(4):652-655.

[6] 姚立真.可靠性物理[M].电子工业出版社,2004.

[7] 朱志炜,郝跃,马晓华.一种改进的片内ESD 保护电路仿真设计方法[J].电子器件,2007,30(40):1159-1163.

[8] 张建人.MOS 集成电路分析与设计基础[M]. 电子工业出版社,1996.

[9] 王雯,钱钦松,孙伟锋. TLP 应力下gg-NMOS 瞬态特性分析[J].电子器件,2008,30(40):1816-1818.