SOC 中嵌入式存储器阴影逻辑的可测性设计

施文龙,林 伟

(福州大学福建省微电子集成电路重点实验室,福州350002)

集成电路已经发展到了系统芯片SOC(System On Chip)时代,芯片集成度越来越高,结构越来越复杂,对集成电路测试又是芯片设计不可或缺的重要环节,测试的可行性、有效性以及测试功耗,极大地影响了芯片设计的成本与上市时间。嵌入式存储器是芯片设计的关键部分,是系统芯片中集成密度最高的器件,同时又是对制造过程中存在的缺陷最敏感的器件之一。各种类型的存储器在当前的SOC 设计中已经被广泛应用,占用了SOC 系统大部分面积[1]。针对SOC 芯片设计中存在着的嵌入式存储器模块,传统的固定故障模型不适合用于对存储器模块进行测试。因此,对于使用自动测试图形生成ATPG(Automatic Test Pattern Generation)工具用固定故障模型进行测试时,通常把嵌入式存储器模块当作“黑盒子(black box)”处理[2]。在黑盒子模型中,所有的输入都被禁止,所有的输出都被置为未知状态X,于是,存储器模块的输入引脚前与输出引脚后就存在着两块不可观察或不可控制的组合逻辑,这部分不可测试的组合逻辑就称为存储器阴影逻辑。由于存储器模块被简化成只含有输入引脚与输出引脚的无功能黑盒子,ATPG 工具产生的测试图形无法顺利通过该模块,阴影逻辑的故障不能被传递,所以无法被检测出来,ATPG 工具只能完成对扫描链路中的寄存器单元以及不包含阴影逻辑的外围组合逻辑电路进行控制和观察测试。当芯片中集成了更多、更大的嵌入式存储器模块,大量的不可测试的阴影逻辑会在很大程度上影响测试覆盖率,造成故障覆盖率低于设计要求。因此,阴影逻辑的影响不能忽视。

覆盖率的提高主要需要提高改善设计的测试可观测性和测试可控制性[3]。可测性设计DFT(Design For Test)就是为了确保复杂设计能够得到全面彻底地测试而提出的。其思想是在设计的初期就考虑芯片的测试问题,通过增加测试逻辑完善设计,把难测或者不可测故障转变为易测、可测的故障,争取在芯片设计前端就解决棘手的测试问题。可测性设计技术有多种结构,目前应用最广泛的可以有效提高芯片可测性的实现方法是基于扫描结构的可测性设计。扫描设计具有结构简单、对芯片的面积影响较小、测试覆盖率高以及可以与EDA 工具紧密结合等特点[4]。

1 基于扫描结构的可测性设计原理

1.1 设计原理

在集成电路设计中都含有大量的时序电路,时序电路的测试生成相当复杂,生成的测试图形非常多,因此测试施加时间也就相应长,而且很难对电路内部节点设置逻辑值,电路的内部状态则难以观察,测试起来非常复杂。扫描设计的提出,为时序电路的测试提供了可能[5],其基本原理是将电路中的时序元件替换成具有扫描能力的扫描寄存器,然后将它们连接起来形成扫描链,为时序元件增加了控制点和观察点,从而可以改善电路的可控性和可观察性[6]。

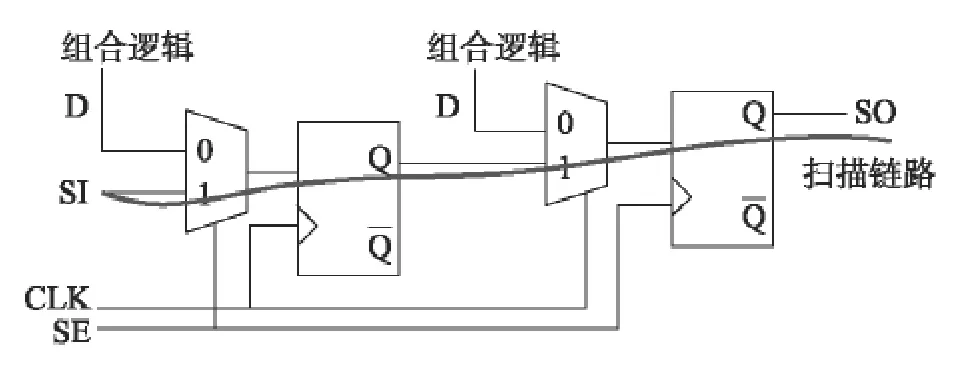

扫描设计的具体实现方式为:每一个触发器前面都接入一个两输入的多路选择器,其中一个输入接到前一个触发器的输出,另一个输入接到原始设计中所接的信号,即把普通寄存器转化为扫描寄存器[7]。这些修改的时序元件一个接一个串在一起形成移位寄存器,所有扫描寄存器的控制线都连接到一起,称为扫描链或扫描路径[8-9],这些时序元件连到扫描链中就形成扫描可控和扫描可观察。如图1 所示,SI 表示扫描输入,SE 表示扫描使能控制线,CLK 表示时钟输入端口,D 端口表示正常的数据输入端口,第一个寄存器的输出Q 接到第二个扫描寄存器的多路选择器的输入,最后一个寄存器的输出标记为扫描输出SO,形成扫描链路。当一个时序元件通过串行移入一个特定的逻辑值(0 或1)可以被设置成一个已知状态,那么这个时序元件是扫描可控的,ATPG 工具就把这个扫描可控元件作为伪原始输入。当一个时序元件的状态通过串行移出数据端口可以被观察到,那么这个时序元件是扫描可观察的,ATPG 工具就把这个扫描可观察元件作为设计的伪原始输出。通过伪原始输入,扫描路径能够实现对所有组合模块的输入控制;通过伪原始输出,扫描路径能够把所有组合模块的逻辑值传递到输出可观察。

图1 扫描设计结构图

扫描测试分为3 个步骤,首先是扫描移入(shift in)操作,将设计中的时序元件设置为期望的目标值,这个过程需要与内部最长扫描链长度相同的时钟数,扫描使能SE=1,电路工作在扫描移位测试状态。然后是给电路施加测试向量并捕获(Capture)响应,此时扫描使能SE=0,电路工作在正常的功能状态。最后对捕获的组合逻辑部分的响应执行扫描移出(Shift out)操作,扫描使能SE=1,电路工作在扫描移位测试状态。

扫描设计的显著优点就是把设计中的普通时序元件替换为扫描元件,从而把对时序逻辑电路的测试转变成对组合逻辑电路的测试,使得测试图形生成变得十分容易,处于扫描路径上的触发器不仅可以串行地移入所需要设置的电路状态,也可以把电路状态串行地移出去,最后实现对故障点的可控可观察。

1.2 存储器阴影逻辑DFT 方案

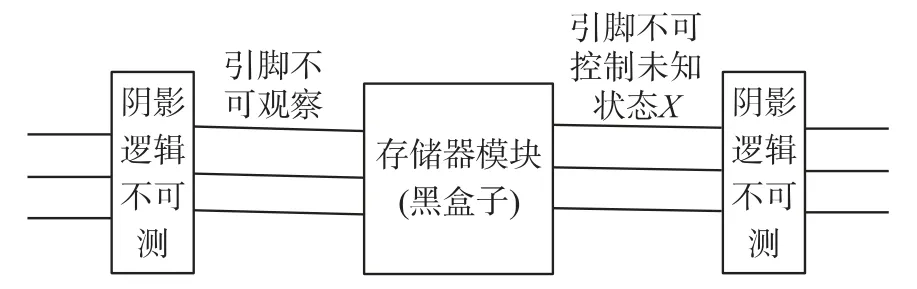

由于芯片设计中的嵌入式存储器模块在扫描插入时将作为黑盒子处理,因此在这些模块周围将为出现无法检测和控制的阴影逻辑,其结构图如图2 所示。

图2 嵌入式存储器阴影逻辑结构图

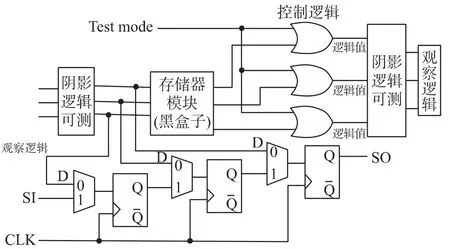

图3 阴影逻辑测试结构图

针对设计中出现的存储器阴影逻辑不可测试情况,通过适当增加测试点的方式,使原来不可控和不可测的逻辑变化反映到扫描链寄存器上,使其变得间接可控和可观测,从而提高整个系统芯片的测试覆盖率。如图3 所示,在存储器数据和地址引脚周围构造观察逻辑,观察逻辑为存储器输入引脚周围的阴影组合逻辑提供了一条通路,使得阴影逻辑的固定故障可以传递到观察点上;在存储器输出引脚周围构造控制逻辑电路,控制逻辑为存储器输出引脚周围的阴影逻辑提供了可控信号,使得输出引脚后的阴影逻辑有了具体逻辑值,不再是原先的X 状态,从而实现了故障传递。在测试模式下,ATPG 工具很容易就可以把阴影逻辑故障传输到扫描链观测点寄存器上。

2 在数字信息安全芯片设计中的应用

2.1 设计过程

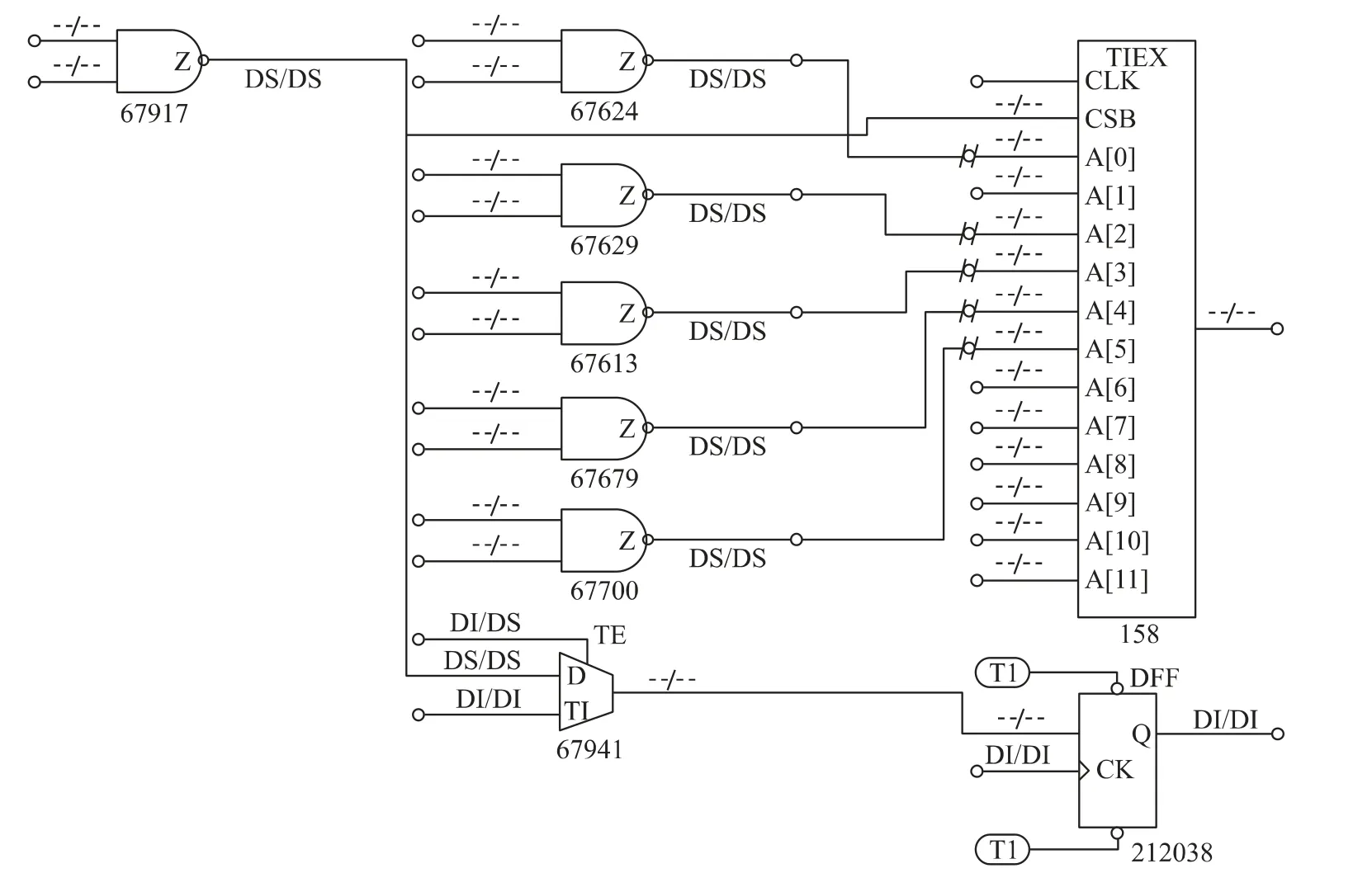

在本次设计的数字信息安全芯片中,以ROM模块为例,该模块的输入引脚有CLK,CSB,A[11:0],输出引脚D[31:0]。其阴影逻辑实现可测的具体实现方式:针对该ROM 存储器输入引脚前的阴影逻辑,在输入管脚添加一个带有选择端的寄存器,当控制信号TE 为0 时,电路工作在正常逻辑功能状态下,功能逻辑传递正常的输入数值,当控制信号TE 为1 时,电路工作在扫描测试模式下,通过在测试链预置相应的值进行移位操作过程,之后给电路施加激励向量并实现捕获,最后移到扫描输出端进行观测。在这种方式下,存储器前的阴影逻辑的故障完全得到测试,ATPG 工具测试报告如图4 所示。

图4 ROM 存储器前添加观察寄存器后ATPG 报告图

图4中DS 与DI 分别为Detected by Simulation 和Detected by Implication 的缩写,表示该点可测试。DS/DS 表示固定故障0 和固定故障1 都可测。

针对该ROM 存储器输出引脚后的电路逻辑,使用或门与测试模式信号Testmode 进行或操作,当测试模式信号Testmode=0 时,电路处在正常功能状态,当测试模式信号Testmode=1 时,电路工作在测试模式下,通过测试信号控制存储器输出端,使得原先不可控输出变为可控,如图5 所示,与ROM 输出引脚连接的或门后的组合逻辑部分都实现了可测试。

图5 ROM 存储器输出引脚添加控制逻辑后ATPG 报告图

对于芯片设计中其它的嵌入式存储器模块如SRAM,FLASH 等,采用类似的方法,使用DFT 工具插入测试点,在该数字信息安全芯片设计中的所有嵌入式存储器周围一共插入了442 个测试点(如表1 所示)。

表1 DFT 测试点插入报告

2.2 测试报告结果分析

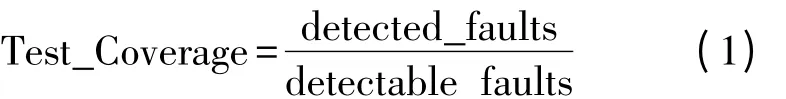

测试覆盖率(Test Coverage)是反应测试图形质量的最有效的手段,其计算公式为:

故障覆盖率(Fault Coverage)定义了检测出的故障占总故障的百分比,其计算公式为:

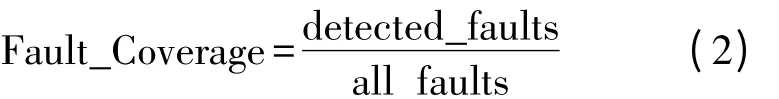

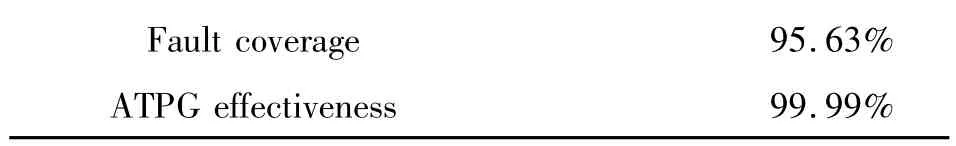

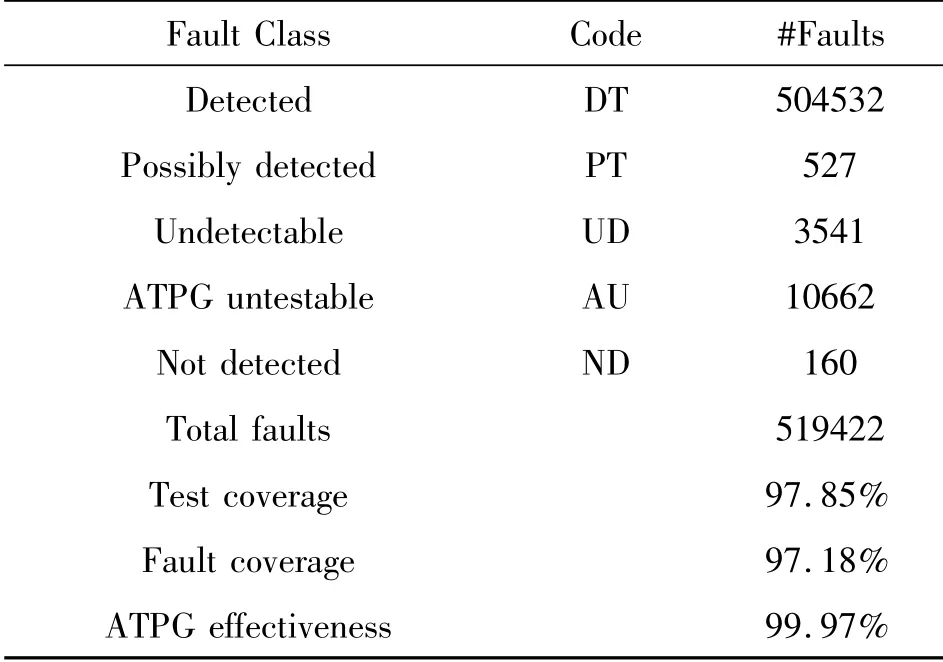

测试覆盖率和故障覆盖率是测试技术有效性的重要度量方法,是用来表征测试完整性的重要手段。在该数字信息安全芯片设计中,针对嵌入式存储器阴影逻辑增加适当的观察寄存器和控制逻辑后,故障覆盖率较原先设计得到了改善。表2 为修改设计前ATPG 工具测试报告,表3 为修改设计后ATPG工具的测试报告。

表2 设计前的ATPG 测试报告

?

表3 改进设计后的ATPG 测试报告

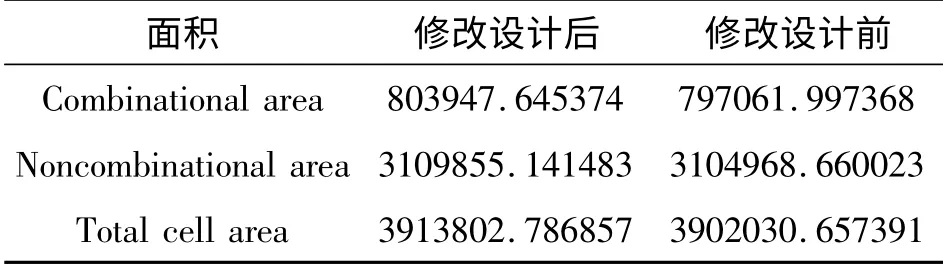

比较后可以看出,该方法使得测试覆盖率提高了1. 59%,故障覆盖率提高了1. 55%,达到了97.18%,芯片的可测性有了很大的提高。设计前后芯片的面积如表4 所示,该方法对芯片面积影响甚微,最后测试了全芯片的功耗为137.9013 mW,满足低功耗要求。

表4 修改设计前后芯片面积报告单位:μm2

3 结束语

本课题介绍了SOC 中嵌入式存储器阴影逻辑在固定故障测试时的不利影响,深入分析了基于扫描结构的可测性设计原理的测试应用,提出了一个测试阴影逻辑的有效方法,对于降低芯片测试成本,提高产品的可用性指标,减少产品的维护费用具有重要意义。本设计虽是针对一个具体数字信息安全芯片的应用,但具有普遍性意义。在实际项目中,测试工程师还需要明晰设计的功能测试结构,要注意测试控制信号的选择是否与测试模式相匹配,否则无法完成相应的测试期望,对于某些阴影逻辑不能使用DFT 工具自动插入测试点的,要尽早与设计工程师进行协商,将测试电路写入RTL 中。

[1] 雷绍充,邵志标,梁峰. 超大规模集成电路测试[M]. 北京:电子工业出版社,2008.

[2] Synopsys Inc.Synopsys Online Documentation[CP/DK].2010.

[3] Hao Zhang,Wally Li. Design for Test with DFT-MAX Adaptive Scan in Low Power Design[EB/OL]. http://www. synopsys.com.cn/information/snug/2006-collection/design-for-test-with-dft-max-adaptive-scan-in-low-power-design,2006.

[4] 刘文峰.全扫描结构在MCU 设计中的应用[EB/OL]. 中国科技论文在线,http://www. paper. edu. cn/index. php/default/releasepaper/content/200702-30,2007-02-03.

[5] 成立,王振宇,高平,等.VLSI 电路可测性设计技术及其应用综述[J].半导体技术,2004,29(5):20-34.

[6] 克拉茨.数字集成电路与嵌入式内核系统的测试设计[M]. 何虎,马立伟,等译.北京:机械工业出版社,2006.

[7] 唐玉兰,于宗光,李天阳,等.一种改进的基于扫描的电路设计[J].微计算机信息,2006,22(2):235-237.

[8] 刘峰,梁勇强.大规模集成电路可测性设计及其应用策略[J].玉林师范学院学报,2005,26(5):29-33.

[9] 陆思安,史峥,严晓浪.面向系统芯片的可测性设计[J]. 微电子学,2001,31(6):440-442.