用于FPGA的多层次集成设计系统的设计与实现

张 峰,李 艳,韩小炜,李 明,张倩莉,陈 亮,吴利华,张国全,刘贵宅,郭旭峰,杨 波,赵 岩,王 剑,李建忠,于 芳,刘忠立

中国科学院微电子研究所,北京100029

现场可编程门阵列 (field programmable gate array,FPGA)通过软件编程对硬件结构和工作方式进行重构,从而使硬件设计如同软件设计一般便捷.这极大地改变了传统的数字系统设计观念、过程和方法.随着新一代FPGA芯片工艺和设计方法的进步,以及新的应用领域和市场需求的变化,电子设计自动化(electronic design automation,EDA)技术亦有长足发展,总趋势可概括为:跨越器件类型,跨越公司界限,设计理念日益人性化,越来越高的优化水平,越来越快的仿真速度,越来越高的仿真精度及完备的分析验证手段.一体化的工具使用户受益于一个统一的用户界面,避免了在不同的工具间进行数据转换等繁琐操作.目前,各大EDA工具供应商分别推出了集成众多工具在内的一体化设计工具,如 Xilinx公司的 ISE和 Altera公司的Quartus II,国内亦有京微雅格(原雅格罗技,Agate Logic)的Primace EDA软件、北京飘石科技有限公司(Uptops)的FPGA开发系统HqFpga和复旦大学的FDE等.但是上述集成开发平台都侧重在FPGA的开发应用,不具有FPGA芯片设计方面的功能.

本研究设计开发出一套用于FPGA的多层次集成设计系统 (versatile design system,VDS).该系统除具有电路设计功能外,还集成了芯片生成、系统级设计及芯片和应用的仿真验证等功能,集成度高.其中,全自动芯片生成功能可帮助用户快速设计适于自用的FPGA,大幅降低芯片开发难度,提升开发效率.VDS集成了具有导航功能的FPGA设计工具,通过部分人为干涉的方式实现了对软件的完全可控,完成了全芯片测试,同时可实现软件设计过程中的容错功能.VDS集成开发环境的编程语言是Python+wxPython,内核为C/C++、perl.整体设计思想是充分利用Python语言的动态特性,构造灵活又易于扩充的软件体系,可实现不同集成层次设计系统的快速定制.

1 VDS体系架构

图1为VDS用户图形界面,它是一个用于FPGA多层次设计的集成开发平台,包括FPGA芯片生成工具VBK(versatile build kit)、FPGA设计工具VDK(versatile design kit)、FPGA系统应用工具VAK(versatile application kit)和 FPGA验证工具VVK(versatile verification kit).各组件的调用可在一个友好且统一的图形用户界面(graphical user interface,GUI)进行.根据VDS中各组件个数和组合方式,可快速定制各种不同集成层次的设计系统.

1.1 VDS编程思想

VDS集成开发环境基于开源文本编辑器Ulipad,其编程语言为python+wxPython.采用wxPython软件可使VDS实现跨平台运行.Python语言的动态特性有益于VDS构造易于扩充且灵活的软件体系.实际开发时则全部采用Mixin和Plugin的设计与开发方法,即分布式类编程技术.

1.2 工程管理

VDS为FPGA设计提供项目工程和设计流程的管理.图1中工程管理窗口使用多Tab页结构,通过Tab页切换实现VBK、VDK、VAK和VVK各组件间的切换.各组件都是互相独立的集成开发系统.同时,这4个组件又紧密联系,可实现互调与资源共享.VBK生成的芯片可供VDK和VAK使用;VDK可辅助VBK完成FPGA架构评估;VBK、VDK和VAK可随时调用VVK进行仿真和验证;调用VDK中的软件可辅助VVK完成板级测试.

2 FPGA芯片生成工具VBK

在实际应用中,通用型FPGA的逻辑资源利用率通常都处于较低的水平,FPGA内部总有不少闲置电路.这部分闲置电路除构成FPGA的成本外,亦导致其性能降低.因此,通过细化市场,针对特定的应用领域优化FPGA结构,以灵活性的降低,换取FPGA效率和性能的提升成为FPGA的一个重要发展方向.现主要有两种实现方式:一是在FPGA中增加和特定应用相关的电路模块[1];二是按某一类特定需求优化FPGA布线架构[2].

但不同应用要求千差万别,采用传统的方法设计适用于不同应用的FPGA芯片和与之配套的EDA工具耗资耗时,得不偿失.为此,VBK的设计旨在提供一种快速FPGA芯片设计方法,使用户能根据自身需要灵活控制芯片规模和功能,快速将针对特定应用优化的FPGA架构转化为FPGA芯片版图,从而缩短FPGA芯片的开发时间,使快速开发适应不同应用的FPGA成为可能.

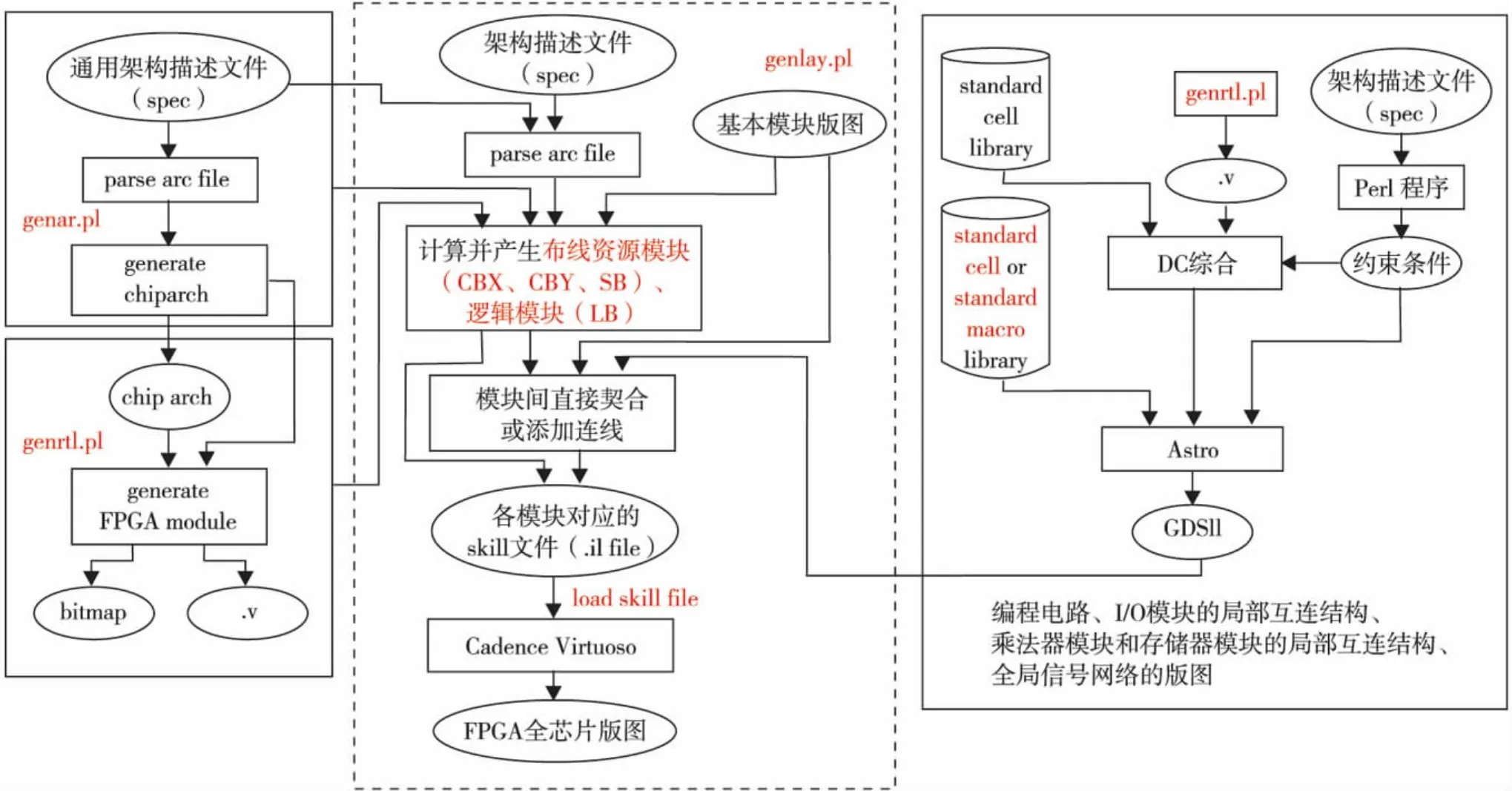

VBK包括FPGA芯片设计和验证的流程,适于体硅CMOS工艺和SOI-CMOS工艺的芯片.本研究使用VBK设计实现VX1000和VS1000两款芯片.VX1000采用0.18 μm体硅 CMOS工艺,5万门,系统时钟达326 MHz;VS1000采用0.5 μm SOICMOS工艺,5万门,系统时钟达100 MHz.虽然这两款芯片规模偏小,但VBK的设计方法具有普适性,对芯片规模无限制.图2为VBK流程图.

图1 VDS用户图形界面Fig.1 VDS graphical user interface

2.1 FPGA芯片设计

FPGA芯片设计指FPGA架构设计和FPGA芯片本身从行为级到晶体管级,再到版图级的具体设计实现.设计FPGA芯片是一个非常复杂和耗时的工作,高度自动化的辅助设计工具可高效实现面向应用的FPGA芯片设计.

图2 VBK流程图Fig.2 The flowchart of VBK

2.1.1 FPGA架构设计

FPGA架构设计是对架构描述文件[3]进行详细的解析,产生FPGA详细的结构和布线资源图,以期找到更好的FPGA架构参数或一系列架构参数的组合,以使FPGA在应用中具有更高的面积利用率和性能.VBK调用FPGA架构文件编辑查看器(view/edit architecture,VAR)来实现半自动设计FPGA架构的功能,通过修改架构描述文件中的相关参数,可改变芯片规模,各基本模块的类型、数量、位置、尺寸,布线结构的类型,I/O类型和数量等,使用户能根据自身需要灵活控制芯片的规模和功能,从而可快速定义适应不同应用的FPGA.架构文件生成后,通过调用genar.pl实现架构转换,产生对应不同应用领域的架构描述文件.然后,建立布线资源图.通过调用VDK,在布局布线后对FPGA架构进行评估,评估标准为面积延时积是否最小.最后,自动产生包含所有配置位的组织形式bitmap文件,从而确定整个芯片的结构和模块间的连接关系.

2.1.2 模型生成

通过 genrtl.pl生成整个芯片的行为级模型[4](verilog HDL),该模型不但可以作为原型对芯片功能进行仿真,更是后期版图设计的输入文件,也是将来验证版图正确性的标准;通过gencdl.pl生成的晶体管级模型 CDL[5](circuit description language)网表,可以用来对芯片进行晶体管级的仿真,验证电路的性能,同时还可以用来和自动产生的整个芯片的版图进行LVS(layout versus schematic)验证.

图3 FPGA全芯片版图自动化设计流程Fig.3 Automatic design flow of FPGA full chip layout

2.1.3 版图生成

FPGA版图自动化设计方法在学术界有很多研究,如文献[6]中采用ASIC的设计方法来设计FPGA,Jonathan Rose率领的研究小组开展了一个名为GILES[7]的研究项目.但以上研究主要采用版图拼接的设计方法,即自动化一个单元块版图的设计,并依靠拼接该单元块版图组成FPGA阵列的版图.这种方法不适用于包含宏块的异质FPGA结构,因为在异质结构的周围,布线资源的规则性已被破坏.为此,VBK提供了参数化的异质结构FPGA全芯片版图自动产生与集成方法,其目标是从FPGA芯片的架构描述文件开始,经过EDA工具对其进行详细的解析,从而生成整个芯片的实际版图[5].全芯片版图自动化设计流程如图3.其中,genlay.pl是用来自动产生并集成整个芯片版图的,它主要是根据芯片架构描述文件及genar.pl和genrtl.pl这两个工具产生的芯片各个模块结构与互连关系的一系列数据库,由一些基本的已经手工画好版图的模块来自动组装成布线资源模块 (CBX、CBY和SB)、逻辑模块 (LB)的版图.同时有些部分 (如编程电路)的版图是由基于标准ASIC设计流程自动布局布线产生的.待所有模块的版图产生后,通过程序计算各模块的位置,然后将各模块自动契合或通过添加连线组装起来,最后形成整个芯片的版图.其中,由genlay.pl产生的各模块和整个芯片的版图是以skill文件格式表示的,在Cadence Virtuoso环境下载入这些skill文件,最终形成实际可见的版图.

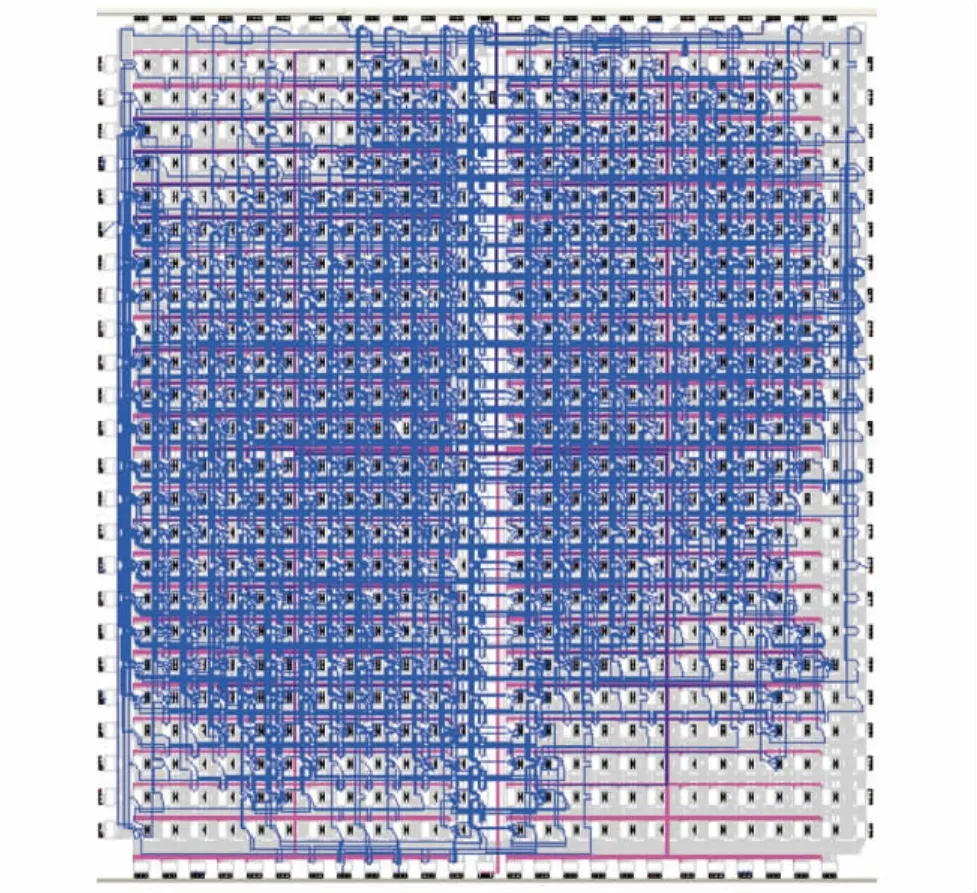

在Intel Core 2 Linux工作站运行本研究设计的版图自动化生成工具,可在约48 h内自动生成一款规模相当于Xilinx XC3S50,但乘法器阵列规模是其4倍的FPGA芯片的版图,而工业界要手工来完成此规模芯片的版图需将近100人/年.图4为使用VBK设计实现的具有自主知识产权的FPGAVX1000的全芯片版图.

图4 VX1000全芯片版图Fig.4 Layout of VX1000

2.2 FPGA芯片验证

VDS提供的芯片验证主要包括DRC、LVS、全芯片仿真和板级测试.

3 FPGA芯片设计工具VDK

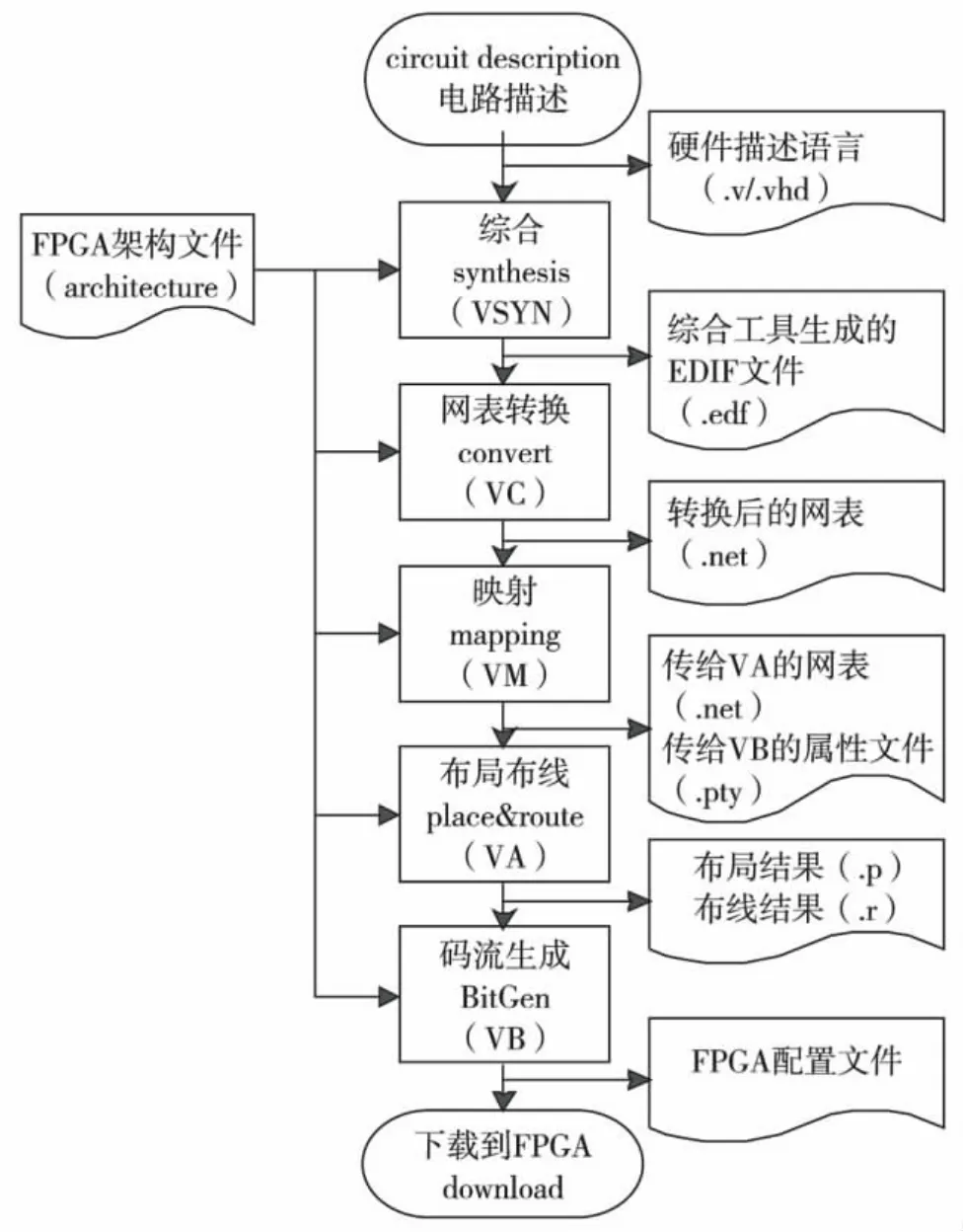

VDK提供了使用FPGA实现逻辑设计的功能,支持VX1000和 VS1000[8]两款芯片.图5为 VDK的EDA设计流程.

电路描述.VDK支持Verilog HDL设计输入.

图5 VDK设计流程Fig.5 VDK design flow

综 合.VDK有3种综合工具可选,分别是采用VSYN(versatile synthesis)、第三方综合工具Synopsys的Synplify和Xilinx的XST.VSYN是基于开源项目 Icarus[9]和 ABC[10]开发的逻辑综合工具.VSYN接受Verilog HDL设计文件,经过HDL解析与确立、逻辑优化、工艺映射和合并算法优化后,生成LUT(look up table)和FF(flip flop)级别的网表.工艺映射主要采用优先截 (priority cut)算法[11]和基于最大基数匹配 (maximum cardinality matching)的合并算法[12].与ABC相比,在不影响时序性能的情况下,VSYN所耗LUT数大减.

网表转换.VC(versatile convert)将第三方综合工具的输出网表转化为目标FPGA支持的结构单元网表.该过程相当于对网表进行二次工艺映射.

映 射.VM(versatile mapping)采用基于TVpack算法[13]的优化算法,对多输入模块和快速进位链的打包进行分类处理,最大化提升逻辑资源使用率和布通率.从MCNC的测试包中选取基准电路在资源占用方面比较ISE与VM,结果显示,对只含LUT的网表和同时包含LUT和FF的网表,VM的资源占用分别提高2%和9%[14].

布局布线.VA(versatile place and route)基于VPR4.3[15],布局采用模拟退火算法,布线采用路径搜索算法.VA实现了一种导航布局布线方法,在布局布线过程中,用户可根据需求指定逻辑单元块的位置和信号路径,从而控制布局布线结果.VA还实现了针对部分漏端指定路径的线网的布线方法,相对直接忽略指定路径的布线方法,该方法平均可减少22.6%的迭代次数和20.9%的关键路径延时,能有效提高布局布线的性能[16].图6是针对一个基准电路所做的布局布线结果.

图6 一个基准电路的布局布线结果Fig.6 A graph of place and route result of a benchmark circuit

码流生成.码流生成工具VB(versatile bitstream generation)接收VA的布局布线结果、VM的逻辑网表及芯片架构描述文件,产生二进制配置文件[17].该文件包含FPGA的所有配置信息,包括互连网络的连接、逻辑模块工作模式及初始值.

下 载.VT(versatile testing)将配置文件下载到FPGA器件中,FPGA中的配置电路按照读入的配置文件配置FPGA的可编程开关和各基本模块,最终完成FPGA电路结构的配置.VT还可实现readback、verify和测试功能.

原来,陆叔叔和妻子牟月原本都是蜡像师,一个偶然的机会,他们制作的一家三口的生活场景的蜡像被发到了网络上,一时间成了红人。身为商人的李总感觉这是个商机,就主动找到他们,投资兴建了这两栋小楼。双方签了合同,夫妻二人专心创作,李总负责运营。

迭代性的形式化验证.VDK通过调用Synopsys的形式化验证工具Formality来验证设计[18].GenV应用程序读入VDK的每个子流程的输出网表,生成格式统一并与Formality兼容的Verilog网表.Formality读入前一阶段的Verilog网表作为参考设计及本阶段的Verilog网表作为实现设计,采用形式化方法验证两个设计的功能等效性.验证成功后,当前阶段的实现设计将成为下一个阶段的参考设计.由于在流程中使用了最近的设计作为参考设计,整个验证所需运行时间将会减小.

4 FPGA芯片应用工具VAK

随着半导体工艺技术的发展,FPGA日益强大,但也更加复杂,从而大幅增加了其设计难度.大规模的设计协同、子系统规划、时序收敛处理、不同IP调用等都给工程师带来了更多的挑战.VAK的目标是以IP及系统为中心,使用标准单元库里的晶片、微处理器和嵌入式外设核,实现从硬件到软件设计的整个嵌入式系统设计,从系统级层面实现FPGA,完成可编程片上系统芯片(system on a programmable chip,SOPC)的设计,从而带来生产效率的大幅提升.VAK提供RTL IP封装技术、标准IP封装、图形化IP集成功能和各类系统构建块的系统集成技术.并为用户提供设计分区的功能,这样多个团队可并行设计,最终完成大型项目的研发.

5 FPGA芯片应用工具VVK

随着制造工艺的不断改进及FPGA芯片规模和应用领域的不断扩展,FPGA验证测试工作的复杂度和难度亦不断增加.VVK设计旨在对FPGA芯片和应用做各种级别的仿真、验证、芯片编程与调试,为芯片和应用能正常工作提供可靠保障.

5.1 VVK的应用测试功能

VVK对应用测试提供了slave serial fault test、master serial fault test和JTAG测试3种模式.

5.2 VVK的芯片仿真功能

VVK提供了全芯片半自动仿真脚本程序,使全芯片可在行为级、开关级、晶体管级、混合模式(晶体管级+寄存器传输级或晶体管级+开关级)4种模式下进行快速仿真.在提高仿真速度又保证精度不失的情况下对全芯片进行快速仿真验证.

图7给出了对VS1000芯片进行半自动仿真的流程图[19],全流程由cltchip.pl控制.genctlchip.pl主要负责搭建仿真平台、产生全芯片网表,以及其他仿真文件的准备,最后由runsim.pl启动仿真.仿真流程为:① 输入仿真命令,启动ctlchip.pl,开始仿真流程;②基于测试实例和芯片架构文件,通过VDK产生仿真需要的码流文件.bit、回读文件.rbb和验证掩模文件.msk;③全芯片仿真验证平台的搭建,主要包括仿真控制模块(ctl.v)、测试电路模块(tb.v)、全芯片网表和仿真配置文件;④调用第三方工具Modelsim进行仿真.

图7 半自动仿真脚本流程Fig.7 Semi-automatic simulation process

5.3 VVK的芯片验证功能

在对FPGA各种模块,包括 IOB、LB、CHB、GB和PGM进行电路设计和版图设计后,都可进行仿真验证 (CoSim)和后端验证 (DRC和LVS).在此基础上,将各个模块的版图进行拼接,完成全芯片版图[5].VVK通过调用 Cadence Virtuoso设计平台的在线验证工具Diva和Mentor Graphics公司的Calibre对全芯片版图进行双重验证.

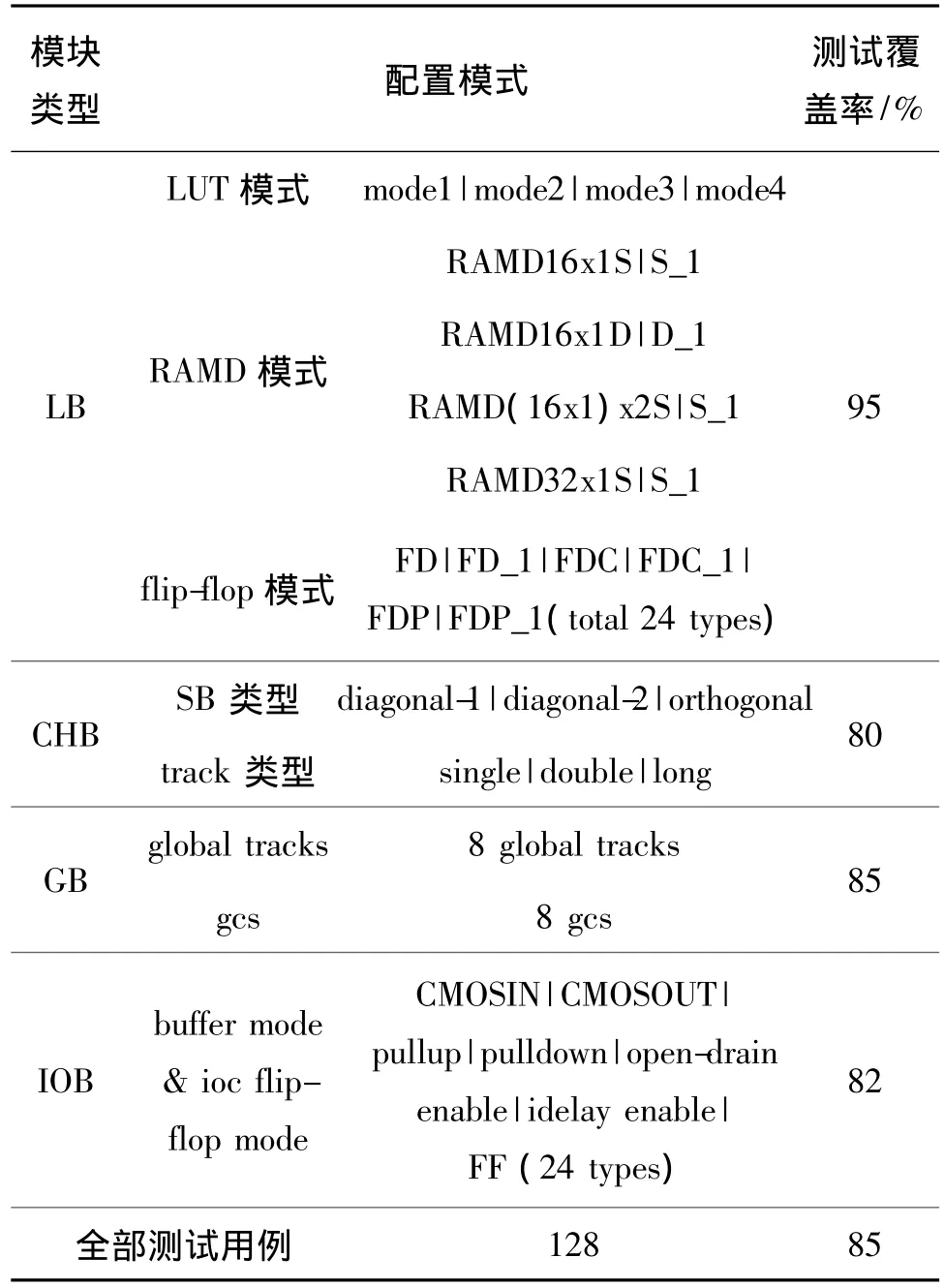

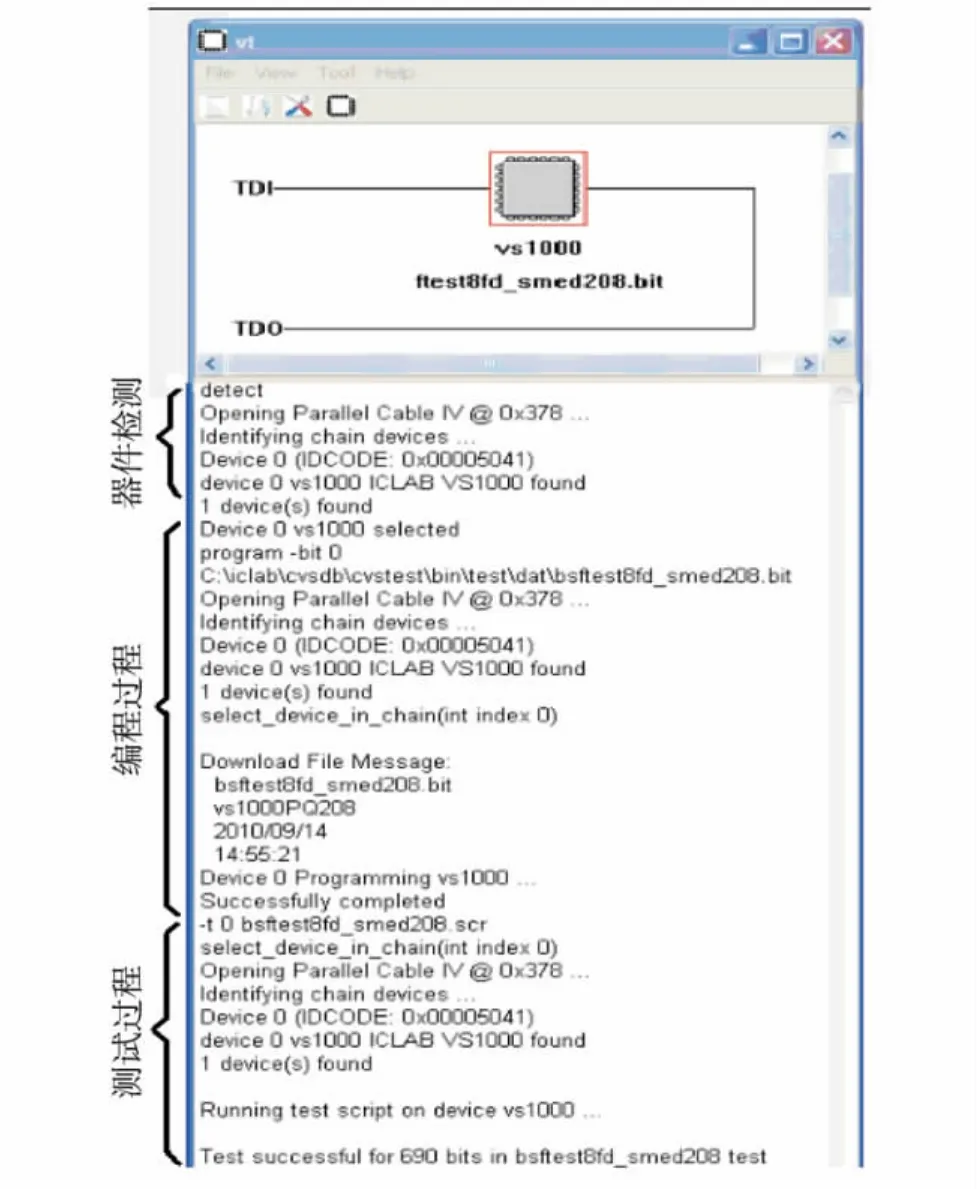

5.4 VVK的芯片板级测试功能

板级测试是指,在功能测试板上,用128个测试向量文件对封装好的每一颗芯片进行完全测试[20].以VS1000芯片板级测试为例,其板级测试环境包括VVK中的下载工具VT、测试板、电压源、示波器以及XC3S400演示板.用每一个测试模型对每颗芯片的测试都包括器件检测、器件编程和功能测试3个过程,全过程如图8.VT会自动对输出结果与期望结果进行比较,并做出报告.重复图8的步骤对每一颗芯片进行完全测试,最终筛选出可用的芯片[20].

表1 VS1000 FPGA芯片的测试实例和测试覆盖率Table1 Functionality test coverage of total testing cases for VS1000 FPGA chip

6 实验结果

为验证VS1000和VVK仿真验证功能的正确性,本研究做了一个演示性的仿真实例pingpong.pingong通过VGA接口在显示器屏幕上显示固定的文字和一个来回跳跃的小球.首先将该测试应用在Xilinx Spartan系列的XCS40上,通过VGA接口在显示器上显示期望图像.然后在本文的仿真演示平台上对pingpong进行仿真.为显示运行结果,本文用C语言编写了一个verilog PLI程序模拟VGA接口,同时利用socket技术将该VGA接口的输出显示在一个用perl程序编写的显示窗口内.图9的仿真演示结果和实际显示结果一致.由此可见,从仿真的角度讲,VS1000硬件和VDS软件已经能正确配合且实现用户定义的功能.

图8 利用VT进行板级测试的整个过程Fig.8 The process of system level test with VT

图9 Pingpong全芯片仿真演示结果Fig.9 GUI graph of full-chip simulation with pingpong

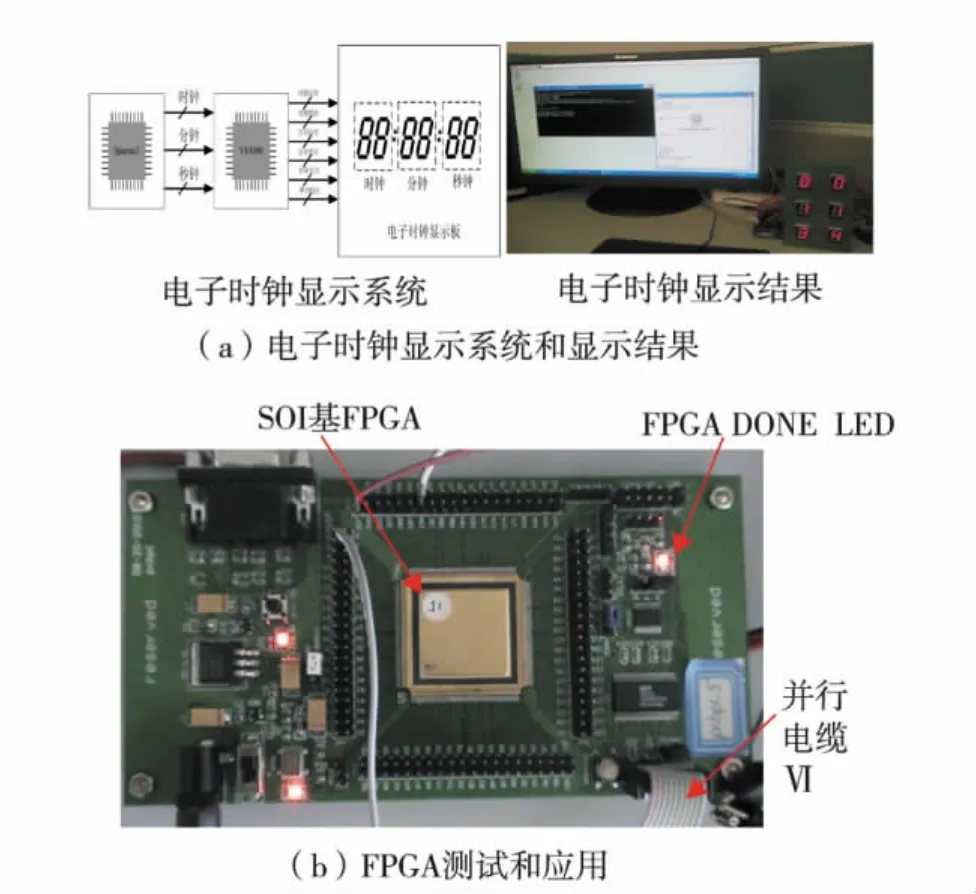

为使VVK对VS1000的测试更加直观,本文做了一个简单的电子时钟显示系统,用VS1000驱动6只LED七段数码管显示电子时钟.电子时钟显示系统和显示结果如图10(a)所示,芯片编程成功后图10(b)测试板上与DONE管脚相连的LED灯会亮.在VS1000的驱动下,电子时钟显示板能够正确地进行时钟显示.由此可见,从应用的角度讲,VS1000硬件和VDS软件已经能正确配合且实现用户定义的功能.

图10 电子时钟显示系统和FPGA应用测试Fig.10 Scheme and effect of a calendar application and FPGA test and application platform

结 语

本文研究开发出一套用于FPGA的多层次集成设计系统VDS,并成功运行于具有自主知识产权的FPGA芯片.VDS的显著特点在于:

①除具有应用FPGA进行电路设计的功能外,VDS还创新性的集成了全自动芯片生成功能,使用户能根据自身需要灵活控制晶片的规模和功能,大大加快了FPGA芯片设计的速度,使快速设计一系列针对不同应用的FPGA芯片成为可能;

②VDS集成了系统级设计以及完备的芯片和应用验证的功能,集成高度超过业界其他FPGA设计工具套件;

③VDS充分利用Python语言的动态特性,通过分布式类编程技术,构造易于扩充且灵活的软件体系,根据VDS中4大组件的个数和组合方式不同,可以快速定制15种不同集成层次的设计系统.

/References:

[1] Zuchowski P S,Reynolds C B,Grupp R J,et al.A hybrid ASIC and FPGA architecture[C]//Proceedings of International Conference on Computer-aided Design.San Jose(USA):IEEE/ACM,2002:187-194.

[2] Sivaswamyy S,Wang G.HARP:hardwired routing pattern FPGAs[C]//Proceedings of the 13th ACM/SIGDA International Symposium on Field Programmable Gate Arrays.Monterey(USA):ACM,2005:21-25.

[3] Betz V,Rose J.Automatic generation of FPGA routing architectures from high-Level descriptions[C]//Proceedings of the Eighth ACM/SIGDA International Symposium on Field Programmable Gate Arrays.Monterey(USA):ACM,2000:175-184.

[4] NI Ming-hao.Research on Automated Design Methodology ofFPGA-the Generation and Verification ofFPGA Behavioral Model[D].Beijing:Chinese Academy of Science,Institute of Semiconductors,2008.(in Chinese)倪明浩.FPGA自动化设计方法的研究—行为模型的产生与验证[D].北京:中国科学院半导体研究所,2008.

[5] YU Hong-min.Research and Realization on an Automated Design Methodology of a High-Performance FPGA Chip[D].Beijing:Chinese Academy of Science,Institute of Semiconductors,2009.(in Chinese).余洪敏.高性能FPGA芯片设计自动化设计方法的研究与实现[D].北京:中国科学院半导体研究所,2009.

[6] Kafafi N,Bozman K,Wilton Steven J E.Architecture and algorithms for synthesizable embedded programmable logic core[C]//Proceedings of the Eleventh ACM/SIGDA International Symposium on Field Programmable Gate Arrays.Monterey(USA):ACM,2003:3-11.

[7] Jonathan R.The GILES research project:automatic layout of FPGAs from an architectural specification[EB/OL].Toronto(Canada):University of Toronto.http://www.eecg.toronto.edu/~ jayar/pubs/ATL/ATL.html.

[8] HAN Xiao-wei,WU Li-hua,ZHAO Yan,et al.A radiation-hardened SOI-based FPGA [J].Journal of Semiconductors,2011,32(7):075012-075016.

[9] Williams S.ICARUS verilog[EB/OL].http://www.icarus.com/eda/verilog.

[10] Berkeley Logic Synthesis and Verification Group.ABC:a system for sequential synthesis and verification[EB/OL].http://www-cad.eecs.berkeley.edu/~ alanmi/abc.

[11] Mishchenko A,Cho S,Chatterjee S,et al.Combinational and sequential mapping with priority cuts[C]//Proceedings of International Conference on Computer-aided Design.San Jose(USA):IEEE/ACM,2007:354-361.

[12] ZHANG Kun,ZHOU Hua-bing,CHEN S L,et al.Technology mapping for FPGA with multi-mode logic cell[J].Journal of Computer-Aided Design & Computer Graphics,2009,21(10):1375-1380.(in Chinese)张 琨,周华兵,陈陵都,等.针对一种多模式逻辑单元结构FPGA的工艺映射[J].计算机辅助设计与图形学学报,2009,21(10):1375-1380.

[13] Marquardt A R.Cluster-based Architecture,Timing-Driven Packing and Timing-Driven Placement for FPGAs[D].Toronto:University of Toronto,1999.

[14] ZHANG Qian-li,CHEN Stanley L,LI Yan,et al.Mapper design for an SOI-based FPGA [C]//Proceedings of 10th IEEE International Conference on Solid-State and Integrated Circuit Technology.Shanghai(China):IEEE Press,2010:821-823.

[15] Vaughn Betz,Jonathan Rose.VPR:a new packing,placement and routing tool for FPGA research[C]//Proceedings of 7th International Workshop on Field-Programmable Logic and Applications.London:Springer,1997:213-222.

[16] CHEN Liang,LI Yan,LI Ming,et al.Implementation and application of navigated place and route for an SRAM-based FPGA [J].Journal of Shenzhen University Science and Engineering,2012,29(3):217-223.(in Chinese)陈 亮,李 艳,李 明,等.基于SRAM的FPGA导航布局布线方法的实现与应用 [J].深圳大学学报理工版,2012,29(3):217-223.

[17] LI Yan,CHEN S L,CHEN Liang,et al.Automated test bitstream generation for an SOI-based FPGA [C]//Proceedings of 10th IEEE International Conference on Solid-State and Integrated CircuitTechnology.Shanghai(China):IEEE Press,2010:1976-1978.

[18] ZHOU Hua-bing,NI Ming-hao,CHEN S L,et al.The design and verification of FPGA CAD toolset[C]//Proceedings of International Symposium on Integrated Circuits.Singapore:IEEE Press,2007:461-464.

[19] WU Li-hua.Design and Verification of Radiation-Hardened SOI-Based FPGA(I)[D].Beijing:Chinese Academy of Science,Institute of Semiconductors,2011.(in Chinese)吴利华.辐射加固SOI工艺FPGA的设计与验证(I)[D].北京:中国科学院半导体研究所,2011.

[20] HAN Xiao-wei.Design and Verification of Radiation-Hardened SOI-Based FPGA(II) [D].Beijing:Chinese Academy of Science,Institute of Semiconductors,2011.(in Chinese)韩小炜.辐射加固SOI工艺FPGA的设计与验证(II)[D].北京:中国科学院半导体研究所,2011.