垂直偏移量任意可调的信号发生器的FPGA实现

陈 琳,潘海鸿,黄光永,李家恒

(广西大学机械工程学院,南宁530004)

1 引 言

直接数字频率合成器(DDS)具有硬件要求低、频率切换速度快、频率分辨率高等优点,已广泛应用于自动测控系统、仪器仪表、通信等领域。一般采用DDS芯片实现波形信号发生器的功能,但其控制方式相对固定,因此不能完全满足用户的需求。而基于高性能FPGA芯片设计出的DDS可根据需求实现复杂的调频、调相和调幅功能,其具有良好的实用性和灵活性。在应用中,需要对多路波形信号的频率、相位、幅度进行高精度调节控制。目前,对信号幅度的调节存在两个方面的不足:一是通过软件方式在波形查找表输出波形数据的末端,简单地加入除法器(或乘法器),该方法不能调节波形信号在垂直方向上所产生的偏移量[1-2];二是通过硬件方式在D/A转换器模拟信号输出末端增加集成模拟乘法器芯片实现波形信号的调零,该方法硬件成本较高且存在一定误差[3-4]。

本文结合直接数字频率合成(DDS)具有频率分辨率高、切换速度快等优点,基于FPGA软件编程方式提出一种可以任意调节输出波形信号的垂直偏移量的信号发生器的设计。采用Altera公司的Cyclone系列FPGA芯片,实现数字化高精度调节多路信号的频率、相位、幅度、偏移量,进而降低硬件电路设计难度和硬件电路的成本。

2 DDS原理

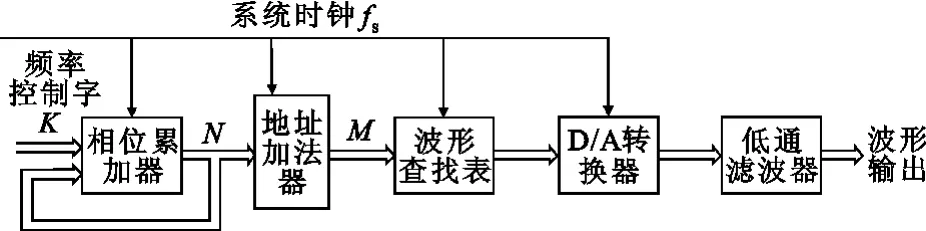

DDS原理如图1所示,主要由相位累加器、地址加法器、波形查找表、D/A转换器和低通滤波器组成。在每个系统时钟脉冲到来,N位相位累加器与频率控制字K进行线性累加,累加结果反馈到相位累加器输入端和输送到地址加法器。在下一个脉冲到来时,相位累加器将输入端累加结果与K相加,如此循环,当相位累加器积满时就产生一次溢出,完成一个周期波形信号输出。地址加法器截取相位累加器高M位二进制码作为寻址值,查找波形查找表的波形数据。波形数据在经过D/A转换器和低通滤波器转换成模拟波形输出。相位累加器频率控制字K大小不同,相位累加器积满时溢出频率不同,也即输出波形频率不同。通过改变频率控制字K大小来改变输出波形频率。输出波形频率 fout与系统时钟频率fs、频率控制字K、相位累加器位数N关系为

当K为1时,输出波形信号频率分辨率为

最大输出频率由Nyquist采样定理决定:fmax=fs/2。

图1 DDS原理图Fig.1 The schematic diagram of DDS

3 波形信号垂直偏移量任意可调的信号发生器设计

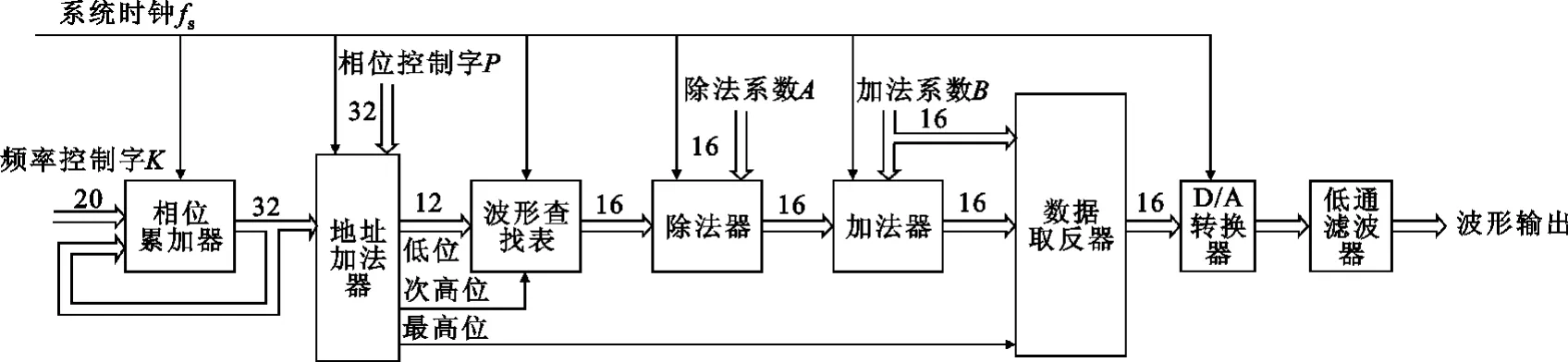

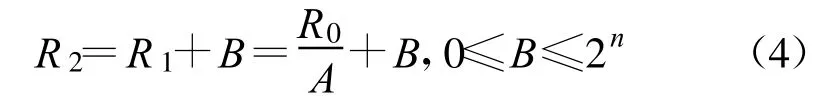

根据DDS原理,在FPGA中实现全数字化调节波形信号的频率、相位、幅度、任意垂直偏移量的功能。通常信号发生器产生正弦波、锯齿波、方波、三角波以及自定义任意波形。波形生成方法有查表法、查表并一阶(线性)插补法、泰勒级数近似值法等[5-6]。考虑满足实验要求情况下,尽量选择速度快、精度较高、波形存储空间需求低的方法。经对比分析,这里波形生成方法选择查表法。整个信号发生器系统原理框图如图2所示,在系统时钟同步下,32位相位累加器不断对频率控制字K进行线性累加,当相位累加器积满时就产生一次溢出,从而完成一个周期波形信号输出。32位相位累加器对频率控制字K进行线性累加,截取相位累加器高12位二进制码输送到地址累加器,地址累加器查找波形查找表数据,经过除法器、加法器、数据取反器、16位D/A转换器、低通滤波器后,输出波形信号。

图2 垂直偏移量任意可调信号发生器系统原理图Fig.2 The principle of arbitrarily adjusted of vertical offset for signal generator system

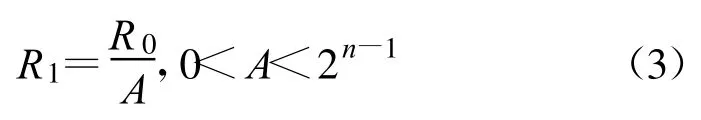

现以正弦波为例(其它波形的产生采用与正弦波类似的方法),结合正弦波信号对称特点,波形查找表存储1/4周期波形。地址加法器最高位和次高位分别控制数据取反器和查找波形查找表方向[5-6]。地址加法器的次高位控制查找波形查找表方向:地址加法器次高位为0,地址加法器输出正向地址值查找波形查找表中波形数据,输出0~π/2信号;地址加法器次高位为1,地址加法器输出反向地址值查找波形查找表中波形数据,输出π/2~π信号。地址加法器最高位控制数据取反器工作:最高位为0,数据取反器对输入的波形信号不进行任何操作;只有在地址加法器最高位为1,数据取反器对输入的波形信号以当前加法器系数为水平中心线的取反操作,即0~π波形数据进行取反操作得到π~2π波形数据。除法器用波形查找表输入的波形信号R0除以输入的除法系数 A,结果 R1输送到加法器,通过改变除法系数A实现改变输出波形的幅度,如公式(3):

在除法器与数据取反器之间的加法器将除法器输入波形信号R1与输入加法系数B相加得到结果R2:

一般情况下,加法器的加法系数B是2n-1,波形信号进行幅度调节的精度取决于D/A转换器、精密基准稳压源的精度。波形信号经D/A转换器、低通滤波器后以某一电压值为水平线输出。此外,因硬件电路原因引起输出波形信号存在偏移,也可以通过调节加法器加法系数B消除波形信号在垂直方向上偏移量。

数据取反器主要完成对由加法器输入的波形信号进行取反操作,该操作由地址累加器的最高位控制。在地址累加器的最高位为1时,数据取反器对输入的波形信号进行取反操作,波形信号后半周期结果为R3:

而最高位为0时,数据取反器对输入的波形信号不进行任何操作。数据取反器将处理后的波形信号输送到D/A转换器、低通滤波器,最后完成整个波形的输出。

以调节输出以0 V为水平中心线的正弦电压波形为例。选取16位AD转换器,波形输出电压V=(CODE/65 536)×Vin,其中 CODE是波形数据,数据是0~65 535之间的整数。假定0和65 535对应AD转换为模拟电压值为-10V和+10V。模拟电压值0V对应波形数据为32 767。根据正弦波信号特点波形查找表存储1/4周期正弦波数据:从0到32 767。

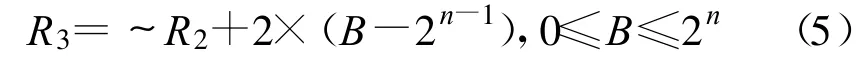

幅度调节:当除法系数A为2,正弦波信号幅度缩小为满幅输出的1/2;当除法系数A为4,正弦波信号幅度缩小为满幅输出的1/4,实现过程如图3所示。

图3 正弦波幅度调节Fig.3 The adjustment of amplitude of sinusoidal waveform

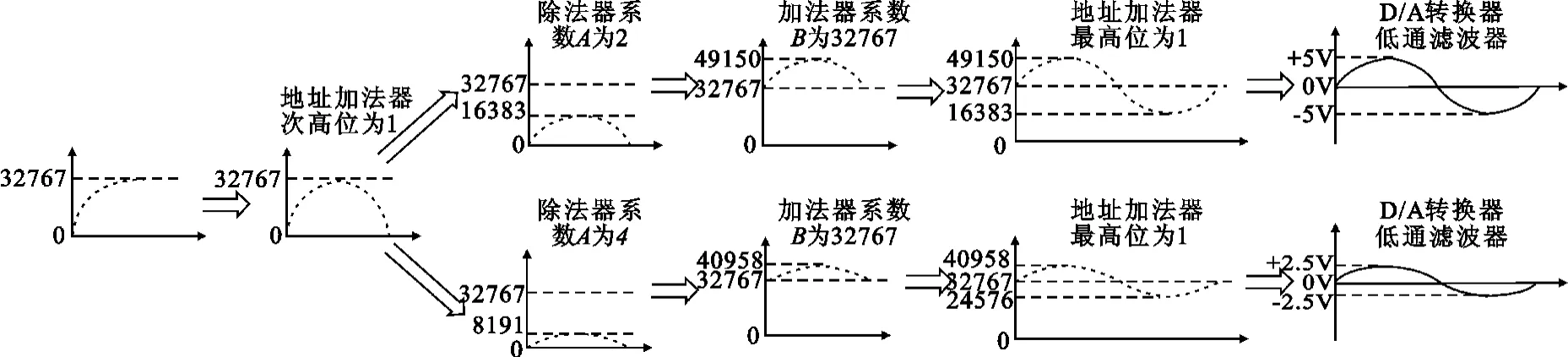

垂直偏移量调节:信号在垂直方向可以任意调节。当输出波形信号要求在垂直方向上有偏移量时,可通过调整加法系数B来实现。此外,因硬件电路原因使得最终输出波形信号略微偏离0 V线,可以通过调节加法器加法系数B消除波形信号在垂直方向上偏移量。16位加法系数B调节电压范围-10~+10 V,偏移量分辨率为:20V/216=0.000 3 V,即加法器加法系数B每变化1引起输出模拟电压变化量为0.3 mV。

以调节幅度为满幅输出的1/2的正弦波,且全为正向电压为例。此时调整除法系数A为2,加法系数B为49 151。由公式(3)~(5)可得正弦波数据范围为32 767~65 535,实现过程如图4所示。

图4 正弦波偏移量调节Fig.4 The offset adjustment of sinusoidal waveform

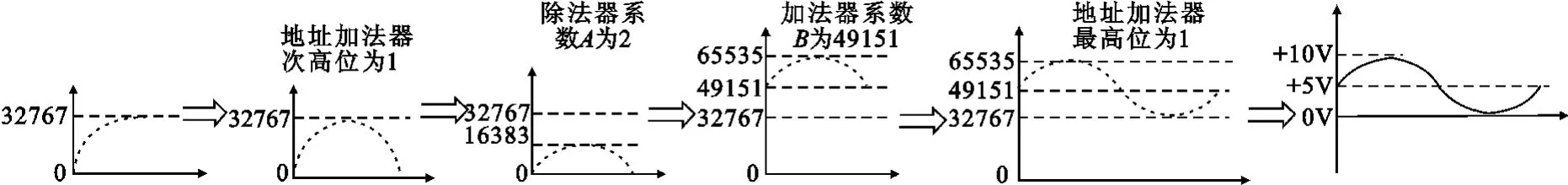

4 实验平台与验证

在Quartus II 7.2环境下采用Verilog-HDL语言设计多路波形信号发生器,并在FPGA平台上实现(图5),该平台主要由DAC板和FPGA板组成。FPGA板采用Altera公司低成本Cyclone系列EP1C12Q240C8芯片,主要通过编程实现可调零、调幅、调频、不同相位偏移量的波形信号生成。DAC板主要由数模转换电路及低通滤波电路组成。由FPGA板生成数字波形信号,输入DAC板,经数模转换电路,将数字波形信号转变成模拟信号,再通过低通滤波平滑,最后通过示波器可以测量所生成的波形信号。通过示波器上的两路波形信号,验证所提出的设计。

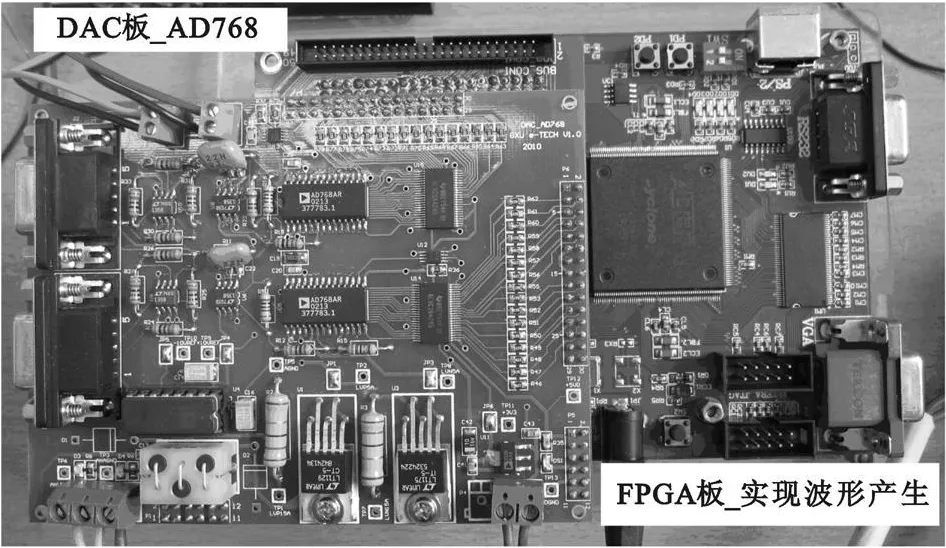

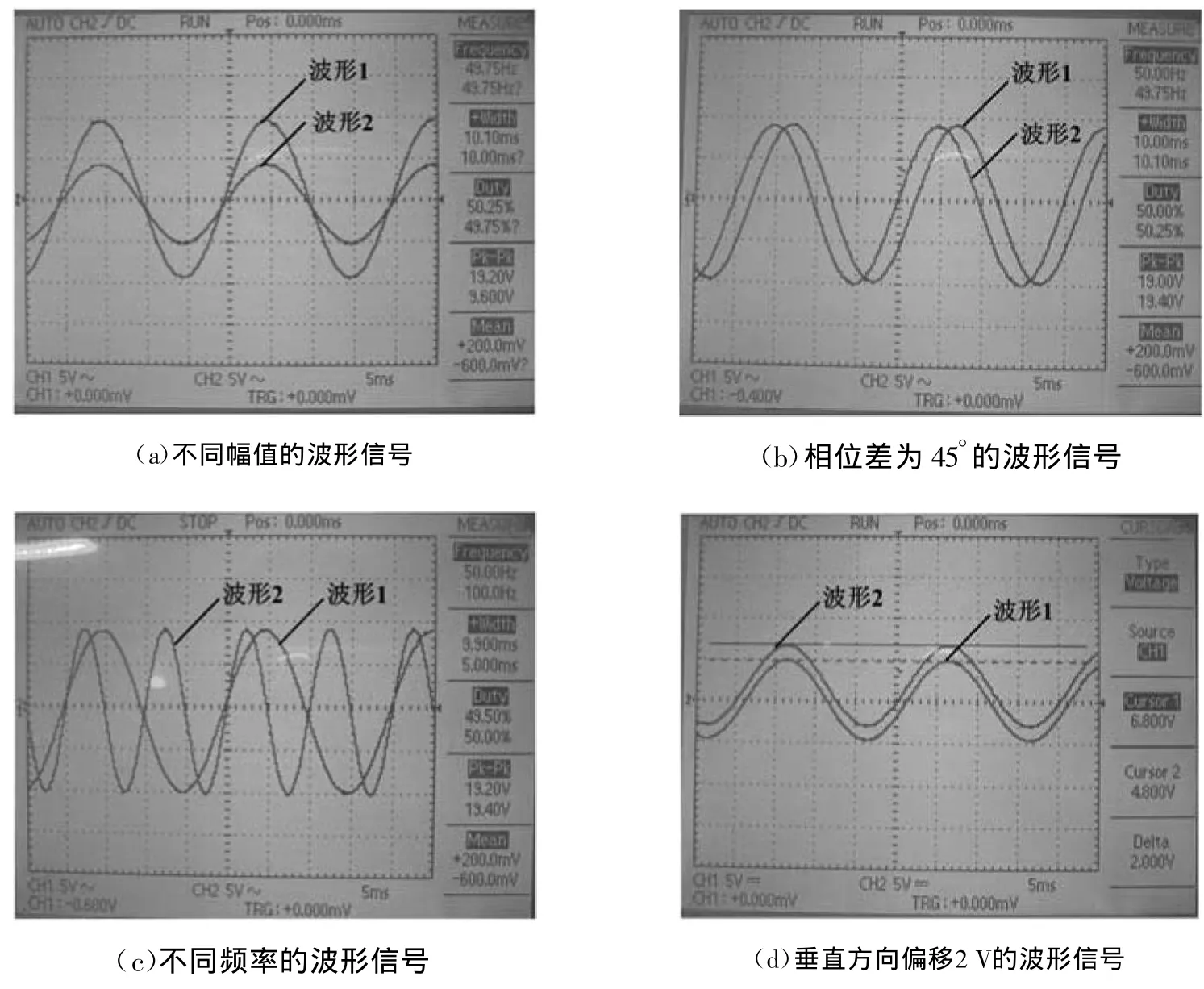

实验结果如图6所示,以波形1作为参考,其频率50Hz,幅值±10 V,通过改变波形2的除法系数A,调节输出波形幅度,实现输出幅度为±5V的波形(图6(a));通过改变波形2的相位控制字P,实现输出波形相位差为45°(图6(b));通过改变波形2的频率控制字 K,实现输出频率100 Hz的波形(图6(c));通过改变波形2的加法系数B,调节其垂直方向偏移量,实现波形2比波形1在垂直方向上的偏移量为2 V的输出波形(图6(d))。

图5 信号发生器实验平台Fig.5 The experiment platform of signal generator

图6 实验结果图Fig.6 The experiment results

5 结 论

本文基于DDS原理采用Verilog HDL语言,在FPGA芯片上通过软件编程方法设计并实现了频率控制、相位控制、幅度控制、垂直偏移量任意可调的信号发生器。通过搭建实验平台验证了采用软件编程方法的波形信号发生器可根据实际需要实现任意的频率调节、相位调节、幅度调节;特别是该波形信号发生器不需要外加硬件电路,就可以实现对输出波形垂直偏移量的调节,且调节信号灵活,具有输出波形精度高、可控性好、成本低的优点。依据DDS原理在FPGA芯片上,根据实际需要通过编程设计并实现两路及两路以上的多路波形信号发生器,可以广泛应用于自动测控系统、仪器仪表、通信等领域。

[1]李勇,艾竹君,刘巧云,等.基于FPGA的 DDS设计方法[J].低温与超导,2007,35(6):539-542.LI Yong,AI Zhu-jun,LIU Qiao-yun,et al.A Design for DDS Dased on FPGA[J].Cryogenics and Superconductivity,2007,35(6):539-542.(in Chinese)

[2]电子科技大学.一种双通道可调相调幅的同步DDS装置:中国,101339446A[P].2009-01-07.University of Electronic Science and Technology of China.A T wo ChannelsT unable Phase andAmplitude of Synchronous DDS Device:China,101339446A[P].2009-01-07.(in Chinese)

[3]汪勐,汪宁,宋晓东.使用较少FPGA资源实现DDS的方法[J].微电子学与计算机,2006,23(8):181-186.WANG Meng,W ANG Ning,SONG Xiao-dong.The Implementation of DDS with FPGA by Less Resources Used[J].Microelectronics&Computer,2006,23(8):181-186.(in Chinese)

[4]叶佩青,杨更更,杨开明,等.多通道相位差可调正弦波信号发生器的设计[J].仪表技术与传感器,2004(1):10-12.YE Pei-qing,YANG Geng-geng,YANG Kai-ming,et al.Design of Multi-channel Sine Waveforms Generator with Tunable Phase Difference[J].Instrument Technique andSensor,2004(1):10-12.(in Chinese)

[5]蓝天,张金林.直接数字频率合成器DDS的优化设计[J].电子技术应用,2007(5):42-44.LAN Tian,ZHANG Jin-lin.Optimization Design of Direct Digital Frequency Synthesis[J].Application of Electronic Technique,2007(5):42-44.(in Chinese)

[6]李康顺,吕小巧,张文生,等.基于改进 DDS技术的FPGA数字调制器研究与实现[J].压电与声光,2009,31(6):852-855.LI Kang-shun,LV Xiao-qiao,ZHANG Wen-sheng,et al.Research and Implement of FPGA Digital Modulator Based on Improved DDS Technology[J].Piezoelectrics&Acoustooptics,2009,31(6):852-855.(in Chinese)