基于System Generator的数字下变频设计

陈 蕾,姚远程

(西南科技大学 信息工程学院,四川 绵阳 621010)

近年来,FPGA以其高度的并行计算能力成为高性能数字信号处理系统的核心器件。在通信、雷达、数据获取以及视频处理等领域得到了广泛的应用。在数字信号领域中,研究人员往往使用Matlab语言进行系统级建模,但不一定对FPGA设计中运用到的硬件描述语言VHDL或者Verilog熟悉,2种语言的不统一,不仅降低了开发效率,也限制了FPGA在数字信号领域中的应用。

Xilinx公司推出的DSP设计开发工具System Generator主要为一些不熟悉VHDL等硬件开发语言的设计者开发。首先,在Simulink的可视化环境内对算法以及系统进行建模,而后调用System Generator自动将Simulink模型转换成硬件可执行模型,直接生成FPGA代码,ISE可以对整个工程文件进行综合、仿真,完成芯片配置后下载到硬件环境中进行测试,整个过程都在可视化的环境中进行。本文介绍了基于System Generator的数字系统开发过程的一般流程,并以数字下变频系统为例,证明了该方法在数字系统中的明显优势。

1 基于System Generator的系统级设计方法

在传统的设计方法中,往往采用Matlab、C、C++等语言来描述各功能模块,从而实现系统的建模。但是在寄存器传输级则采用硬件描述语言VHDL等来进行描述。在传统设计方法中,原始的Matlab等语言描述必须经手工转换为VHDL语言,这就要求设计人员必须同时掌握这两类语言,并且这个转换过程会花费大量的时间和精力,可能还会产生一些错误,降低整个工作过程的效率。同时,当使用Matlab等语言描述的模块转换成硬件描述的模块之后,设计者花费大量心血和时间建立起来的原模型将再没有什么用处。再次,完成整个的设计需要多个测试平台。因为针对Matlab等语言描述的模块测试平台无法直接转换为针对硬件描述语言的模块所需要的测试平台。

为了克服传统的系统级设计方法所存在的弊端,提出了基于System Generator的系统级设计方法。System Generator和matlab的simulink是无缝连接的,可以通过调用simulink中的 system generator blockset,在simulink的可视化环境内对算法以及系统进行建模,同时对各功能模块进行划分。这些模块对应着IP核库组件,设计者只需要按照要求对这些模块进行配置即可完成功能模块的设计。

当在Matlab算法中完成系统级的建模之后,通过调用System Generator将simulink模型转换成硬件可执行模型。这样,在同一个环境中,就可以完成算法的设计到硬件的实现,整个设计的软硬件可以协同设计和仿真,弥补了传统设计中两个层次转换的问题,也解决了不熟悉硬件描述语言的设计者面临的问题,提高了开发效率。具体的开发流程如图1所示。

图1 典型的基于System Generator的FPGA开发流程图Fig.1 Typical FPGA development flow chart based on System Generator

具体步骤为:首先,根据系统的需求进行分析,在Matlab环境下进行建模,并对各功能模块进行配置,完成系统算法的仿真验证;其次,调用System Generator自动将系统转换为ISE工程,生成寄存器传输级和IP核代码,同时生成Testbench测试文件,可以在Modelsim中进行仿真验证。最后,在ISE环境中,完成FPGA的综合、布局布线等,产生位流文件,方便下载到FPGA中进行验证。

2 数字下变频基本原理

数字下变频系统主要由模数转换器 (ADC)、NCO模块、多级抽取滤波器以及整形滤波器组成,如图2所示。其中模数转换器主要完成对模拟中频信号的采样,得到数字化中频信号。再通过混频、多级滤波抽取以及整形滤波将感兴趣的信号搬移到基带,得到正交的两路信号,不仅降低了速率,同时也包含了原始中频信号中的有效信号,由此将低速数据送往后续的数字信号处理器进行基带信号的处理。

图2 数字下变频框图Fig.2 Digital down-conversion block diagram

3 System Generator数字下变频模块设计

3.1NCO模块

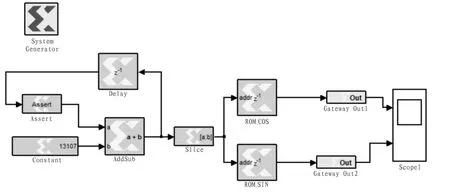

NCO 模块的作用是产生两个正交、频率可变的正余弦波形,通过和采样信号进行混频处理,得到两路正交信号,它的性能优劣很大程度上影响数字中频的性能,并对后续的抽取滤波等运算有直接的影响,如图3所示。

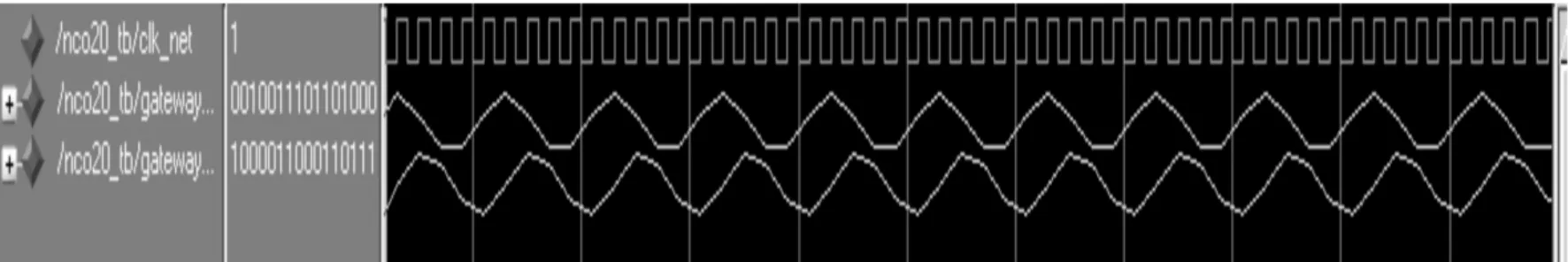

采用直接数字合成器(DDS)来产生正弦波。其中最重要的步骤是确定步长,它是控制NCO输出频率的关键因素。假定系统时钟为50 MHz,其中参数控制模块配置累加器数据位宽为16位,期望输出频率为10 MHz,由此得出步长为13 107.2。经过ISE综合后,在Modelsim中运行仿真得到仿真结果如图4所示。

3.2 多级抽取滤波器的设计

图3 基于System Generator的NCO设计Fig.3 Design of NCO based on System Generator

图4 NCO在Modelsim中的仿真结果Fig.4 Results of NCO in the Modelsim

由于混频后产生的数据率比较高,后级FIR无法对这个速度进行处理,由此采用多级抽取滤波器级联结构。通常第一级由较高的比率进行抽取,后面的采用低速率抽取并完成整形。因为CIC滤波器只有加减运算,没有乘法运算,实现起来简单,在硬件实现的时候能够达到很高的处理速率,不管是在实现性能还是资源节省方面都优于FIR滤波,由此一般作为第一级抽取或者是抽取比较大的系统中。HB滤波器由于冲击响应具有偶对称性质,其偶数点(除0点以外)均为零,滤波时运算量减少一半,计算效率高,带内平坦度好,因此被作为第二级低通滤波和抽取。最后一级使用FIR滤波,对整个信道进行整形滤波。

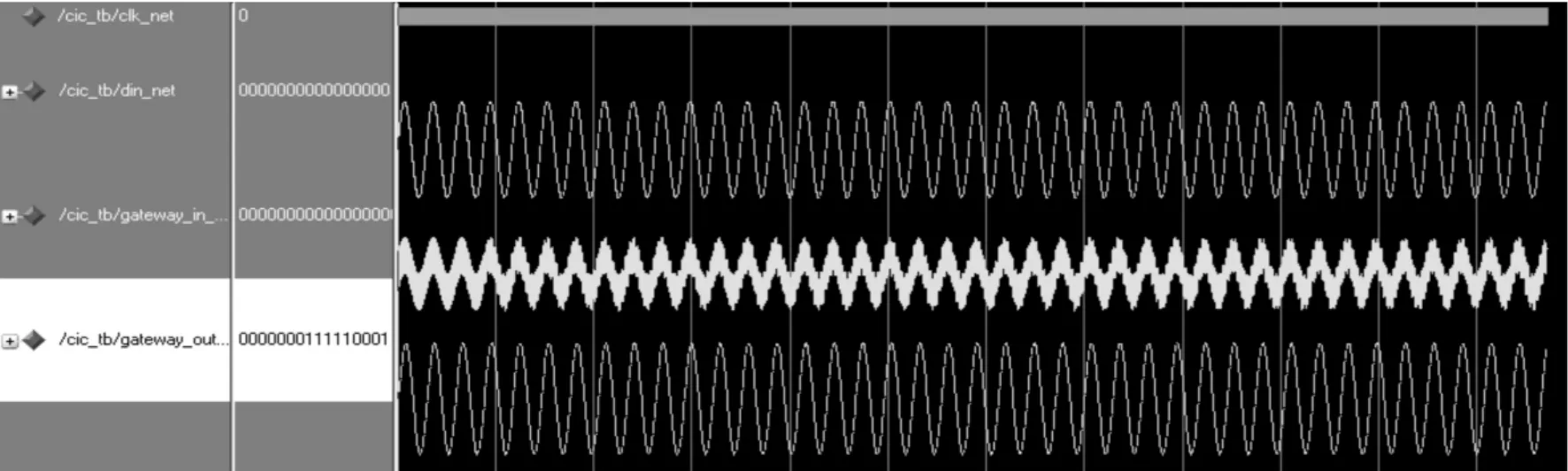

3.2.1 CIC模块

CIC滤波是一种结构简单,具有全加法递归结构的线性相位有限冲击响应滤波器,如图5所示。它只需要进行加减运算,不需要通过乘法运算,非常适合硬件的高效实现,通常用于第一级的抽取或者大的抽取因子系统。由于单级CIC滤波的过渡带和阻带衰减都不是很好,主瓣与第一旁瓣峰值之差约为13.46 dB,往往不能满足系统的要求。所以一般采用CIC级联的方式来降低旁瓣幅度,增大阻带衰减,系统中一般采用5级级联方式,阻带衰减达到13.46×5=67.3 dB,滤波器性能将大幅度提高。

输入频率为33kHz和2MHz的两个单频信号,其中33kHz的信号代表有用信号,2 MHz的信号代表带外干扰信号,采样率为80 MHz。在FPGA实现的时候,CIC内部处理的数据位数将增加,因为随着CIC级数的增加,处理增益将增大。为了确保每一级的运算精度,防止溢出错误和运算精度的下降,需要根据输出位数来确定每一级的输出位数。在本例中,输出数据在无舍尾的情况下应该为25+25=50位,这将是非常耗资源的,所以在输出的时候需要对数据进行舍位截取。

图5 基于System Generator的CIC设计Fig.5 Design of CIC based on System Generator

图6 CIC滤波在Modelsim中的仿真结果Fig.6 Results of CIC in the Modelsim

在仿真结果图中,由上至下分别为原信号、混合信号以及滤波后信号,CIC滤波有效的抑制了混叠的频率成分,输出了较干净的33 kHz频率成分,同时对2 MHz的噪声信号经过32倍抽取产生的0.625 MHz的噪声信号也进行了有效地抑制,衰减幅度在60 dB以上。

3.2.2 HB模块

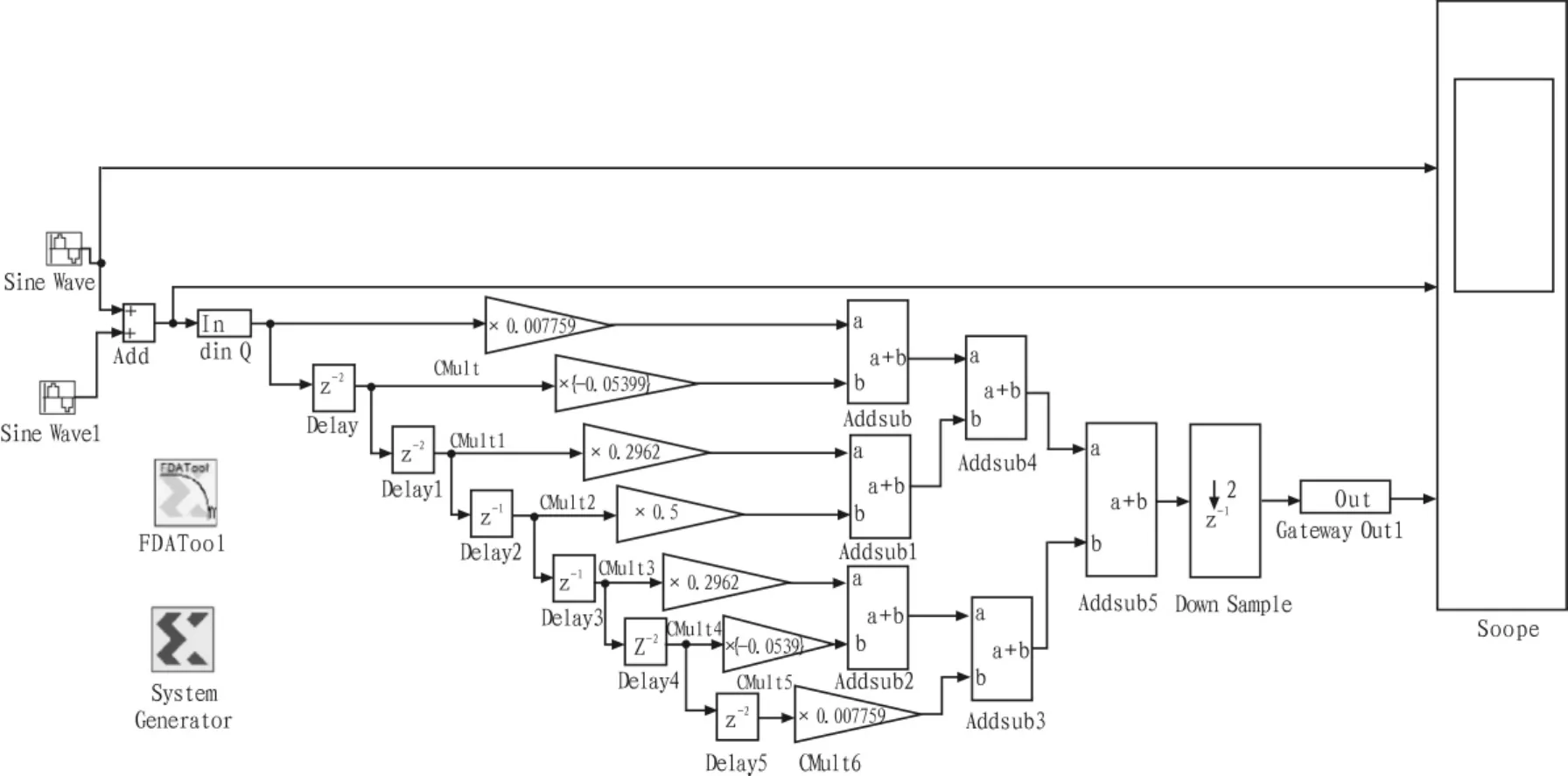

半带滤波器是指阻带宽度和通带宽度相等,并且通带波纹和阻带波纹也相等的一种特殊的FIR滤波器,特别适用于实现2的N次方的抽取和滤波,滤波器的参数是中心对称的,并且有一半为零,卷积计算时的乘法运算次数减少了一半,极大地提高了计算效率,实时性非常强。在对HB滤波器进行设计的时候,为了避免半带滤波器2倍抽取之后通带信号的频谱发生混叠,需要对半带滤波器的通带截止频率和阻带起始频率进行设计。由于它们关于pi/2对称,则只需对通带截止频率进行设计,要求通带截止频率要大于等于有用信号带宽的带宽并且小于pi/2,HB模块如图7所示。

输入2个单频信号频率分别为1.6 MHz和28 MHz,采样率为80 MHz,其中1.6 MHz代表有用信号,28 MHz代表带外干扰信号。取通带宽度为6 MHz,通带波纹为0.001。图8的仿真结果充分显示了在经过半带滤波器2倍抽取之后,有效的滤除了28 MHz的噪声信号,得到比较纯净的原信号波形,滤波效果良好。

图7 基于System Generator的HB设计Fig.7 Design of HB based on System Generator

图8 HB滤波在Modelsim中的仿真结果Fig.8 Results of HB in the Modelsim

3.2.3 FIR滤波器

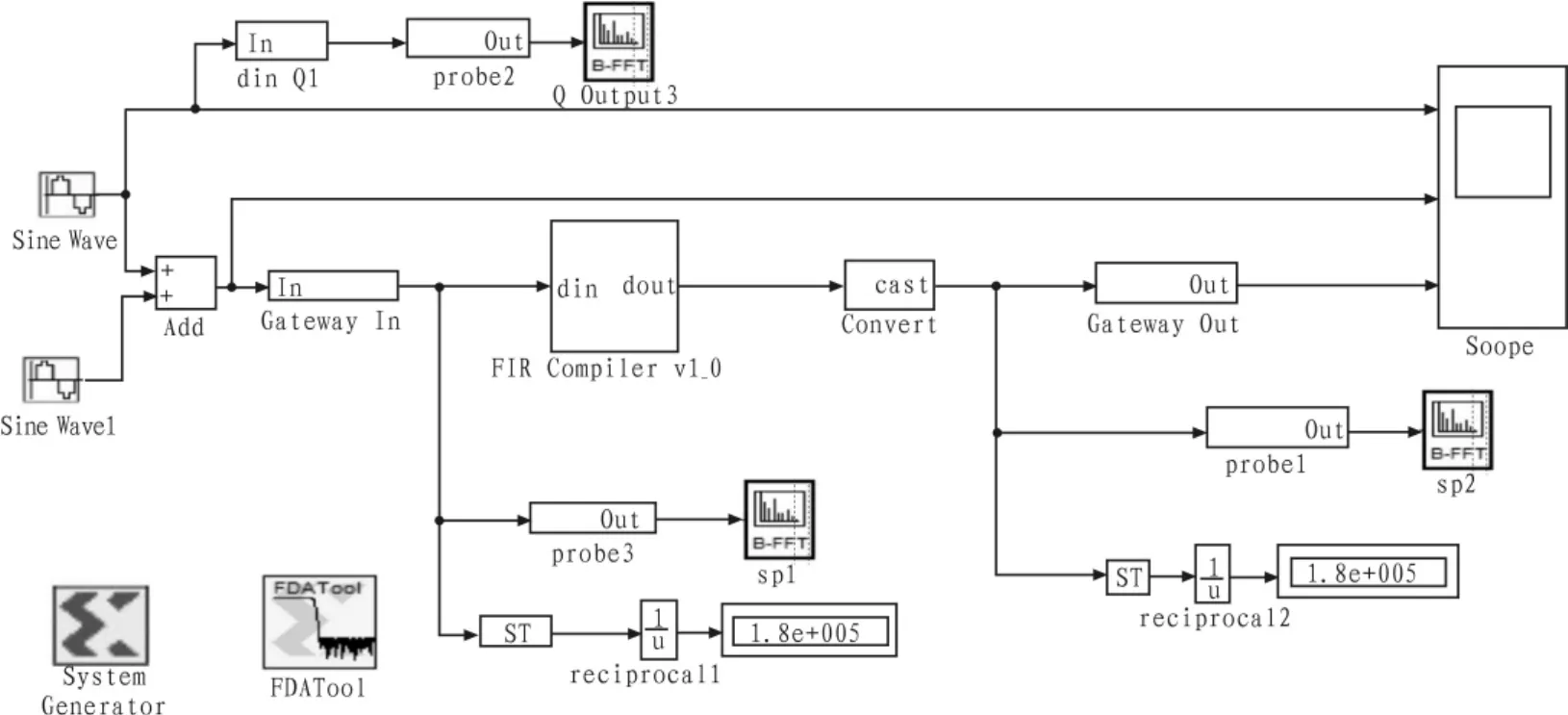

在多速率处理的过程中,一般将FIR滤波器放在CIC滤波和HB滤波器的后面,因为经过前两级滤波之后,采样速率一般已经很低,不需要FIR在进行抽取,只需要对整个信道进行整形滤波。对FIR滤波器的设计,同样可以采取Matlab中的fdatool工具进行,由于一般滤波器阶数较高,故采用FIR Compiler模块来设计,实现起来比较简单,该模块能实现基于乘累加的滤波运算。输入的仿真信号为10 kHz和40 kHz,采样率为160 kHz。通过仿真结果,能清楚看到FIR滤波很好的完成了滤除噪声信号的功能。

图9 基于System Generator的FIR设计Fig.9 Design of FIR based on System Generator

图10 FIR滤波在Modelsim中的仿真结果Fig.10 Results of FIR in the Modelsim

4 结束语

在软件无线电中,数字下变频是整个系统中最关键的信号处理模块,也是整个软件无线电收发机中最耗资源的模块,它的性能决定了整个软件无线电收发机的性能。文中首先分析了传统的系统级设计方法所存在的弊端,提出了基于System Generator的系统级设计方法,并给出了设计的一般流程和步骤,对多速率处理中的NCO模块、CIC、HB以及FIR模块分别进行了验证和仿真,均符合设计的要求,并在Modelsim中得到了准确的验证。这种设计方法避免了DSP设计者在不熟悉硬件描述语言状况下的复杂编程,提高了设计的效率,缩短了设计周期。

[1]张勇,高梅国.基于SysGen的FPGA设计开发[J].计算机工程与应用,2010(9S):134-137.

ZHANG Yong,GAO Mei-guo.Research of FPGA design technology based on SysGen[J].Computer Engineering and Applications,2010(9S):134-137.

[2]牛斌凯,雍少为.基于System Generator开发数字信号处理系统[J].舰船电子工程,2010:129-132.

NIU Bin-kai,YONG Shao-wei.Research on design method fordigitalsignalprocessing system based on System Generator[J].Ship Electronic Engineering,2010:129-132.

[3]纪志成,高春能.FPGA数字信号处理设计教程——System Generator入门与提高 [M].西安:西安电子科技大学出版社,2008.

[4]刘强.基于SystemC的系统级芯片设计方法研究[J].现代电子技术,2005(9):33-35.

LIU Qiang.The study on design method of SystemC[J].Modern Electronics Technique,2005(9):33-35.

[5]Xilinx.System Generator Manual[S].San Jose:Xilinx,2012.

[6]屈有萍.基于FPGA的数字下变频研究实现[D].西安:西安电子科技大学,2007.

[7]Murthy S N,Alvis W,Shirodkar R, et al.Methodology for implementation of unmanned vehicle control on FPGA using system generator[C]//IEEE,1957.

[8]田耘,徐文波,张延伟.无线通信的FPGA设计[M].北京:电子工业出版社,2008.