基于ADF4111的锁相环频率合成器设计

张珂勇

(电子科技大学 四川 成都 610054)

锁相环频率合成器作为一种相位负反馈控制技术,能提供高稳定度的频率输出,具有以下优点:锁定时无剩余频差;门限性能优良;宽带调制跟踪性能好;窄带载波跟踪性能强;易于集成[1]。广泛应用于微处理器芯中的时钟发生器、硬盘驱动电路模块、时钟恢复电路等以及便携式消费电子产品中。随着电子技术的发展,电子设备对对频率合成器的要求也越来越高。文中旨在设计出满足移动通信中GSM下行频率范围930~960 MHz的频率输出,同时提出一种减少开发风险、加快锁相环产品开发周期的设计方法。

1 锁相环频率合成器的原理

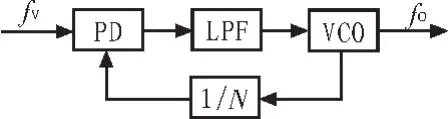

锁相技术是通过比较输入信号和压控振荡器VCO的输出信号相位,取出与二者的相位差成正比的电压作为控制电压来控制VCO的输出,以达到使二者信号频率(相位)相等的目的。总之,锁相环电路是用于产生与输入信号相位同步的新的信号电路。其电路基本组成如图1所示[2-4]。

图1 PLL频率合成框图Fig.1 PLL frequency synthesis principle diagram

由基本原理得到,其输出频率f0=N*fv(fv为参考频率)。令fv=200 kHz,f0=930~960 MHz,故分频数N为 4 650~4 800。

1.1 利用ADIsimPLL快速选型与仿真

ADIsimPLL是ADI发布的锁相环产品辅助设计及仿真工具,拥有强大的锁相环芯片、VCO库,能快速进行产品选型与仿真,并能进行包括环路滤波器在内的外围电路设计,避免复杂的环路滤波器计算,提高准确度与效率[5-7]。运用ADIsimPLL软件可以选择具有高集成度、频率范围为0 Hz~1.4 GHz的ADF4111作为锁相环芯片,选用三阶无源超前滞后滤波器为环路滤波器。软件会根据需求自动筛选出合适的VCO,在此选择ZComm公司的V580ME02。其输出频率范围为900~960 MHz,压控灵敏度Kv为37 MHz/V。确定环路带宽为10 kHz,相位裕度45°。自动生成的锁相环频率合成器原理图如图2所示,环路滤波器参数如表1所示。

1.2 利用ADS进一步仿真优化

ADS全称为 Advanced Design System,是美国安捷伦(Agilent)公司所生产拥有的电子设计自动化软件。ADS功能十分强大,包含时域电路仿真 (SPICE-like Simulation)、频域电路仿真 (Harmonic Balance、Linear Analysis)、 三维电磁仿真、通信系统仿真(Communication System Simulation)和数字信号处理仿真设计(DSP),是微波、射频电路仿真分析的首选工具[8]。

图2 ADIsimPLL仿真图Fig.2 ADIsimPLL schematic diagram

表1 ADIsimPLL得到的环路滤波器参数Tab.1 Parameters of loop filter from ADIsimPLL

表2 ADS优化得到的环路滤波器参数Tab.2 Parameters of loop filter optimized by ADS

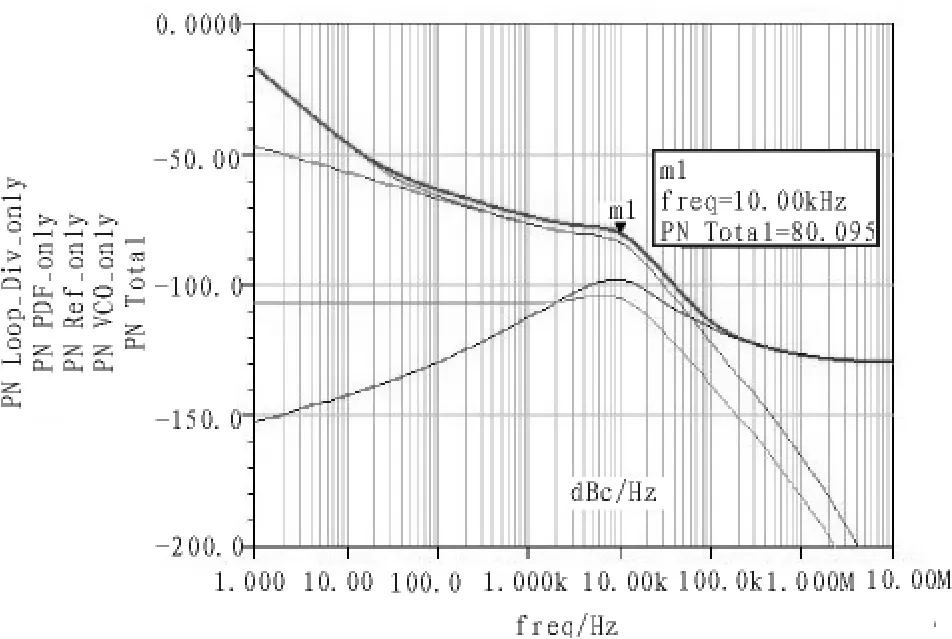

以上仿真在10 kHz处的相位裕度为45°,满足了条件,但是并没有得到最大相位裕度,可能造成系统的不稳定,因此仍需进一步利用ADS进行优化[9-10]。在ADS中建立锁相环的瞬态响应仿真,设置变量 Kv=37 MHz,Id=0.004 5 A,No=4750,环路带宽为10 kHz,添加相关优化变量,使其在10 kHz处的相位裕度达到最大。优化后的环路滤波器参数如表2所示,与优化前有较大变化。开、闭环增益(相位)曲线响应如图3所示,可见其相位裕度提高到47.2°。锁定时间如图4所示,其锁定时间为377.5 μs。从各部分相位噪声关系图6可以看出,总的相位噪声优于-80 dBc/Hz@10 kHz。可见利用ADS进一步仿真优化使电路的稳定性有了较大提升。

图3 开、闭环增益曲线Fig.3 Open and closed loop amplitude responses

图4 开、闭环相位曲线Fig.4 Open and closed loop phase responses

图5 输出频率的锁定时间Fig.5 VCO frequency versus time

2 结束语

文中在利用ADS设计PLL频合器前使用ADIsimPLL进行快速选型与环路滤波器的参数确定,避免繁琐的选型与复杂的推导计算,进而快速设计出输出频率为930~960 MHz,性能指标优良的锁相环频率合成器。该方案提高了设计精准度,有力地缩短了设计周期,为快速设计锁相环频率合成器提供一种行之有效的办法。

图6 各部分相位噪声关系Fig.6 Contributions to VCO phase noise

[1]陈邦媛.射频通信电路[M].2版.北京:科学出版社,2006.

[2]远坂俊昭.锁相环(PLL)电路设计与应用[M].北京:科学出版社,2006.

[3]邓正森.基于锁相环技术频率合成器研究与设计 [D].成都:电子科技大学,2008.

[4]Reinhold ludwig Pavel Bretchko.射频电路设计[M].北京:电子工业出版社,2002.

[5]杨宜生.基于ADF4106的本振源的设计与实现 [J].科技信息,2012(14):341.

YANG Yi-sheng.The design and tealization of Local oscillator based on ADS[J].Science and Technology Information,2012(14):341.

[6]丁新强.基于ADF4106的锁相环设计 [J].电子测试,2011(6):16-18.

DING Xin-qiang.Design of phase locked loop which is based on ADF4106[J].Electronic Test,2011(6):16-18.

[7]谢力慧.300 MHz集成锁相环频率合成器的设计[D].成都:电子科技大学,2008.

[8]项顺祥,边新辉.基于ADS的锁相环瞬态响应仿真[J].舰船电子工程,2008(10):144-146.

XIANG Shun-xiang,BIAN Xin-hui.Transient response of lock loop based on ADS software[J].Ship Electronic Engineering,2008(10):144-146.

[9]刘丽平.锁相环中环路滤波器的设计与ADS仿真[J].信息通信,2010(4):28-29.

LIU Li-ping.The design and ADS simulation of PLL loop filter[J].Information and Communication,2010(4):28-29.

[10]徐兴福.ADS2008射频电路设计与仿真实例[M].北京:电子工业出版社,2009.