基于DVB-S2标准的LDPC码编译码器设计研究

陈豪威,王秀敏

(中国计量学院信息工程学院,浙江 杭州 310018)

1994年DVB-S被采纳作为欧洲数字卫星广播标准,随着技术的发展,又提出了第二代标准DVB-S2,相比第一代标准具有更高的调制要求,更强的前向纠错系统和30%的通信容量增益。DVB-S2标准阐述了不同码长,不同码率下LDPC码的编码过程,根据该编码过程,能够得到对应的校验矩阵。DVB-S2标准下的LDPC码性能接近香农极限,结合8PSK,16APSK或32APSK的调制体系,LDPC码能够满足数字视频通信的要求。此外,LDPC码在 DVB-SH(Digital Video Broadcasting-Satellite to Handheld)标准,DVB-RCS(Digital Video Broadcasting Return Channel via Satellite)标准中都得到了应用[1]。

近些年,LDPC码译码算法研究和译码器设计受到国内外学者的关注。2004年,Dale E.Hocevar提出了基于行的分层译码算法,该算法所需迭代次数减少到并行译码算法的一半[2]。2005年,Juntan Zhang和Marc P.C.Fossorier提出了Shuffled BP译码算法,该算法与Dale E.Hocevar提出的分层算法类似,只是其分层是基于列[3],其性能与基行分层译码算法相近。2009年,Chang-Soo Park等人也设计了码长为64800 ,码率为0.5的DVB-S2标准LDPC码,该译码结构基于内存共享,并行度为90,吞吐率为277 Mbit/s[4];2009年,国防科技大学张波涛等人在IEEE上提出了基于RMP(Row Message Passing,基行信息传递)译码顺序和最小和算法的DVB-S2标准LDPC码译码器,当码率为9/10,时钟为320 MHz时,译码速率达998 Mbit/s[5]。黄秋元等人在2009年对各种译码算法的性能做了总结,提出一种改进的min-sum算法以实现复杂度和性能的折中[6]。

1 编码器硬件结构

在线性分组码中,某一奇偶位的编码值是其所在任一校验方程中其余比特位(包括信息位和奇偶位)的模二和。同时,由于LDPC码奇偶位所在列H1具有“Z”性结构,其编码可通过先后两步实现[1]:

1)依次完成每个信息位m对与之相连的校验节点集合j∈C(m)的贡献,贡献是指C(m)中每个校验值累加信息位m的值。

2)校验值的累加输出。

第m个信息位贡献的校验节点通过式(1)计算得到。

每个信息位m对校验值的贡献是可并行的,这可提高编码速率。图1给出了适用于所有码长和码率的LDPC码编码器。由DVB-S2标准可知,奇偶地址表一行的地址数最大为13,为了实现最大并行,编码器的并行度选用13。编码器主要包括校验位存储RAM、DVB-S2地址表储存ROM、贡献校验位计算模块、校验位更新模块、输出模块和编码参数控制单元。

图1 LDPC码编码器硬件结构

校验位存储RAM:双端口RAM,存储n×(1-R)个校验位,为了能并行编码,最大需13个RAM分开存储信息位对校验位的贡献。编码输出时,逐一将多个RAM中同地址的数据并行读给输出模块,未利用的RAM片选未使能。

DVB-S2地址表存储ROM:共13个ROM组,每个ROM组存储不同码型的地址表,每个地址表中第p行的第q个数据分别存储在第q个ROM的第p个地址。这样,信息位同步时钟经360分频后进行循环计数,计数结果p即可作为ROM的读地址,并行读出DVB-S2标准给出的地址表中的第p行,用于并行计算该信息位的所有贡献校验位。值得注意的是,地址表为空时,需禁止对相应校验位RAM更新。例如,对于短码0.6码率,当9≤p≤26且3≤q≤11,附录A地址表的值为空,此时需禁止对第3≤q≤11个校验位RAM的更新。

贡献校验位计算模块:包括360循环计数器和地址计算模块。完成(1)式的逻辑计算,得到信息位贡献校验位,即双端口RAM的地址。m mod 360通过360循环计数器输出,计数器时钟为信息位同步时钟。

校验位更新模块:将从校验位存储RAM读出的校验位与信息位模二和,并将结果重新写入同一地址,完成信息为对校验位的贡献。

输出模块:包括储存信息位的FIFO、异或电路和累加器。其中FIFO共n×R bit。当完成信息位对校验位的贡献后,输出模块先从FIFO中输出信息位,再同时将双端口RAM中的数据以地址递增的形式读出,读出的校验位依次经过多输入单输出的异或电路和单输入单输出的累加器,最终完成奇偶位的输出。在RAM中的校验位读出后,需立即将同地址内的数据清零,以备下一码组的编码。

编码参数控制单元:该单元根据码型选择,控制编码器其他单元完成对不同码型的编码。主要控制信号包括循环控制器循环周期控制信号和地址表选通控制信号。其中,前者根据信息位长度决定循环周期,以保证完成一个信息码组的编码后,地址表ROM的输入地址回到首地址,以完成对下一码组的编码;后者根据码型选通地址表ROM组中的不同ROM单元,完成不同码型编码需求。

2 译码器总体结构设计

LDPC码译码过程包括:变量节点初始化、变量更新、校验更新、求变量节点后验概率、译码停止判决和码字输出。

译码器总体结构如图2所示[4],共有6480 个校验节点信息存储字,一个RAM存储360个字,共需18个RAM;信息位和奇偶位后验概率的组织形式类似,分别占用27个RAM和18个RAM。

图2 LDPC码译码器硬件总体结构

SMP算法的校验更新通过CFM完成,本译码器共18个CFM,第i个CFM在第j个周期内,完成对18×j+i个校验节点的更新,0≤i≤17,0≤j≤359。在360个周期内,18个CFM并行完成了6480 个校验节点的更新。之所以如此安排CFM对校验节点的更新,是因为H1行之间具备周期性循环移位特性。在第j个周期内,第i个CFM为了完成校验更新,需从比特位(包括信息位和奇偶位)RAM中读入后验概率,而信息位RAM地址可通过第i个CFM第0个周期的起始地址循环加上j得到。如果信息位与奇偶位在RAM中储存位置设计巧妙,那么和每个CFM交织连接的比特位RAM可以固定下来。

该译码结构无BFM,通过将更新后的校验节点信息沿交织器原路径累加写入比特位RAM,即可完成SMP的变量更新。

3 DVB-S2标准LDPC码的性能

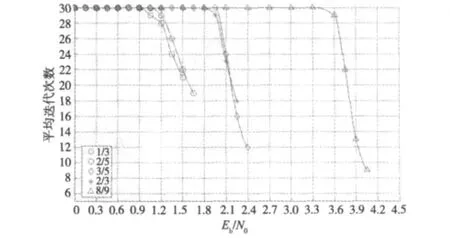

图3、图4和图5分别给出了DVB-S2标准下LDPC码码长为16200 不同码率的性能比较,包括误码率、误帧率和平均迭代次数。码率分别为1/3,2/5,3/5,2/3和8/9。译码算法为并行译码和min-sum算法,迭代次数30次,信道为高斯信道。

仿真结果表明:

1)当码长相等时,码率越低,则误码率、误帧率和平均迭代次数一般均越低。这是因为码率低,则校验位越多,能纠正的错误越多。

图5 DVB-S2标准LDPC码短码不同码率的平均迭代次数

2)比较3/5和2/3码率的仿真结果发现,码率2/3虽然大于3/5,但是其误码率和误帧率仍低于后者。事实上,该两种码率大小近似相等,不同之处在于校验矩阵,LDPC码校验矩阵的优化设计对译码性能的提高至关重要。

3)在实际应用中,信噪比较大,译码所需平均迭代次数远低于30次,应该根据具体环境噪声,选择合理迭代次数,尽量减少译码延时。

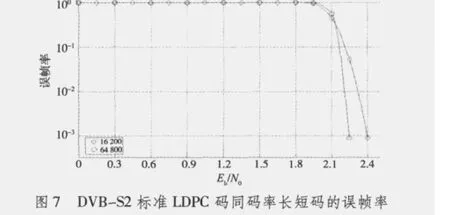

图6和图7分析了同码率下不同码长的性能比较。码率为3/5,译码算法为并行译码和min-sum算法,迭代次数30次,信道为高斯信道。

仿真结果表明,在码率相等时,码长越长则误码率和误帧率越低。同码率不同码长的码组,虽然校验位和信息位的比例相等,但是码长越大,校验位和信息位的约束更强,则性能越优。

4 结束语

本文根据DVB-S2标准规则设计出了LDPC码编码器并且利用校验矩阵周期特性,以16200 码长和0.6码率为例设计了基于共享内存和后验概率累加储存的译码器结构,减少了变量节点更新所需要的资源消耗。对码长为16200 不同码率LDPC码的误码率、误帧率和平均迭代次数性能比较。分析了同码率下不同码长的性能比较,在码率相等时,码长越长则误码率和误码率越低。同码率不同码长的码组,虽然校验位和信息位的比例相等,但是码长越大,校验位和信息位的约束更强,则性能越优。

[1]ETSI EN 302307 V1.2.1,Digital video broadcasting(DVB);second generation framing structure,channel coding and modulation systems for broadcasting,interactive services,news gathering and other broadband satellite applications(DVB-S2)[S].ETSI,2009.

[2]HOCEVAR D E.A reduced complexity decoder architecture via layered decoding of LDPC[C]//Proc.IEEE Workshop on SIPS 2004.[S.l.]:IEEE Press,2004:107-112.

[3]ZHANG J,FOSSORIER M.Shuffled iterative decoding[J].IEEE Transactions on Communications,2005,53(2):209-213.

[4]CHANG S P,SEONG W K,SUN Y H.Design of a low-area,highthroughput LDPC decoder using shared memory banks for DVB-S2[J].IEEE Transactions on Consumer Electronics,2009,55(2):850-854.

[5]ZHANG Botao,LIU Hengzhu,CHEN Xucan,et al.Low complexity DVBS2 LDPC decoder[C]//Proc.VETECS 2009.[S.l.]:IEEE Press,2009:1-5.

[6]黄秋元,陈兵.DVB-S2标准IRA-LDPC译码算法研究与改进[J].电视技术,2009,15(5):47-49.

[7]MANSOUR M M,SHANHHAG N R.Turbo decoder architectures for low-density parity-check codes[C]//Proc.IEEE GLOCOM 2002.[S.l.]:IEEE Press,2002:1383-1388.