一种高效的AVS自适应环路滤波器硬件设计

吴燕秀,黄有源,何明华

(福州大学物理与信息工程学院,福建 福州 350002)

音视频编码标准(AVS)是我国具有知识产权的第二代信源编码标准[1]。与 MPEG-2和H.264/AVC相比,AVS具有性能高、复杂度低、实现成本低、专利授权费用低的优势[2]。与MPEG标准相似,AVS标准也采用了基于块的DCT变换,这就带来了边界的块效应。为了消除块效应,标准引入去块效应环路滤波器。去块效应滤波器在包括MPEG-4,H.264,AVS以及VC-1等视频编码标准中扮演着重要的角色,是视频图像在低码率情况下,保持清晰主观效果的主要技术保障。

AVS环路滤波,可以采用类似H.264/AVC相似的滤波算法和硬件结构。目前针对H.264/AVC的环路滤波研究比较多,如文献[3]至[4]提出了实现方案。文献[3]通过改进滤波数据的缓冲以及片上存储空间的调整,优化了去块滤波的性能;文献[5]提出了4级流水线设计大大提高了滤波器的数据吞吐能力;文献[4]通过门控时钟降低了电路的功耗。本文根据AVS中环路滤波器的特点,设计了一种基于流水线技术的硬件结构完成自适应环路滤波处理[3-5]。为了进一步缩短宏块滤波的周期,将8×8块进一步划分,按照4×4块进行滤波。采用优化的滤波顺序和适当增加片上存储,在满足实时滤波处理的同时,有效地减少了总线的压力,利于AVS环路滤波的ASIC实现。

1 AVS环路滤波算法

1.1 滤波边界

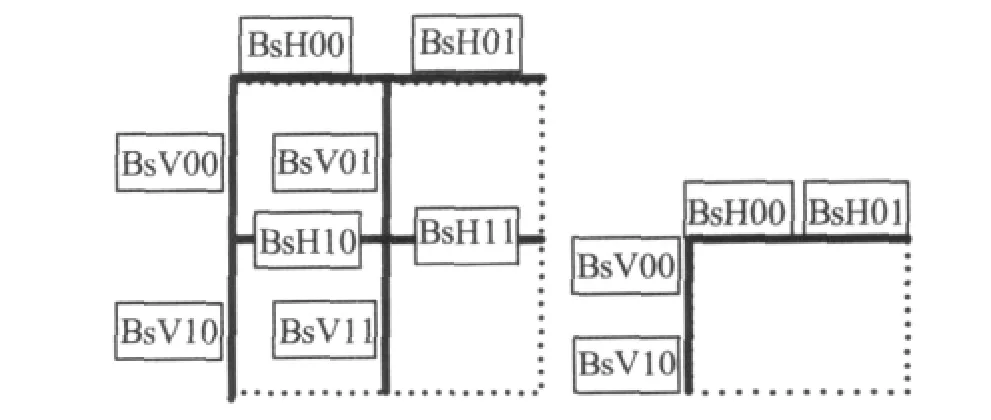

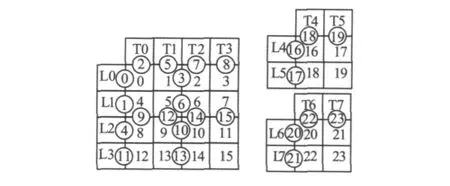

AVS标准中规定:环路滤波以宏块为单位,按照光栅扫描顺序依次处理不包括图像边界及条带边界的所有宏块边界。每个宏块按照从左到右的垂直边界滤波,从上到下的水平边界滤波,先亮度后色度的顺序对最小尺寸的块边界进行滤波。图1所示为4∶2∶0格式的宏块滤波边界。

图1 AVS宏块滤波边界

1.2 滤波强度

AVS中对每个8×8块的边界有一个边界强度(boundary strength),简称BS。色度块的边界强度与对应位置亮度块相同的边界强度。BS的取值为0,1或2,若BS等于0的边界不做处理,BS等于1和2的边界均要进行滤波。BS的推导过程如表1所示。

表1 AVS边界强度

1.3 滤波阈值

图2中表示块p和块q在水平或垂直边界两侧的6个样本点(边界用黑色粗线表示)。AVS利用这6个像素来判断边界是否为虚假边界。

图2 8×8块水平或垂直边界样本

在边界强度BS不等于0的情况下,滤波器可以根据编码时给的块边界阈值α和β来判断是否需要滤波,如果3个式子同时为真,即

则检测为虚假边界要进行滤波,否则保留原像素不滤波。

2 AVS环路滤波器硬件实现

2.1 流水线结构设计

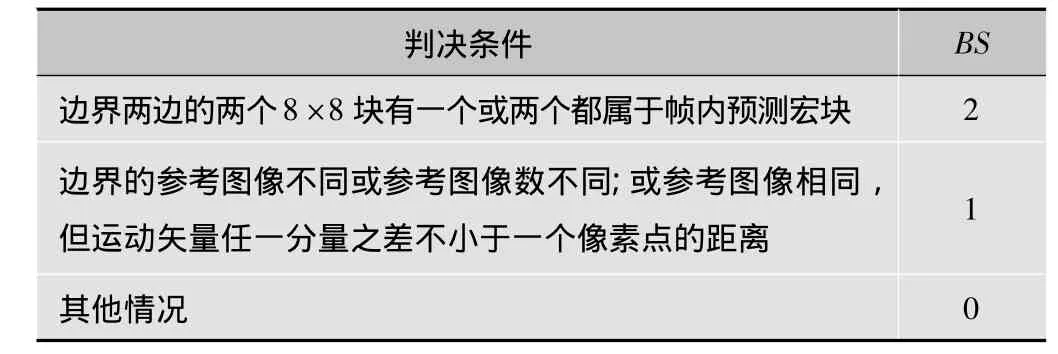

由于两个相邻子边界滤波操作的数据没有关联,所以滤波过程可以使用流水线处理,这样可以增大数据的吞吐率,加快滤波速度。图3所示为5级流水线的详细结构图。

图3 5级流水线结构图

每个待滤波的像素都要经过以下几个阶段。

1)存储器读:读取片上像素存储器,分配数据并完成滤波边界BS的读取。

2)阈值裁决:计算边界阈值α和β,并判断阈值条件是否满足,是否为真实边界。

3)预计算:当BS=2时,需要计算α >>2+2;当BS=1时,需要计算delta和滤波裁减参数c等。

4)滤波计算:根据之前得到的参数数据,完成BS=2滤波计算和BS=1滤波计算。

5)存储器写:存储经过滤波器滤波后的数据,数据将送到片外存储器存储。

2.2 门控时钟

使用门控时钟来实现选择性停止时钟。由于门控时钟技术可以为电路节约30% ~60%的功耗,所以常用于降低电路的功耗。在本文设计的自适应流水线中,若BS=0或者不满足滤波的条件时(如真实边界阈值条件没达到),可以将流水线相关模块的时钟停止,不对该块中的像素进行滤波,这也是门控时钟的原理。门控时钟设计如图4所示。

图4 门控时钟设计

2.3 滤波顺序优化

AVS视频标准给出8×8块边界滤波的基本顺序是从左到右,从上到下。若按标准所给的顺序滤波,不仅需要大量的存储空间而且滤波的速度也较慢。因此,本文对滤波器的滤波顺序进行了优化,优化的原则有以下3个:1)保证边界滤波的先后顺序不变,将8×8块进一步划分,按照4×4块进行滤波,不影响滤波效果;2)能够让流水线畅通地流动,避免数据冲突,提高流水线的效率;3)尽可能地减少数据的读写,配合使用转置缓冲器,尽可能地减少缓存面积。重新安排滤波顺序,如图5所示。改进后的滤波顺序,共24条4×4的边界,水平滤波和垂直滤波交叉进行,但并不影响滤波结果。

图5 改进后的滤波顺序

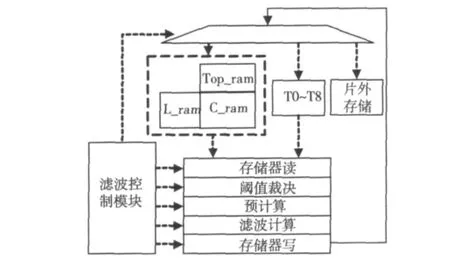

2.4 片上存储器设计

合理高效的存储器设计能够让所设计的结构处理的更加流畅,在环路滤波器中也一样。本文所提出的存储器设计不仅配合了改进后的滤波顺序,使流水线效率提高,而且最大限度地降低存储器的面积。对于较大的存储器使用SRAM设计,较小的如转置缓冲器则使用寄存器堆来实现。存储器结构图如图6所示。

图6 存储器结构图

1)左边界像素存储器,标记为L_RAM,存放左侧相邻宏块数据。使用单端口SRAM,共需32×32 bit。

2)上边界像素存储器,标记为U_RAM,存放上边相邻宏块的数据。为了提高总线效率,保证滤波不被堵塞。采用双端口,3840 ×32 bit的SRAM(可用于1920 ×1088 的HDTV)。

3)当前宏块存储器,标记为C_RAM,存放重建后的待滤波宏块数据。考虑模块间的流水,采用两个单端口的SRAM,96×32 bit,实现乒乓操作。当一个存储器读出滤波数据时,另一个存储器写入重建数据。

4)转置缓冲器,标记为T0~T8,需要4×4块转置,即行列转换。每个缓冲器容量为8×4×4 bit,共需存储容量1152 bit。TO,T1,T2和T3起转置当前宏块数据的作用,T5和T6的作用上边相邻宏块数据转置,T4,T7和T8的作用临时存储。

2.5 滤波过程

本文提出的环路滤波硬件结构如图7所示。滤波时按照图5所示的滤波顺序,配合图6的存储结构,具体的行列滤波过程如图7所述。

图7 环路滤波硬件结构

垂直边界滤波,以边界0为例。样本p像素和q像素来自左边界像素存储器L_RAM和当前宏块像素存储器C_RAM。4个时钟后边界0滤波完成,判断滤波后的p像素不会再使用则将p像素直接输出到片外存储器保存。而滤波后的q像素值需用作边界2的滤波样本值,所以需要将这些像素保存至转置缓冲器中,由于边界2为水平滤波,所以缓冲的数据需经过转置后保存,等待边界2的滤波。同理,对其他垂直边界进行滤波。随着边界0,1,4和11滤波结束后,块1,5,9和13也作为后续边界滤波的左侧数据也将陆续写入转置缓冲器中。

水平边界滤波,以边界2为例。样本p像素来自上边界像素存储器U_RAM,样本q像素来自经过0边界滤波后保存在转置缓冲器的像素。经过4个时钟周期以后,当前滤波边界结束,经过滤波后的p像素在以后的滤波过程中,不会重新滤波,经转置后暂存在缓冲器,以便后续输出到片外存储器。经过滤波后的q像素同样在以后的滤波过程中,不会重新滤波,经过转置后暂存在缓冲器。随着边界2,5,7和8滤波结束后,块4,5,6和7作为后续边界滤波的上侧数据也陆续写入上边界存储器中。

由上文分析可以看出,无论垂直边界还是水平边界,每条边界滤波都需要4个时钟周期。每个宏块滤波中需要的滤波边界总数为24,故进行滤波计算需要96个时钟。为了避免资源冲突,宏块需要4×4个额外的时钟周期来完成存储到片外存储器。所以完成整个宏块的滤波需要96+16=112个时钟周期。

3 仿真结果和分析

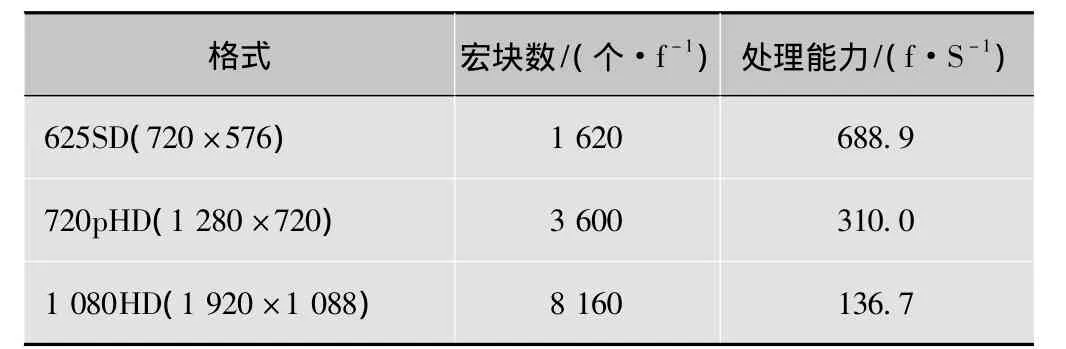

提出一种高效AVS环路滤波硬件设计,使用了Verilog HDL语言进行RTL级描述,用AVS软件RM52的C程序产生测试码流,应用了Modelsim 6.5c仿真平台进行了逻辑功能的仿真验证。采用Synopsys的Design Compiler在0.18 μm SMIC CMOS工艺库综合,在最大频率为125 MHz时,电路规模为20.7千门。表2给出了在125 MHz时钟时,625SD,720pHD,1080 HD这3种格式下,环路滤波的处理能力,这表明本文所设计的结构能够有效地支持标准清晰度和高清晰度视频解码的实时滤波处理。表3将本文提出的结构与其他几种环路滤波结构进行了比较,通过比较可以看出,本设计与文献[3]的设计均可满足对HDTV图像的实时处理(1280 ×720,60 f/s),但本设计的宏块处理周期减少55.2%,处理能力提高了64.1%。

表2 125 MHz时钟环路滤波的处理能力

表3 几种去块滤波器综合结果比较

4 小结

本文针对AVS视频标准,提出了一种高效的AVS环路滤波器硬件设计。设计使用了5级流水线结构,通过优化滤波顺序,适当地增加片上数据存储空间,大大地缩短了处理一个宏块的周期。实验结果表明,本设计电路规模为20.7千门,处理一个宏块只需要112个时钟周期。能够以136.7 f/s的帧率对分辨力为1920 ×1088 的图像进行滤波处理。与同类设计相比,本设计电路规模小,处理能力高,能够支持AVS高清视频的实时滤波处理。

[1]GB/T20090.2—2006,信息技术先进音视频编码第2部分:视频[S].2006.

[2]SHENG Bin,GAO Wen,WU Di.A platform-based architecture of loop filter for AVS[C]//Proc.International Conference on Signal Processing.[S.l.]:IEEE Press,2004:571-574.

[3]LIU T,LEE W,LIN T,et al.A memory-efficient deblocking filter for H.264/AVC video coding[C]//Proc.IEEE International Symposium on Circuits and Systems.[S.l.]:IEEE Press,2005:2140-2143.

[4]KE X,CHOY C.A five-stage pipeline,204 cycles/mb,single-port SRAM based deblocking filter for H.264/AVC[J].IEEE Transactions on Circuits and Systems for Video Technology,2008,18(3):363-374.

[5]NAM T T,JINSEON Y,HUIGON K,et al.Low-power high-throughput deblocking filter architecture for H.264/AVC[C]//Proc.2009 International Conference on Electronic Computer Technology.[S.l.]:IEEE Press,2009:627-631.