基于FPGA的IRIG-B(DC)码的解码方案的设计与实现

王丽敏,胡永辉,侯雷,刘军良,3

基于FPGA的IRIG-B(DC)码的解码方案的设计与实现

王丽敏1,2,胡永辉1,3,侯雷1,3,刘军良1,2,3

(1. 中国科学院国家授时中心,西安 710600;2. 中国科学院研究生院,北京 100039;3. 中国科学院精密导航定位与定时技术重点实验室,西安 710600)

IRIG-B码是国际上通用的时间码格式,广泛应用于各种系统的时间同步。针对IRIG-B(DC)码的调制特性,介绍一种基于FPGA的B码解调方案。重点描述了如何在同步时序中准确提取秒同步信号并解调B码中包含的时间信息。整个方案中采用Verilog HDL语言进行设计,已成功实现,并给出了验证结果。

IRIG-B(DC)码;现场可编程门阵列;同步;解调

0 引言

在靶场,我们把为常规武器试验、导弹试验、航天器发射、测控系统提供标准时间信号和标准频率信号的一整套电子设备称为时间统一系统,简称“时统”[1]。时统设备是向各个设备提供标准时间信号和标准频率信号的设备。

时统设备送给用户的是标准格式的时间编码信号,我们可以将时间统一系统产生的编码信号转化为B码信号,用B码进行传输,在其他用户端通过IRIG-B码解码器来获得各种时间和频率信号[2]。IRIG-B码解码器又称为IRIG-B码解码终端,它是用户设备的有机组成部分,能否实现系统的时间统一,IRIG-B时间码接口终端是重要的一环[3]。

1 IRIG-B时间码简介

IRIG(inter range instrumentation group)是美国RCC(Range Commanders Council)所属的负责制订靶场标准等工作的机构。靶场时统和通信系统的标准化工作是IRIG所属的TCG(tele-communication group)负责的,它所制订的标准时间格式有两大类:一类是并行时间码格式,另一类是串行时间码格式。

IRIG-B码是一种串行格式的时间码,分为直流码(DC)和交流码(AC)2种。B(DC)码的帧周期为1s,码元速率为每秒100脉冲,从秒准时点起,按秒、分、时、天等时间信息进行编码,如图1所示。B码中每个脉冲称为码元,每个码元的准时参考点是该脉冲的前沿。B码的信息采用脉宽调制的方式表示,码元宽度有3种,即2、5和8ms,如图2所示。为了便于提取B码中的信息,每10个码元中有一个位置识别标志,其宽度为8 ms,位置识别标志分别称为P1,P2,…,P9,P0。参考标志是由位置识别标志P0和相邻的参考码元PR组成的,参考码元PR的宽度也为8ms,而且PR的前沿即该帧B码的准秒时刻,因此可以说参考码元PR是B码中最重要的码元。B码中表示时间信息的码元共有30个,这些码元称为码字。表示二进制“1”的码字宽度为5 ms,表示二进制“0”的码字宽度为2 ms。

图1 IRIG-B(DC)码波形示意图

图2 B码码元类型

2 FPGA解码及其算法

与传统使用单片机及其外围电路进行B码解调相比,使用FPGA(现场可编程门阵列),具有运行速度快,效率高和内部时延小的优点,并且FPGA有大量软核,可以方便地进行二次开发。因此,使用FPGA来实现B码的同步解码具有很大的优势[4]。

采用FPGA进行B(DC)码的解码最终是要同步提取出1 PPS和8421BCD格式的时间信息[4],其关键是码元的识别与提取。整个方案采用Verilog HDL语言进行设计,其解码过程示意于图3。

图3 B码解调过程示意图

2.1 码元识别

2.1.1 脉宽计数

B码是脉宽调制的串行格式的时间码,因而对码元的识别最直接的方式是对码元时宽计数,再根据计数值判断相应码元的值“0”、“1”和标志位。本方案采用1 kHz的时钟对码元的持续高电平计数,并在低电平时对计数值清零。由于输入的B码信号与时钟可能存在同步误差,所以对于码元宽度的计数值不能采用固定的计数值。对于宽度为2 ms的码元,计数值为1,或2,或3时,判断码元的值为二进制数“0”;宽度为5 ms的码元,当计数值为4,或5,或6时,判断码元的值为二进制数“1”;宽度为8 ms的码元,当计数值为7,或8,或9时,判断码元为参考标志。

2.1.2 码元赋值

码元的赋值是在脉宽计数完成之后,码元的下降沿处完成的。定义一个2位的寄存器用来存储码元的值,值为0的码元存储为“00”,值为1的码元存储为“01”,位置识别标志分别为码元P1,P2,…,P9,P0,它们的值存储为“10”。

用Verilog HDL设计的可综合模块,必须避免使用异步时序逻辑,这是因为许多综合器不支持异步时序逻辑的综合,而且用异步时序逻辑确实很难控制由组合逻辑和延迟所产生的冒险和竞争[5]。

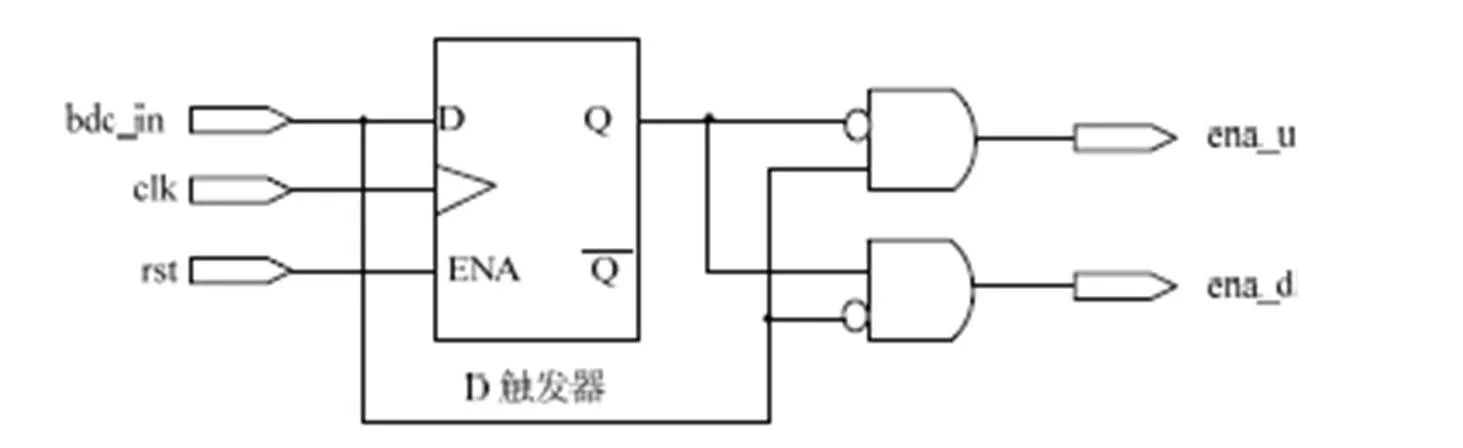

为了满足以上FPGA的同步时序设计原则,首先同步提取出B码中码元上升沿和下降沿处的窄脉冲,码元的上升沿窄脉冲在之后的码元计数时会用到。这样在设计中可以采用这些窄脉冲作为使能条件,而始终采用时钟的上升沿作为唯一确定的触发条件,即保证了同步时序的设计原则。码元边沿窄脉冲如图4所示。

注:clk表示10 MHz的计数时钟,bdc_in表示输入的B(DC)码信号,rst表示复位信号,ena_d表示码元下降沿窄脉冲,ena_u表示码元上升沿窄脉冲。

为了得到码元的上升沿窄脉冲,将输入的B码信号延迟一个计数时钟,并与其取反信号进行相与操作即可得到码元上升沿的窄脉冲ena_u;同时,将B码输入信号延迟取反之后与原输入信号进行相与即可得到码元下降沿的窄脉冲ena_d。其产生原理如图5所示。

图5 上升沿、下降沿窄脉冲产生原理

2.2 秒信号1PPS的同步提取

要获得1 PPS信号,首先要判断出B码中每一帧的秒准时点。

在图1中可以看到,连续2个P码元的第2个P码元的前沿即为秒的帧头。对帧头的定位设计了一个三段式状态机。所谓三段式状态机,就是使用3个always模块,其中一个always模块采用同步时序的方式,描述状态转移,第2个always模块采用组合逻辑的方式,判断状态转移,状态转移条件,描述状态转移规律,第3个always模块使用同步时序电路描述每个状态的输出。这种三段式结构的优势是使状态机做到了同步寄存器输出,消除了组合逻辑输出的不稳定与毛刺的隐患,而且更利于时序路径分组。一般来说在FPGA/CPLD等可编程逻辑器件上采用这种结构会使得综合与布局布线的效果更佳[6]。

在这个状态机中,设计了3个状态:IDLE,STATE 1和STATE 2,其中初接始状态是IDLE,STATE 1表示接收到一个P码元,STATE 2表示连续接收到2个P码元,图6是状态示意图。

状态机的初始状态是IDLE,当接收到P码元时,状态转移到STATE 1,否则保持IDLE状态不变;当处于STATE 1状态时,若接收到P码元,则状态转移到STATE 2,否则状态回到IDLE;当转到状态STATE 2时,接收到任何码元,状态都跳转到IDLE。

在进入状态STATE 2时,状态机产生一个高电平信号,此后整个解码工作将在高电平持续期间进行。对高电平持续期间,设计了一个码元计数器,这个计数器在每个码元的上升沿实现加1操作,当加到99个码元的时候将高电平信号清零,同时产生一个1PPS的控制脉冲pps_pulse。这个脉冲相当于一个门限信号,与下一个码元的上升沿窄脉冲进行与操作可以准确地得到B码地秒准时点1 PPS信号。如图7所示。

图6 状态机示意图

图7 1 PPS的产生原理

2.3 时间信息的获取

由之前对B码的介绍可知,B码的每一帧中1~41个码元用来表示秒、分、时、天个位、天十位、天百位的时间信息,所以定义一个41位的寄存器Memory[41:1]来存储1~29码元的值,同时定义9个4位的寄存器分别用来存储秒个位(second_l),秒十位(second_h),分个位(minute_l),分十位(minute_h),时个位(hour_l),时十位(hour_h),天个位(day),天十位(m_day)和天百位(h_day)的信息。

B码的编码采用的是8421BCD格式,因而在进行B码的解调时,当获得二进制表示的每个码元值时,只需要将码元值的最低位“0”或“1”,存到寄存器中,便可进行8421BCD与二进制的转换。

当码元计数器的值为99时,对之前定义的秒、分、时、天个位、天十位、天百位寄存器赋值,Verilog HDL语句实现如下:

Second_l<=Memory[1]×1'd1+Memory[2]×2'd2+Memory[3]×3'd4+Memory[4]×4'd8;

Second_h<=Memory[6]×1'd1+Memory[7]×2'd2+Memory[8]×3'd4;

Minute_l<=Memory[10]×1'd1+Memory[11]×2'd2+Memory[12]×3'd4+Memory[13]×4'd8;

Minute_h<=Memory[15]×1'd1+Memory[16]×2'd2+Memory[17]×3'd4;

Hour_l <=Memory[20]×1'd1+Memory[21]×2'd2+Memory[22]×3'd4+Memory[23]×4'd8;

Hour_h<=Memory[25]×1'd1+Memory[26]×2'd2;

Day<=Memory[30]×1'd1+Memory[31]×2'd2+Memory[32]×3'd4+Memory[33]×4'd8;

M_day<=Memory[35]×1'd1+Memory[36]×2'd2+Memory[37]×3'd4+Memory[38]×4'd8;

H_day<=Memory[40]×1'd1+Memory[41]×2'd2;

其中,1'd1、2'd2、3'd4和4'd8分别代表二进制形式转化为8421BCD格式时,对应位相乘的加权值,即十进制的1、2、4和8。

3 实验结果与分析

整个方案采用Verilog HDL语言编写代码,并在Altera公司的cycloneii系列型号为EP2C20Q240C8的芯片中成功实现,图8是FPGA解码模块方框图。

图8 FPGA解码模块图

使用Altera的QUARTUSⅡ进行Verilog HDL语言的设计与编译,并用Modelsim进行仿真,结果如图9所示。如图中竖线所示,在参考码元上升沿处准确同步提取了1PPS信号,且显示解调的时间为 115d 21 h 18 min 59 s与输入的时间一致,其中second_l,second_h,minute_l,minute_h,hour_l,hour_h,day,m_day,h_day分别代表秒个位,秒十位,分个位,分十位,时个位,时十位,天个位,天十位,天百位。解调的时间可以通过接口电路在七段数码管上正确显示,证明了本方案的可行性。

图9 解码结果图

4 结语

以上介绍了一种基于FPGA的IRIG-B(DC)码的解码方案,本方案在altera公司的cycloneii系列型号为EP2C20Q240C8的芯片中实现,占用芯片资源非常少,不到5%,完全可以在同一块芯片上完成后续B(AC)码的解调,这在很大程度上节约了芯片资源。此外,与传统利用单片机实现相比,大大减小了电路设计的复杂度,增加了设计的灵活性。在整个解码中,采用Verilog HDL代码实现,具有方法简单、易读和可重用性强的特点。设计完全在同步时序中完成,避免了异步时序可能导致的竞争与冒险,因而在时间同步系统中应用前景广阔。

[1] 刘凯. 时间统一技术研究及应用[D].西安: 西安电子科技大学, 2010.

[2] 吴坤, 张君. 基于 GPS 的靶场时统系统技术研究[J].国防技术基础, 2009, 3: 57-59.

[3] 童宝润. 时间统一系统[M]. 北京: 国防工业出版社, 2000.

[4] 陈曦, 刘方. 基于FPGA的IRIG-B(DC)码的解码方案[J]. 仪器仪表用户, 2009, 16(3): 94-96.

[5] 夏宇闻. Verilog数字系统设计教程[M]. 2版. 北京: 航空航天大学出版社, 2008.

[6] 吴继华, 王诚. 设计与验证: Verilog HDL[M]. 北京: 人民邮电出版社, 2006.

Design and implementation of IRIG-B(DC) codedemodulation based on FPGA

WANG Li-min1,3, HU Yong-hui1,2, HOU Lei1,2, LIU Jun-liang1,2,3

(1. National Time Service Centre, Chinese Academy of Sciences, Xi′an 710600, China;2. Graduate University of Chinese Academy of Sciences, Beijing 100039, China;3. Key Laboratory of Precision Navigation and Timing Technology, National Time Service Center,Chinese Academy of Sciences, Xi′an 710600, China)

IRIG-B code is an universal format of time code in the world and is widely used in timing systems.According to the characteristics of IRIG-B code modulation, a decoding plan based on FPGA is introduced with emphases on how to extract the synchronous second signal accurately from the synchronous timing sequency and how to get the time information included in the B code. The whole project is designed by using Verilog HDL and has been implemented successfully with the results shown.

IRIG-B(DC) code; FPGA; synchronization; demodulation

TN76

A

1674-0637(2012)04-0228-07

2011-12-28

中国科学院“西部之光”人才培养计划重点资助项目(Y001YR1601)

王丽敏,女,硕士研究生,主要从事时间统一系统技术研究。