基于ARM+FPGA的IRIG-B码产生器的研制

高林,胡永辉,侯雷

基于ARM+FPGA的IRIG-B码产生器的研制

高林1,2,3,胡永辉1,2,侯雷1,2

(1. 中国科学院国家授时中心,西安 710600;2. 中国科学院精密导航定位与定时技术重点实验室,西安 710600;3. 中国科学院研究生院,北京 100039)

本设计中采用ARM芯片作为主控芯片,FPGA芯片作为主功能芯片,使用C和Verilog语言编程。通过软件控制生成IRIG-B(DC)码信号,由分频1 PPS信号和外部标准1 PPS信号锁相同步保证时标信号的同步,在产生DC码后采用基于FPGA内部ROM数字查找表技术实现AC码的数字调制。整体方案设计简单,应用方便。

IRIG-B码;ARM芯片;现场可编程门阵列(FPGA);数字调制

0 引言

时间统一设备在测控中提供一种符合标准的同步信号作为基本参考单位,这是非常重要的。我国在靶场测量,工业控制,航空航天,通信实验,电力系统维护等方面大多采用国际标准IRIG-B格式时间码(简称B码)作为同步标准。B码信号产生器作为时间统一设备的重要组成部分,其设计不仅要满足精度的要求,同时要考虑应用现场需求[1]。

在测试实验中,通过地面基准时频站和配备原子钟的时统车来保障测控设备间的时间同步,尽管可以满足精度要求,但成本较高,在飞行测试和其他移动测量中难以满足要求。随着我国卫星导航系统的不断建设和更为先进的授时技术不断发展,在此基础上设计研制成本低廉、性能良好、便于携带的IRIG-B码信号产生器可以很好地应用于移动测量中来保障时间统一,还可以广泛应用于国防实验、金融、电力等部门。本文正是基于实际项目需求,提出了使用ARM芯片和FPGA芯片的组合研制IRIG-B码信号产生器,设计中合理地使用集成器件,使得外围电路简单,逻辑清晰。采用本方案研制的IRIG-B码信号产生器具有高精度、低功耗、低成本和便于应用的特点,并且具有良好的人机交互性能。

1 IRIG-B码的编码格式

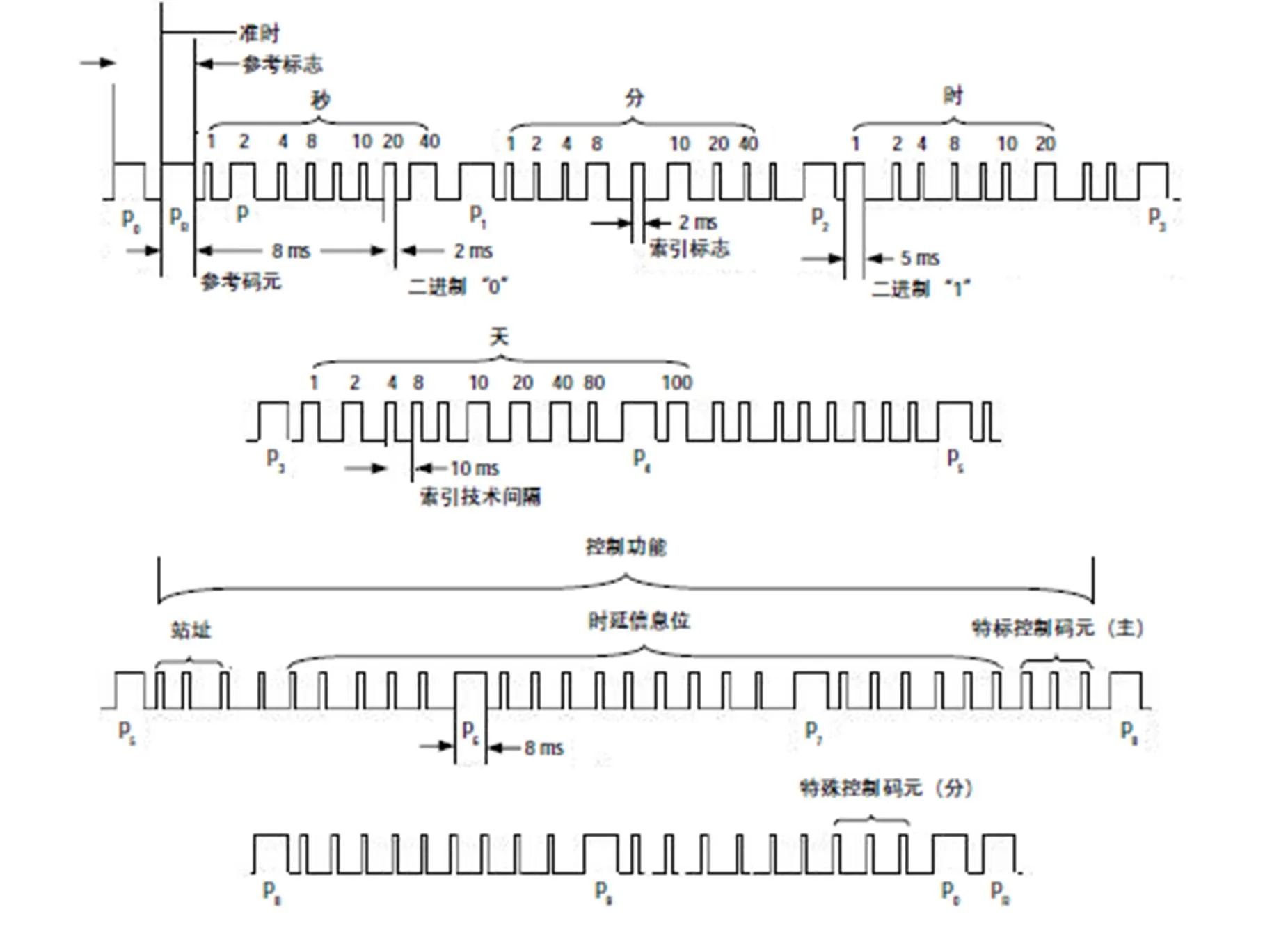

IRIG(inter range instrumentation group)规定的时间格式标准有两大类:一类是并行时间码,规定的4种并行时间码格式是PB1,PB2,PB3和PB4。这4种并行时间码一般主要用于卫星、导弹和空间飞行器的发射、测控、跟踪及其数据处理系统以及定时系统与用户之间近距离的实时并行二进制格式的时间信息的传输。受传输距离的限制,并行时间码远不如串行时间码应用广泛;另一类是串行时间码,按时帧的速率不同分为A,B,D,E,G,H 6种。其中IRIG-B码的帧速率为每秒1帧,每次传递100个码元,每个码元宽度为10 ms,用高电平宽度为8 ms的脉冲表示索引标记,用宽度为5 ms的脉冲表示逻辑1,用宽度为2 ms的脉冲表示逻辑0[2]。B码脉冲序列如图1所示。

图1 B码脉冲序列图

脉宽调制的IRIG-B码信号按照IRIG标准的习惯称为IRIG-B(DC)码。就直流码而言,由于每个码元为脉冲信号,因而其可以实现较高精度(纳秒量级)的时间同步,但由于脉冲信号的频谱丰富,窄带信道无法传输,而只适用于用电缆传输至近距离的用户,对远距离时统设备并且只有窄带信道相联系的用户,可以采用B(DC)码调制成B(AC)码的方法,如图2所示。用B(DC)码对标准正弦波载频进行幅度调制,标准正弦信号必须与产生B(DC)码的信号共源,以保持两者的时间关系一直不变,正弦波载频的频率与码元速率严格相关,一般为码元速率的10倍,B(AC)码低幅到高幅的正弦信号的正交过零点(如图2中的A点)与B(DC)码的准时点(即脉冲前沿)严格保持一致。同时,我国国军标规定标准调制比为10:3。

图2 典型的1 kHz调制信号

B码信号符合使用习惯,携带信息量大,译码后可获得多种脉冲信号、BCD编码的时间信息和控制信息,调制后的B码信号交流码还适用于远距离传输,具有标准化的接口,因此IRIG-B码被广泛应用于各种场合,形成国际标准。

2 硬件方案

2.1 系统原理

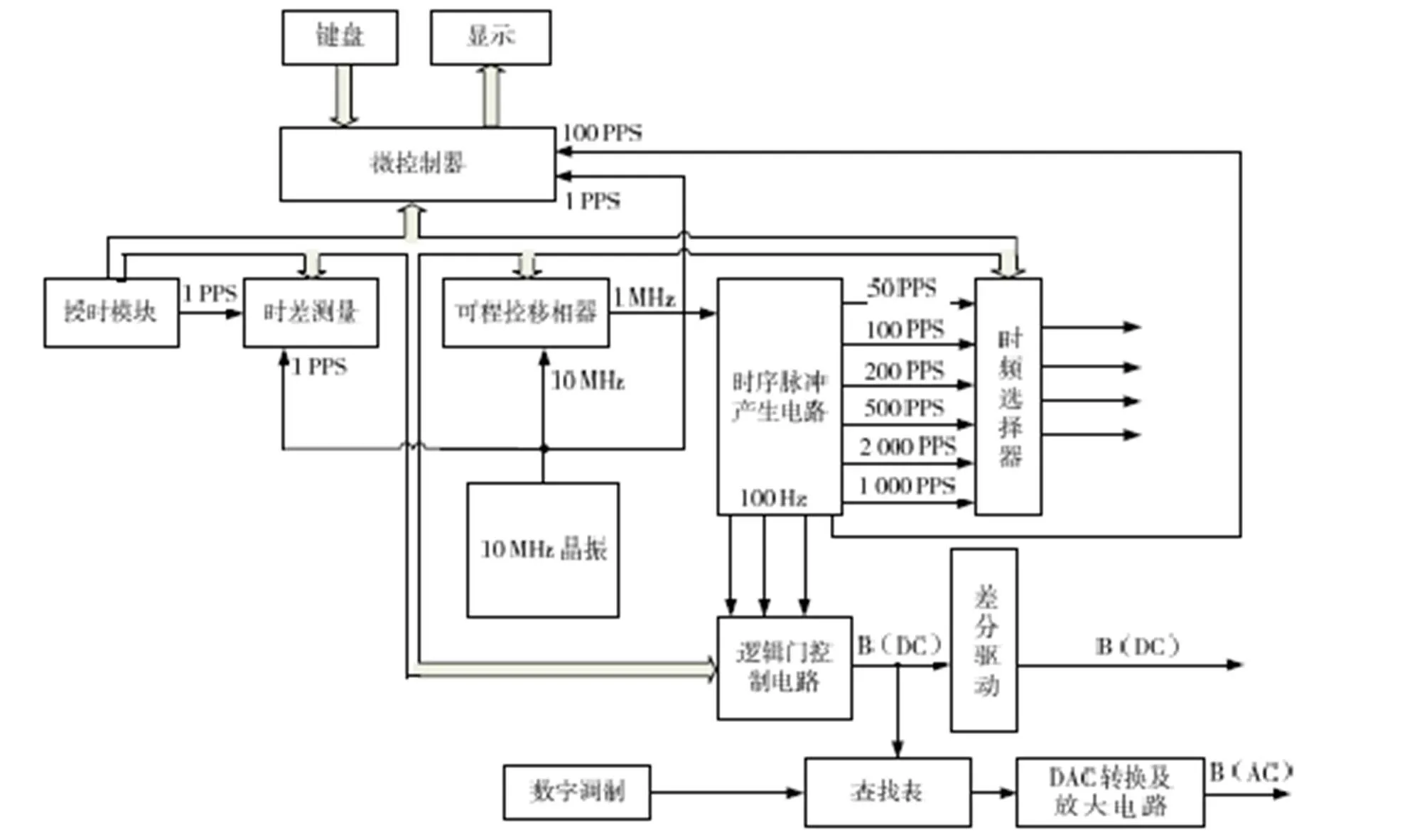

图3是该系统框图。系统由标准10 MHz的输入作为本地频率基准,通过FPGA内部数字分频链模块产生各种所需时标信息和符合IRIG-B码编码特征的脉冲序列,对分频产生的1PPS信号与外部授时模块提供的1 PPS标准信号进行时差测量,微控制器收集测量结果作为依据来调整程控移相器超前或者滞后,完成对外部标准1PPS信号的锁相同步。直流码的产生由ARM控制器编程软件控制逻辑门电路输出符合B码编码标准的时标信号完成,生成的直流码信号按要求进行驱动输出。FPGA内部ROM存储正弦调制信号的采样波形,产生的直流码信号在数字调制模块依据查找表输出相关的数字序列到DAC器件输出交流码信号,经过后置放大滤波处理按要求输出IRIG-B交流码信号。

图3 IRIG-B码信号产生器系统框图逻

2.2 输入模块

由图3可以看到本系统的信号源主要是授时模块的标准时间信息和1 PPS信号及10 MHz频率信号。针对卫星授时传递信号的编码特点,采用模块化设计,不仅降低系统设计难度,更增强了系统的实际应用性。只要符合RS232传输标准的时间信息均可作为系统输入,基于此特点,北斗系统、GPS系统、GLONASS系统的授时型接收机均可提供信号输入,应用灵活[2]。

2.3 控制模块和功能模块

设计中控制芯片采用STM32F103VBT6,该芯片使用高性能的ARM Cortex-M3TM32位的RISC内核;最高工作频率为72 MHz,在72 MHz时消耗36 mA(所有外设处于工作状态),待机时下降到2μA;128 k的程序存储空间和20k的RAM;最大程度地集成了复位电路、低电压检测、调压器、精确的RC振荡器等单元;外设接口丰富,2~3.6 V供电电压;工作于-40~+105℃的温度范围[3]。功耗表现突出,控制方便,设计简单,非常适合嵌入式的系统设计[3]。

本设计中ARM芯片STM32F103VBT6的控制功能主要包括接收授时模块信息进行钟面显示并完成标准时间的二进制编码存储;收集时差测量结果,控制移相器完成锁相同步;软件控制完成直流码产生;控制时标信号选择模块对时标信息进行控制输出等。

系统设计主要功能实现采用FPGA芯片EP3C10E144I7N,该芯片属于Altera Cyclone III 系列,该系列采用全铜、低K值、1.2 V SRAM工艺设计,不仅提高了飓风家族的低功耗、高性价比特点,在功能设计上更为完善。EP3C10E144I7N具有10 320个逻辑单元、内置46个M9K的RAM存储块,该芯片内置23个乘法器、2个锁相环(相对于Cyclone I和Cyclone II系列增加了动态重配功能)和10个全局时钟网络。最小输入频率为5 MHz,能直接接收外部10 MHz的标准频率输入。Cyclone III芯片支持热切换和上电复位,不需要额外复位芯片。相对于Altera Cyclone II系列的产品,设计难度降低,功耗更低,成本也不高[4]。

FPGA完成主要功能包括:数字分频链模块设计产生各种时标信号和直流码编码信号;时差测量和程控移相模块完成本地1PPS信号和外部标准的1 PPS信号的锁相同步;依据FPGA内部ROM查找表对直流码信号数字调制等。

2.4 输出模块

在输出设计上充分考虑项目应用需求,输出时标信号使用了TI(texas instruments)的驱动芯片SN54128,其输出具有50Ω的驱动能力,工作温度范围为-55~+125℃,且与SN74128(70Ω驱动能力)上下兼容[5]。IRIG-B(DC)码输出应用了AM26C31,即TI公司生产的一种低功耗,线性差分驱动芯片,符合EIA(electronic industries association)和ITU(international telecommunication union)声明的V.11接口标准。工作温度范围为-55~+125℃[6]。直流码调制后得到表示交流码信号幅度的数字序列值输出到DAC8311,TI公司的14位低功耗的数字模拟转换芯片[7],产生的交流码信号经后置电路处理输出符合要求的交流码信号。

2.5 基于FPGA的数字调制

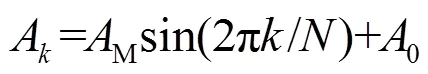

依据奈奎斯特抽样定理,如果信号的采样频率大于信号最高频率的2倍,则整个连续信号就可以用它的抽样值代替。如果抽样值序列是经过正弦信号以×(> 2)的频率进行抽样获得,则该正弦信号需在=1/的时间内等间隔输出个采样值至数模转换器(DAC),再经低通滤波器滤波后即可恢复原来的正弦信号。各采样点的值为

本设计中依据上述原理生成查找表文件,对标准1 kHz正弦信号进行200 kHz等间隔抽样,采样值输出需综合考虑实际选用的DAC器件,实际采样值输出表达式可写成

表1 FPGA正弦查找表

采用Matlab可以辅助生成存储于FPGA内ROM中的.mif文件,建立周期为5μs的定时器和地址计数器,定时器溢出,计数器加1。可以把生成的查找表对应逻辑0置于ROM上半部分,逻辑1置于下半部分,使用IRIG-B码输入信号作为地址高位,则对应的ROM输出即为DAC的调制输出,同时保证了直流IRIG-B码和交流IRIG-B码的严格相关性。

3 印刷电路版(PCB)原理图设计

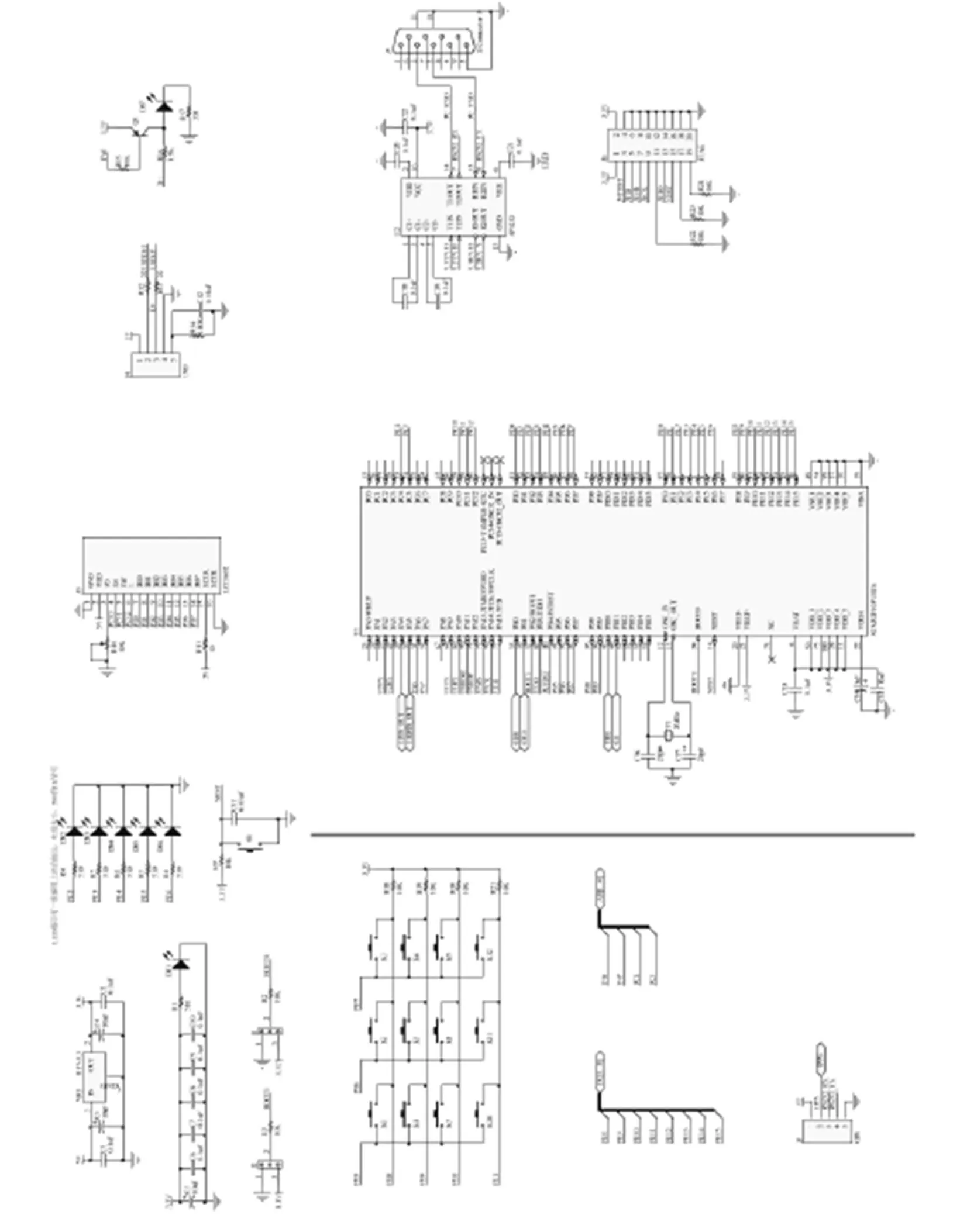

基于ARM+FPGA的IRIG-B码产生器的ARM控制器部分设计原理图和FPGA部分设计原理图分别如图4和图5所示。

图4 IRIG-B码产生器ARM控制器部分设计原理图

图5 IRIG-B码产生器FPGA部分设计原理图

4 软件控制

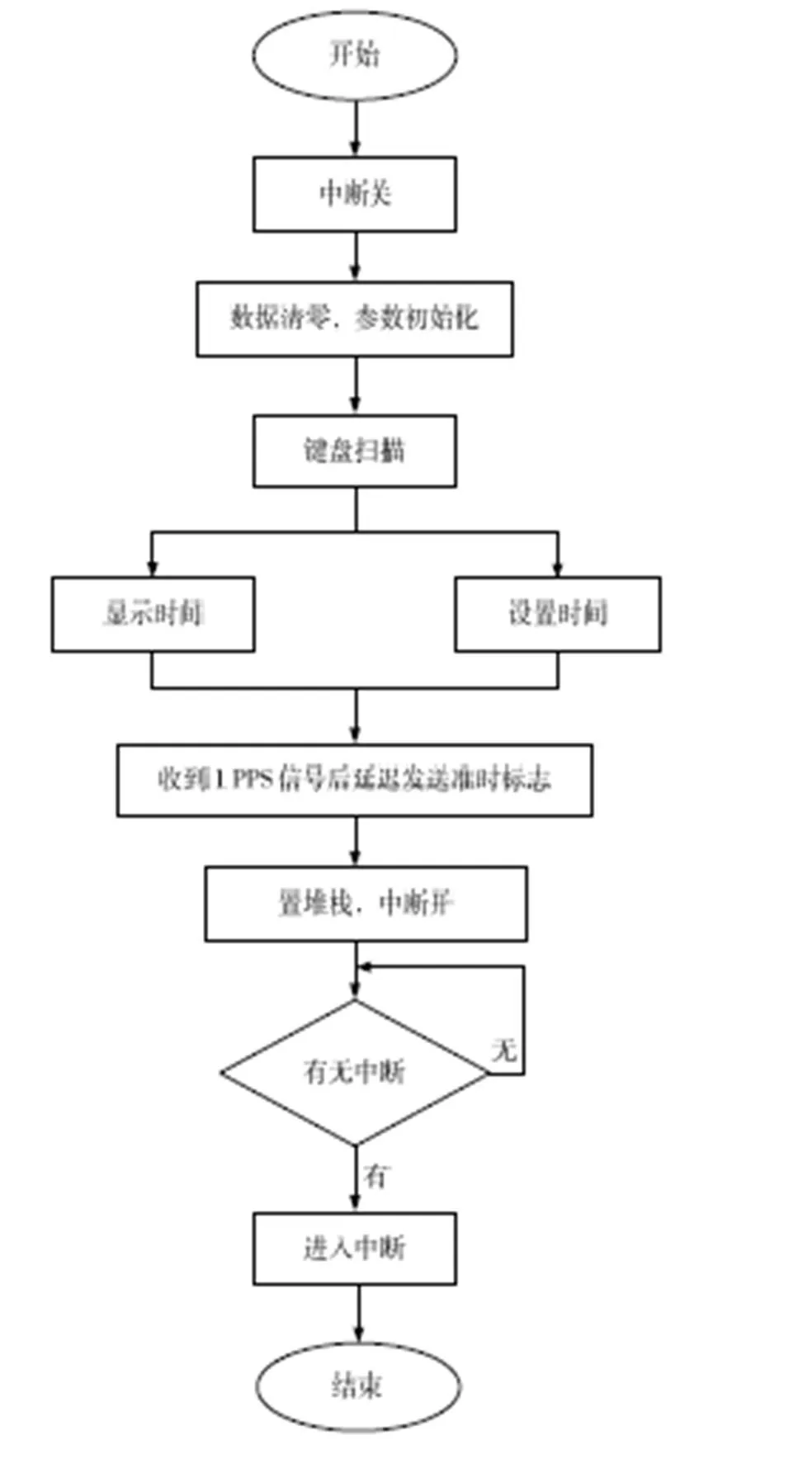

4.1 主程序控制流程

IRIG-B码信号产生器的主程序控制包括设备初始化、同步设置、发送准时参考标志、进行中断判定等工作。完成上电后设备首先进行状态检测,选择自动同步时间信息或者手动设定时间信息,钟面信息和设备状态信息送到LCD显示,当接收到标准1 PPS信号后,控制发送位置识别标志P0和参考码元,作为B码的准时参考标志,完成后进行中断判定,中断1则执行1 PPS中断程序,中断0则执行100 PPS中断程序。

ARM主程序控制流程如图6所示。

图6 B码信号产生器主程序流程图

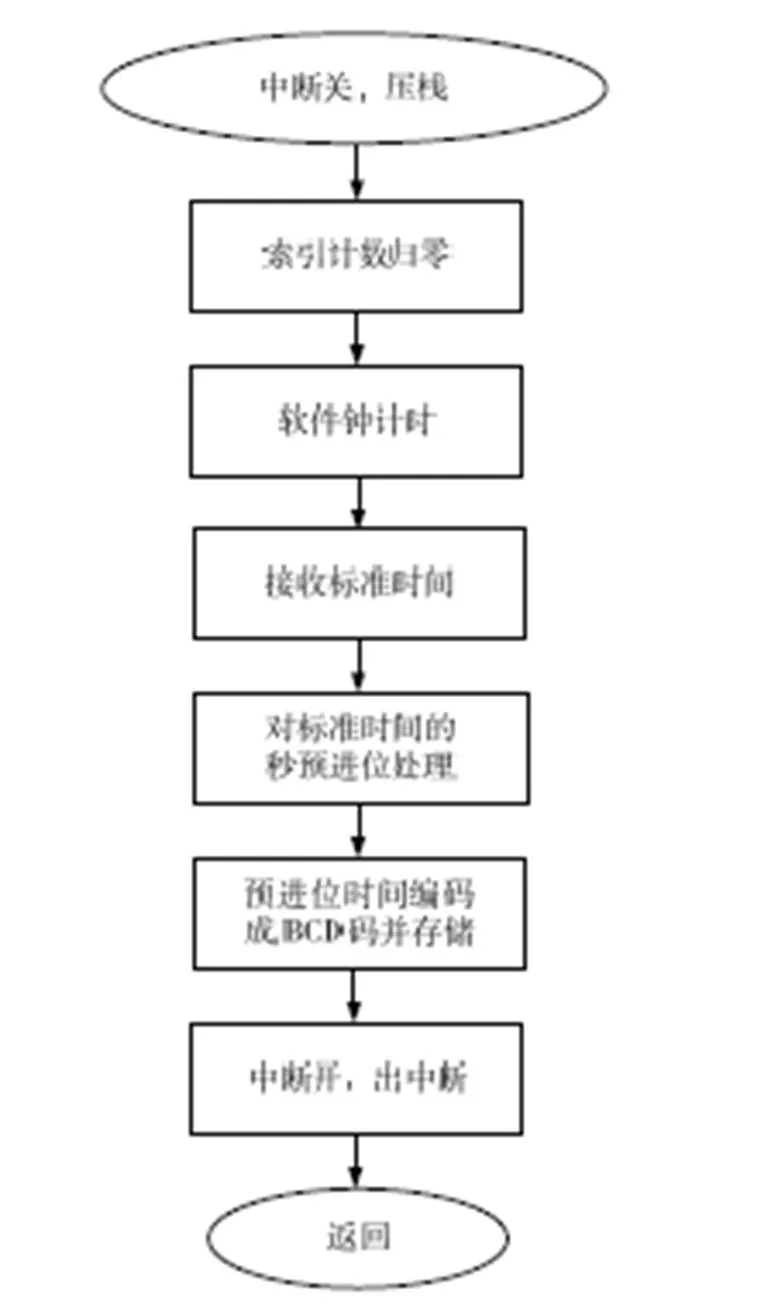

4.2 1PPS中断处理子程序

1 PPS中断子程序完成标准时间的提取和BCD编码,并控制索引计数的清零设置。通常为了保证提取到正确的绝对时间,在1 PPS上升沿送出当前时间,而ARM微控制器接收时间时,IRIG-B码的当前帧已经启动,形成IRIG-B码编码信号后需要等待下一个1PPS上升沿到来才发送出去,因此我们需要对接收的时间进行预进位处理后存储,以保证发送时间与标准时间之间的严格同步。预进位处理后的时间信息还要考虑闰年的大月、小月,这可以影响B码编码时的Day字段。

1 PPS中断处理流程如图7所示。

图7 B码信号产生器秒中断处理流程图

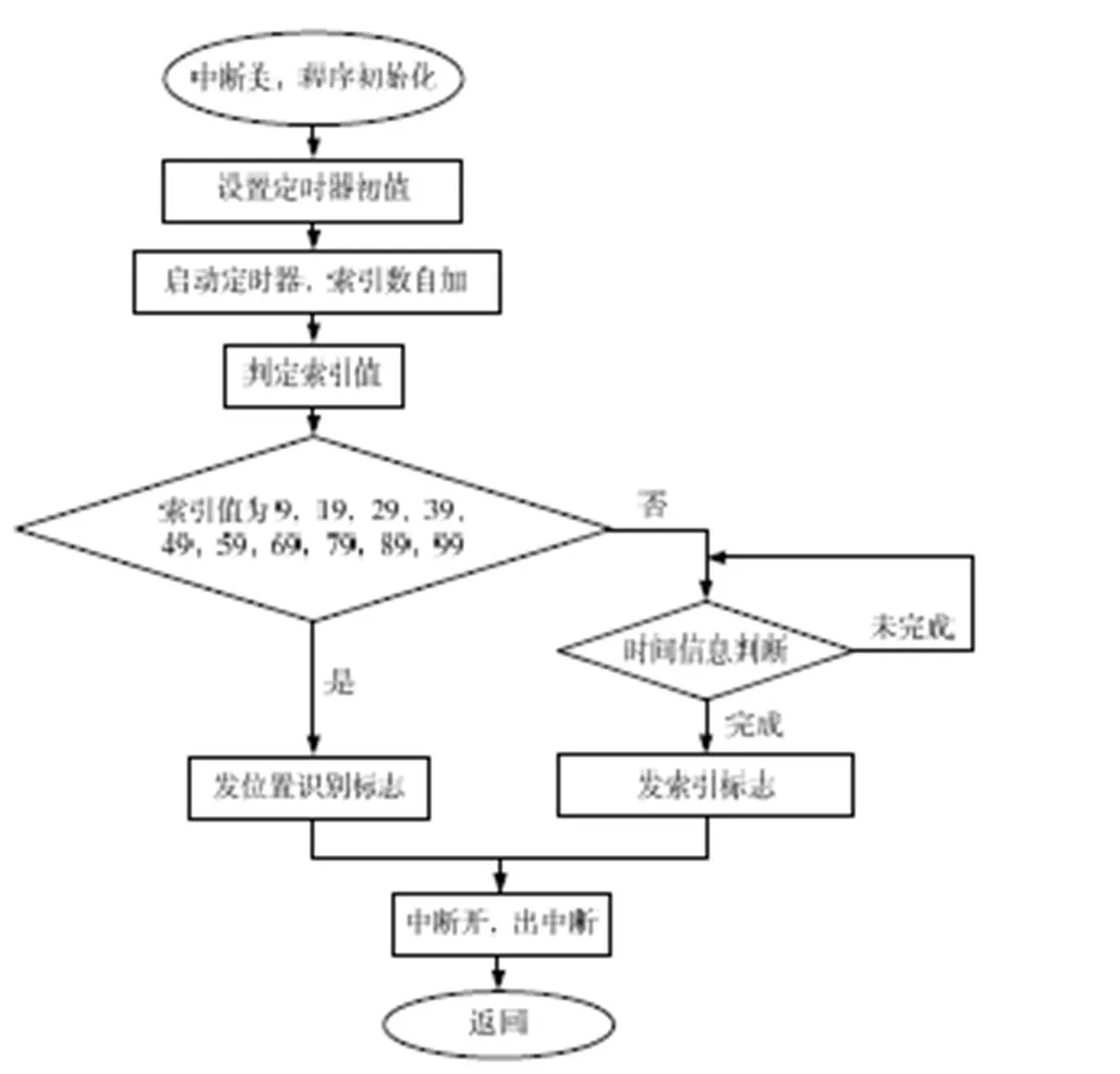

4.3 100 PPS中断处理子程序

根据B码信号的码元可以和100 PPS信号正好对应的关系,使用同步后的100 PPS信号为中断信号,完成IRIG-B码的直流码编码。定时器启动后完成位置识别标志的发送,每响应1次100 PPS中断,索引计数就加1,同时进行判断,当索引计数为9、19、29、39、49、59、69、79、89、99时,即每计数10次发送1个位置识别标志。当索引计数不是位置识别标识时,则对其时间信息进行判断,并根据判定结果控制逻辑门电路发送符合IRIG-B编码格式的脉冲信号,如果需要特殊控制信息,就在相应的位置加入相应的特殊控制码,输出相应的脉冲信号,完成IRIG-B(DC)码的编码。

100 PPS中断子程序控制流程如图8所示。

图8 B码信号产生器100 PPS中断处理流程图

5 结语

采用组合ARM+FPGA来完成的IRIG-B码信号产生器的设计,相比传统的设计,降低了设计难度,功耗更低,控制方便,性能稳定,应用更加广泛。在实际测试中,授时模块采用北斗导航接收机作为输入,直流码的同步精度可达50 ns,交流码同步精度可达100 ns。

随着新的高精度授时手段不断提高,便携式时统设备可以满足大部分测控现场的精度要求,可以为高速移动测量等场合提供完善的解决方案。嵌入式技术的应用和大规模集成电路的研究不仅可以提高IRIG-B码产生器的精度和可靠性,还可以不断开发其更为强大的功能,比如对现场信息处理能力和信息传递能力地不断提高。相信随着技术的不断进步,作为时间统一设备的重要组成部分的B码信号发生器将会具有微功耗、高度集成、高稳定度、智能化等特点。

[1] 童宝润. 时间统一系统[M]. 北京: 国防工业出版社, 2003.

[2] 杨蕾, 胡永辉. 用CPLD实现的靶场时间码产生器[J]. 电子测量与仪器学报, 2004(增刊): 1186-1192.

[3] STMicroelectronics. STM32F103VBT6 Datasheet[K]. 2009.

[4] Altera Corporation. CycloneⅢDevice Handbook[K]. 2008.

[5] TI Corporation. SN54128/SN74128 Device Datasheet[K]. 2007.

[6] TI Corporation. AM26C31 Device Datasheet[K]. 2008 .

[7] TI Corporation. DAC8311/DAC8411 Device Datasheet[K]. 2007.

[8] 庞吉耀. 基于FPGA的IRIG2B编码器实现[J]. 现代电子技术, 2009, 24(311): 113-117.

An IRIG-B code generator based on ARM and FPGA

GAO Lin1,2,3, HU Yong-hui1,2, HOU Lei1,2

(1. National Time Service Centre, Chinese Academy of Sciences, Xi′an 710600, China;2. Key Laboratory of Precision Navigation and Timing Technology, National Time Service Center,Chinese Academy of Sciences, Xi′an 710600, China;3. Graduate University of Chinese Academy of Sciences, Beijing 100039, China)

In this design, an ARM chip is used as the master control chip, while an FPGA chip is used as the main functional chip, and they can be programmed by using C programming language and Verilog hardware description language respectively. The IRIG-B code signal is generated and controlled by the software, and then the frequency demultiplication 1PPS signal and the external standard 1PPS signal are used to ensure the synchronization of time scale signal. Afterwards, the digital look-up table which is based on the ROM in FPGA is used to realize the digital modulation of AC code. The whole design is easy to be realized and applied.

IRIG-B code; ARM chip; FPGA; Digital modulation

TN76

A

1674-0637(2012)04-0218-10

2012-02-08

中国科学院“西部之光”人才培养计划重点资助项目(Y001YR1601)

高林,男,硕士研究生,主要从事时间统一系统技术研究。