基于E1接口的时间同步系统关键模块设计与仿真

闫辉,胡永辉,侯雷

基于E1接口的时间同步系统关键模块设计与仿真

闫辉1,2,3,胡永辉1,2,侯雷1,2

(1. 中国科学院国家授时中心,西安 710600;2. 中国科学院精密导航定位定时技术重点实验室,西安 710600;3. 中国科学院研究生院,北京 100039)

针对E1线路延迟稳定的优点,给出了溯源到GPS系统时间的时间保持模块,提出时间信息组合以适应E1线路不成帧的传输方式,采用HDB3码作为E1线路传输码型,利用FPGA芯片EP2C8T144I8进行开发,设计了基于E1接口的时间同步系统关键模块,并对各关键模块进行仿真,结果表明各模块设计均满足时间同步系统的要求。

时间同步;E1接口;HDB3码;现场可编程门阵列

0 引言

随着通信技术的飞速发展,时间标准及时间同步技术在通信网中的应用越来越广泛,但由于各种网元设备的内部时钟一般没有内在联系,且模块晶振精度较低,网元守时能力较差,现代通信领域的传统业务和新业务、运营商之间的互联互通和网间结算以及通信业务所涉及的网络安全、认证、计费等都需要一个共同的时间标准,准确、稳定的时间同步可以保证整个系统工作步调一致,高效地实现其所具有的全部功能[1]。而E1线路最大的优点就是延迟稳定,可以在一定程度上保证时间同步的精度。E1是国际电联电信标准化部门(ITU-T)制定并由欧洲邮政与电信协会(CEPT)命名的数字传输系统一次群(PCM30)标准,E1接口的物理及电特性符合国际电报电话咨询委员会(CCITT)的G.703标准,我国也采用E1标准作为脉冲编码调制(PCM)系统和窄带综合业务数字网(N-ISDN)的基群[2]。目前,E1接口在分组网、帧中继网、全球移动通讯系统(GSM)移动基站及军事通信中都得到了广泛的应用,用来传送语音、数据、图像等信号。兼顾应用的广泛性和稳定性,本文提出了一种基于E1接口的时间同步系统。文中介绍了以FPGA(现场可编程门阵列)为主要芯片,利用E1线路传输时间同步信息,完成时间同步的系统设计,并且给出了相关部分的设计和仿真结果。

1 系统设计

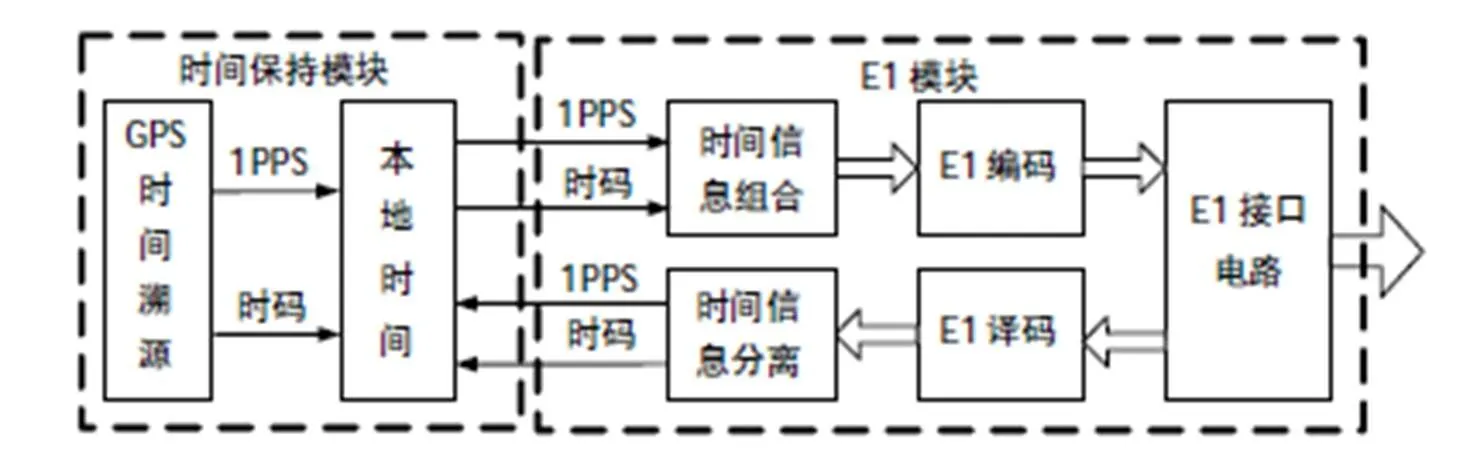

本系统通过接收外部GPS时间信息来校正本地时间,从而达到系统时间与GPS时间同步的目的。整个系统可以分为2个部分:时间保持部分和E1模块部分,系统组成框图如图1所示。时间保持部分的主要功能是本地时间保持和通过外界时间源对本地时间进行校正;E1模块部分的主要功能是通过E1接口发送时间同步信息,或接收外部同步信息用以校正本地时间。

图1 系统设计框图

2 时间保持模块

时间保持模块的主要功能就是实现本地时间保持和GPS时间溯源。本地时间保持模块是在系统自带晶振的驱动下工作的本地时间;GPS时间溯源是通过接收GPS时码信息和标准秒脉冲信号(1PPS)来完成对本地时间的校正。时码信息采用与串口通信类似的串行传输方式,其波特率为9 600 bit/s,数据位为8位。GPS 1PPS信号脉宽与本地晶振脉宽不同,为了之后的操作,需要将GPS 1PPS信号进行整形,使二者的脉宽一致。实现方法是将GPS 1PPS信号通过D触发器延迟,而后与自身相与。

在得到GPS时码信息和脉宽整形后的GPS 1PPS信号后,首先将本地时间重置为GPS系统时间,由于时码信息比GPS的1PPS信号晚,所以重设时间后需要等待下一个1PPS信号才能触发计时,并且重置的GPS系统时间需要多加1 s。GPS 1PPS信号不但触发计时,而且还会启动本地秒脉冲信号产生,保证GPS溯源完成后,完成本地秒脉冲信号的同步。

3 E1模块

E1线路数据传输速率为2.048 Mbit/s,可分为32个时隙,有成帧、成复帧和不成帧3种传输方式[3]。

本设计中采用不成帧的传输方式(此传输方式中,所有32个时隙均用于传输有效数据),将整个2 M线路作为数据传输链路,没有数据帧结构,传输速率为2.048 Mbit/s,传输码形式为HDB3码,传输时码信息和1PPS信号。首先将1PPS信号转换成同步头信息,将其与时码信息进行组合,然后经过HDB3编码,最后通过外围接口电路传输出去。

3.1 时间信息的组合和分离

时间信息包括本地时码信息和1PPS信号。本地时码信息可以从本地直接获取,经过HDB3编码就可以进行传输,而1PPS信号是一种时刻信号,不仅需要编码还要考虑时刻的问题。另外,由于信号传输方式是不成帧方式,所以传输数据没有帧头,接收端无法找到数据接收起始点,从而无法完成有效数据的提取。

考虑到1PPS信号的上升沿时刻和时码信息滞后1PPS信号的特点,可以将1PPS信号作为传输信号的帧头,随后传输时码信息,这样组合后,不仅可以标识1PPS信号的时刻,还可以保证有效数据的提取。

1PPS信号可以看作是连“1”数据,若以连“1”为帧头,在数据传输中可能会出现帧头误判;再者,1PPS信号就是要体现数据帧头的位置,而内容并不重要,所以在此以巴克码代表1PPS信号作为帧头。

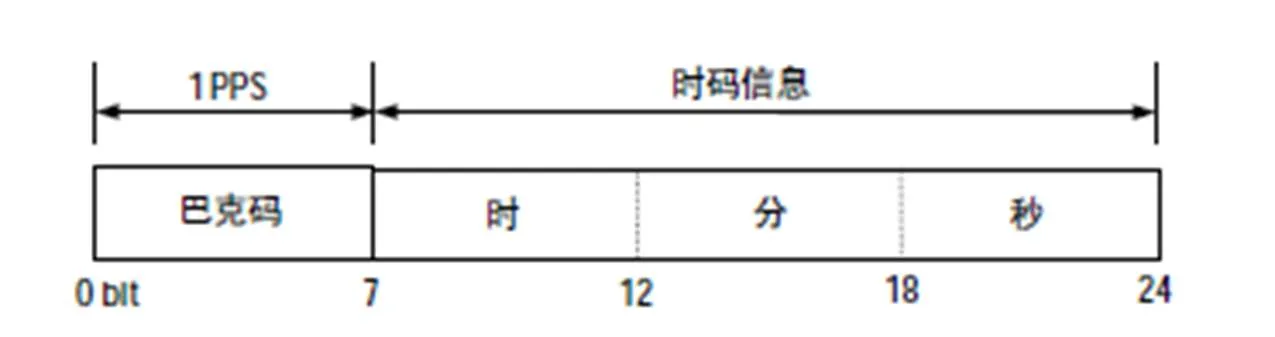

巴克码主要用于通信系统中的帧同步,是一种具有特殊规律的二进制码组,是一种非周期序列,其特点是具有尖锐的自相关函数,与随机数字信息相区别,易于识别。在本设计中采用7位巴克码“1110010”作为帧头,用来代表1PPS信号,其后数据为含有时分秒信息的时码信息,共有17位数据,如图2所示。

图2 1PPS信号与时码信息组合

由于时码数据的位数是固定的,去除7位帧头即可得到时码数据,所以可以不要帧尾,如果有需要也可以加上商定的帧尾或CRC校验位。在接收端,接收信号经过HDB3译码后,得到二元码,当检测到帧头的上升沿便产生一脉冲信号,即1PPS信号,然后将接收到的数据去除帧头,完成1PPS信号与时码信息的分离,得到时码信息。

3.2 E1编码

E1编码采用三阶高密度双极性码,即HDB3码。HDB3码是一种双极性码,其基带信号无直流分量,而且克服了AMI码连“0”的缺点,可以提取时钟信号[4]。其编码原理为:

1)将信息代码转变成极性交替的AMI码;

2)判断AMI码中连0的个数,如果连0数大于3个,则把第4个0变成V符号,V的极性与前一个非0符号(+1或-1)的极性相同;

3)为了不破坏极性交替,V符号也要极性交替,但是当相邻V符号之间有偶数个非0符号时,会出现V符号与前一个非0符号极性不同,此时再将该连0的第1个0变换成+B或-B,B符号极性与前一个非0符号相反,并让后面的非0符号极性从V符号开始再交替变化;

4)最后将非0符号均变成1符号,极性不变。

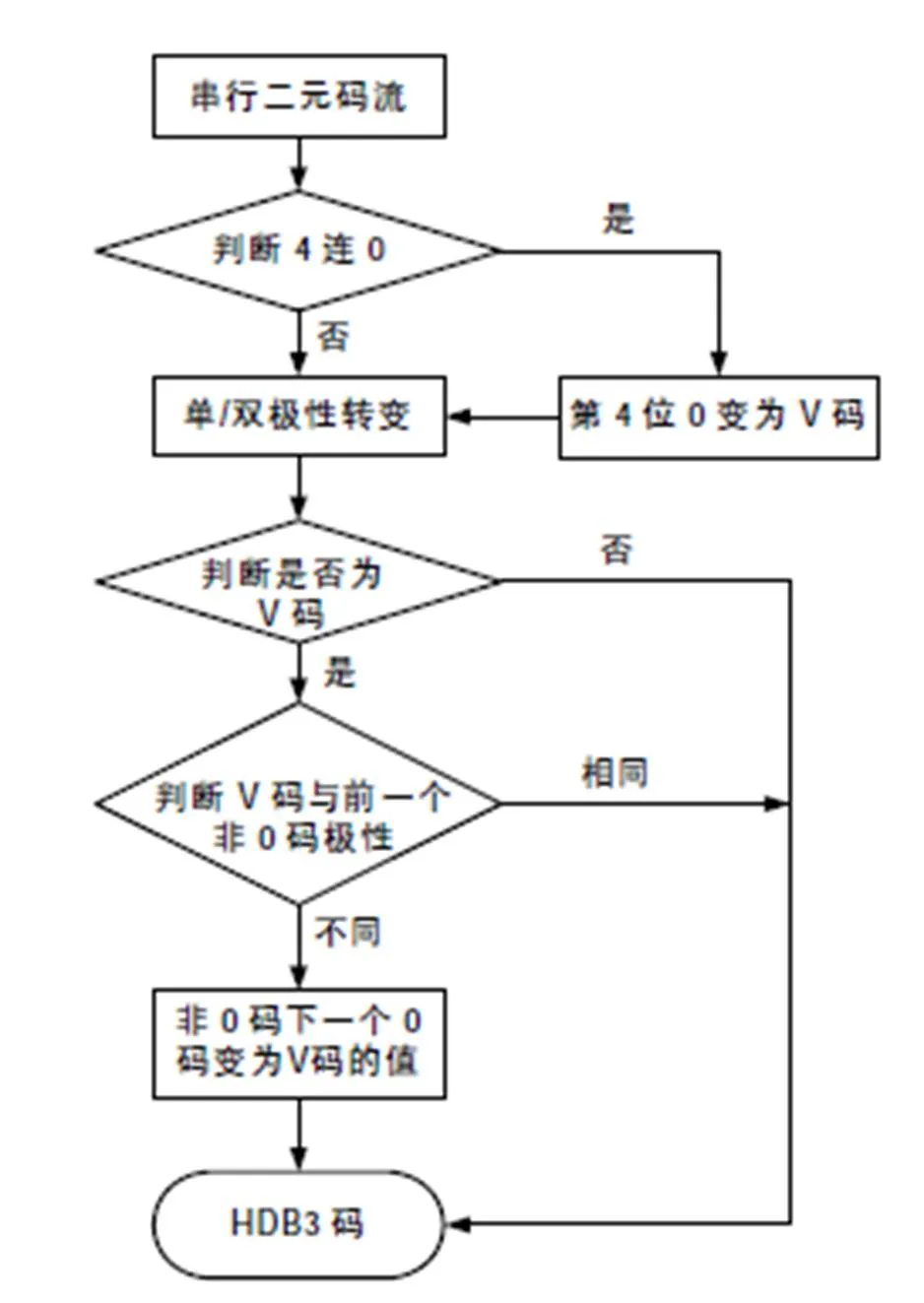

本设计中的HDB3编码是在FPGA上实现的,但是因为FPGA不能产生负电压,所以需要2路信号,一路代表正极性,另一路代表负极性[5-6]。用Verilog编程语言实现编码,编程思想如下:

第1步,改变极性,产生极性交替的信号,编码中用“10”表示“+1”,“01”表示“-1”,“00”表示“0”;

第2步,加V并完成极性交替。根据编码规则,判断4个连0,当出现4个连0,将第4个0变为V符号,同时V符号极性也要交替,最后再将V符号变成1符号,极性不变。所以可以直接将V符号变成1符号,并且极性交替,即“10”或“01”,同时输出1个加V符号的标志信号,以标定加V符号的位置,为接下来的加B操作做基础;

第3步,加B符号。根据编码规则,利用第2步的加V标志可以得到V符号位置,将其值与前4个非零值相比,若相同,说明极性相同,不作改变;若不同,则说明极性相反,将前3个0符号的第1个变为B符号,极性与V符号相同,由于最后还要将B符号变为同极性的1符号,所以可以直接变为V位置的值,即“10”或“01”,分别代表“+1”或“-1”。

HDB3码编码的程序流程如图3所示。在第3步中,由于要参考前4个值并且可能要改变前面的数值,所以在FPGA代码编写中需要4个寄存器,分别延时1,2,3和4个周期,加B符号的是在第3寄存器。

图3 HDB3编码程序流程图

3.3 E1译码

HDB3码的双极性需要2路表示,“10”和“01”分别代表“+1”和“-1”。根据编码规则,只有破坏点V脉冲与前一个非0符号极性相同,所以首先可以从信码中找到V码,那么V码和其前3个符号必然是取代码,在译码时,只需要把V码以及其前3个取代码变为0码即可,只要找到V码,不管V前面是2个0码,还是3个0码,一律将取代码置零,完成V码和B码的转变,最后完成双/单极性的转换,进而得到原二元码。

在代码编写中,首先判断V码,由于要判断前4个符号极性,所以需要4个寄存器,分别是对输入信号进行1,2,3和4个周期延迟的信号,检测V码有2种情况:一种是“1000V”,另一种是“B00V”,判断2种情况的非0符号极性是否相同,若不同,不作改变,若相同,则将全部非0符号变为0符号,最后将正极性和负极性2条信号相加,得到译码后的二元码信号。译码的程序流程如图4所示。

3.4 E1接口电路

E1接口电路是E1接口与FPGA之间的硬件电路部分,主要功能是电平转换、网络隔离、滤波和整形,完成FPGA与E1接口之间信号电平和极性的转换。

4 仿真结果及分析

在Quartus II 9.0集成环境下,结合前面系统及模块设计,给出了相关仿真结果。

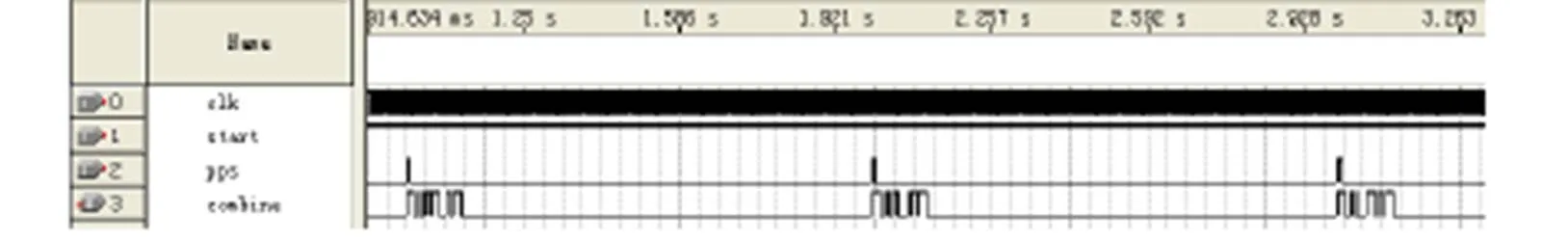

图5是组合后的时间信息仿真图,“pps”信号是1PPS信号,每1秒发1次,“combine”信号是1PPS信号和时码信息组合之后的信号。

图5 组合后的信息仿真图

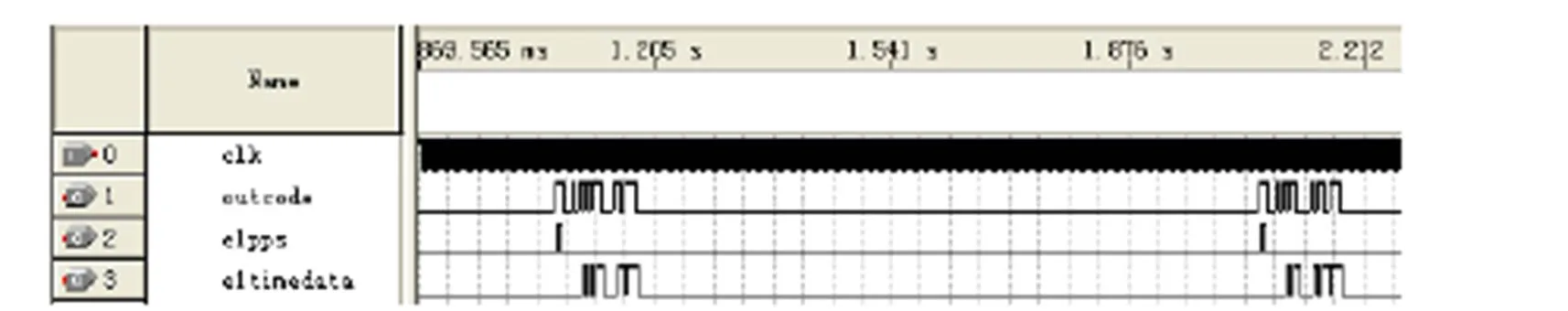

图6是组合信号的细节仿真图,从图6中可以看到,组合信号前7位是巴克码“1110010”,随后是17位的时码信息,代表时分秒的信息。图7是接收端将接收的信号分离为1PPS和时码信息的仿真图。图7中,“e1pps”信号是分离后的1PPS信号,“e1timedata”信号是分离后的时码信息。

图7 信息分离仿真图

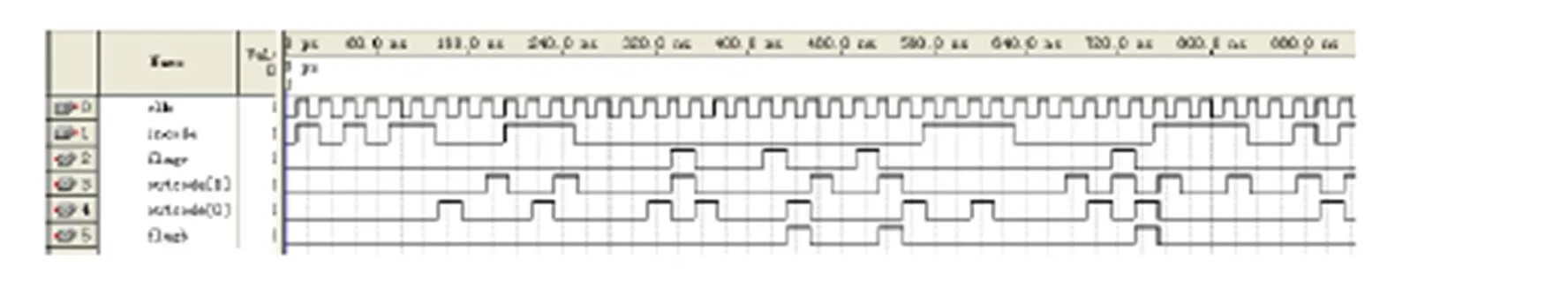

图8是HDB3编码的仿真图。图8中“incode”是输入的二元码序列,“outcode[1]”是HDB3码的负极性信号,“outcode[0]”是HDB3码的正极性信号,“flagv”和“flagb”分别是加V符号和加B符号的位置。

图8 HDB3编码仿真图

5 结语

设计了基于E1线路进行时间同步的系统,各模块均在FPGA上进行仿真,应用Verilog硬件编程语言进行开发,开发周期短,设计灵活,可移植性强,可以通过逻辑仿真验证设计的合理性和正确性。本设备还可以扩展为成帧的传输形式,利用时分复用,可以进行多路时间同步操作,也可以添加其他接口线路,进行相关转换,增强其扩展性。同时,还可以通过对开发程序和同步方法的优化,提高同步的精度,满足更高的要求。

[1] 中国人民解放军总装备部军事训练教材编辑工作委员会. 时间统一技术[M]. 北京: 国防工业出版社, 2004.

[2] 邱志模, 王华. 基于FPGA的以太网与E1协议转换器的实现[J]. 军民两用技术与产品, 2006, (10): 44-45.

[3] ITU-7 G.703 CCITT, 系列数字接口的物理电特性[S].

[4] 樊昌信, 曹丽娜. 通信原理[M]. 北京: 国防工业出版社, 2007.

[5] 汉泽西, 孙燕妮. 基于FPGA的HDB3编译码[J]. 电子科技, 2007(3): 66-69.

[6] 朱勤为, 唐宁, 赵名剑. 利用FPGA实现HDB3编解码功能[J]. 电子设计工程, 2009, (12): 76-79.

Design and simulation of key modules of time synchronous system based on E1 interface

YAN Hui1, 2, 3, HU Yong-hui1, 2, HOU Lei1, 2

(1. National Time Service Center, Chinese Academy of Sciences, Xi′an 710600, China;2. Key Laboratory for Precision Navigation and Timing Technology, National Time Service Center,Chinese Academy of Sciences, Xi′an 710600, China;3. Graduate University of Chinese Academy of Sciences, Beijing 100039, China)

According to the advantage of the stable transfer delay of E1 interface, the time keeping module which can trace to the time of GPS System is proposed. The time information combination is given in order to adapt to the no framed transfer method for E1 interface. By using the HDB3 code as the transmission code and adopting the EP2C8T144I8 FPGA chip, the key time synchronous system module of E1 interface is designed. The simulations of the key modules are conducted and the results indicate that all the key modules meet the requirements of the time synchronization system.

time synchronization; E1 interface; HDB3 code; FPGA

TN919;P127

A

1674-0637(2012)04-0212-06

2012-03-15

中国科学院“西部之光”人才培养计划重点资助项目(Y001YR1601)

闫辉,男,硕士研究生,主要从事时间统一系统技术研究。