基于FPGA的时钟数据恢复电路的研究和设计

任全会 赵雨虹

(郑州铁路职业技术学院,河南 郑州 450052)

一、引言

时钟数据恢复电路(CDR)是高速收发器的核心模块,在光传输系统、背板连接以及IO接口等领域应用非常广泛。CDR的作用是根据接收数据本身的特点,找到采样数据的最佳时钟相位,使数据恢复稳定可靠。目前在通信系统中大量使用专用的CDR芯片大多采用PLL技术,成本较高。同时,FPGA由于其功能的灵活性、相对低廉的成本和较短的设计周期,已经大量在通信设备中作为业务核心芯片,完成上下业务、电路交换以及开销处理等功能。本文提出一种基于FPGA的过采样时钟恢复方法,对全数字CDR设计加以改进,在Altera公司Cyclone II芯片上实现数据的恢复。

二、过采样法时钟数据恢复原理

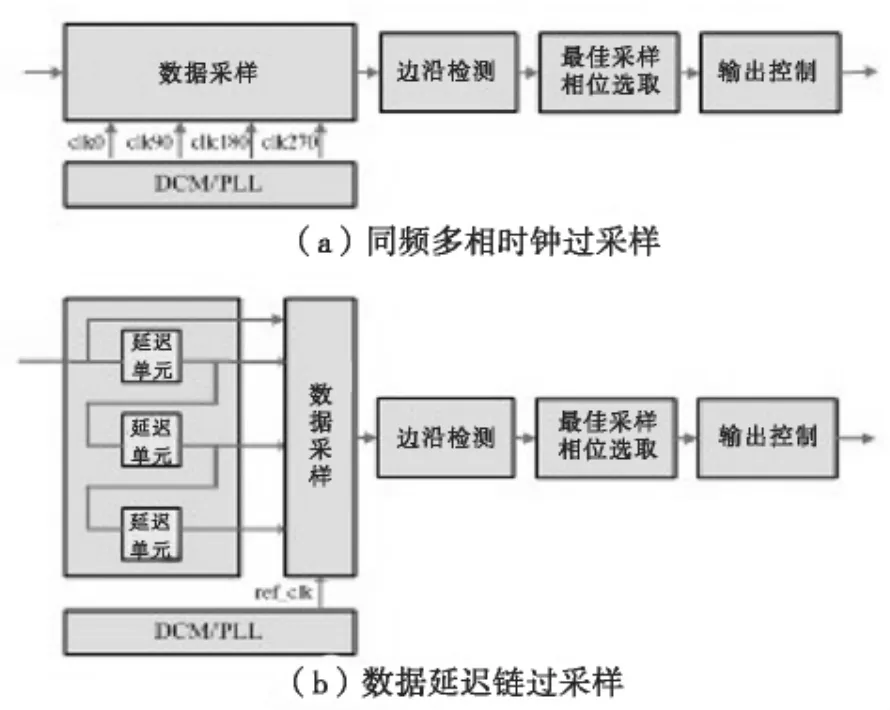

前基于FPGA的全数字CDR多采用数字化过采样法,其两种具体的实现方式为同频多相时钟采样和数据延迟链采样,如图1所示。其基本原理是采用本地N*f的高速时钟,对信号作N倍过采样,通过对采样数据的分析判断出数据跳变沿的位置,实时寻找并切换到最佳采样时钟,从而恢复出数据与线路时钟。由于是一种相位前馈技术,过采样法具有较大的频率捕捉范围和较快的捕捉速度。

受到FPGA工作频率限制,对高速数据直接采用频率为N*f的时钟采样困难很大,因此两种方法都是模拟N*f采样时钟在一个数据时钟周期内获取N个均匀采样值。为保证时钟恢复质量,N通长采用6-8。

图1 同频多时钟过采样与数据延迟链过采样时钟数据恢复原理

三、模块电路设计

1.过采样模块

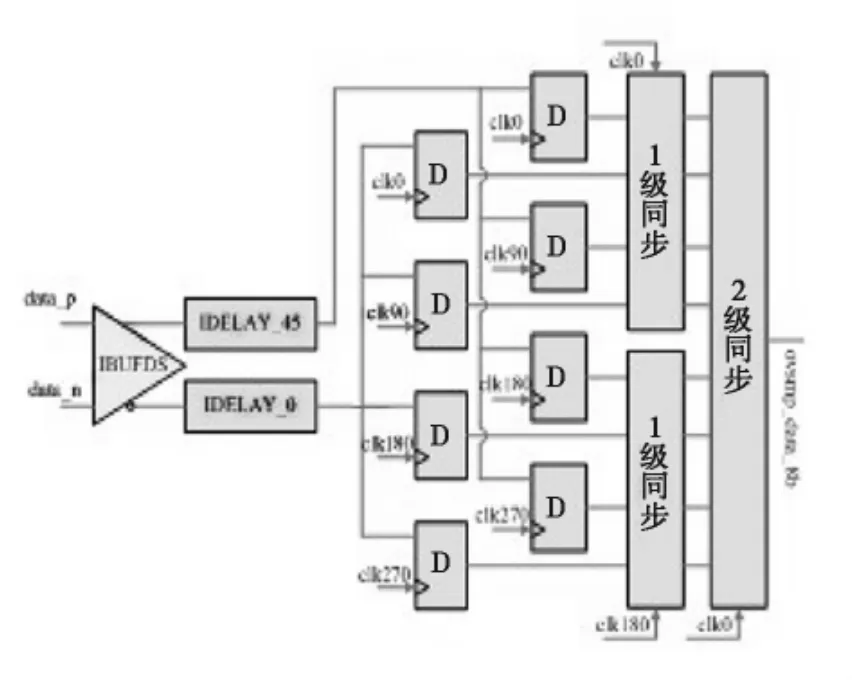

过采样模块的设计目标是尽可能保证高速数据采样的相位精确,因此要求从数据输入管脚到8个第一级采样触发器具有相同的数据时延。本设计中采用了如图2所示的电路结构。

与以往设计不同的是,在接收数据通过差分数据缓冲器后,在过采样模块中采用FPGA内置的IDELAY模块将接收数据及其反相信号分别延迟相当于45°和0°相位的时间,再送给由PLL/DCM产生的相位分别为 0°,90°,180°

图2 过采样模块原理

和270°的4路155.52MHz本地参考时钟采样,获得8倍过采样数据。此后,采用两级触发器将采样数据同步到相位0°的本地参考时钟域,以方便后级模块检测判决,同时避免了异步采样的亚稳态现象。最佳采样相位判决模块和数据恢复模块也工作在此时钟域。

2.最佳采样相位判决

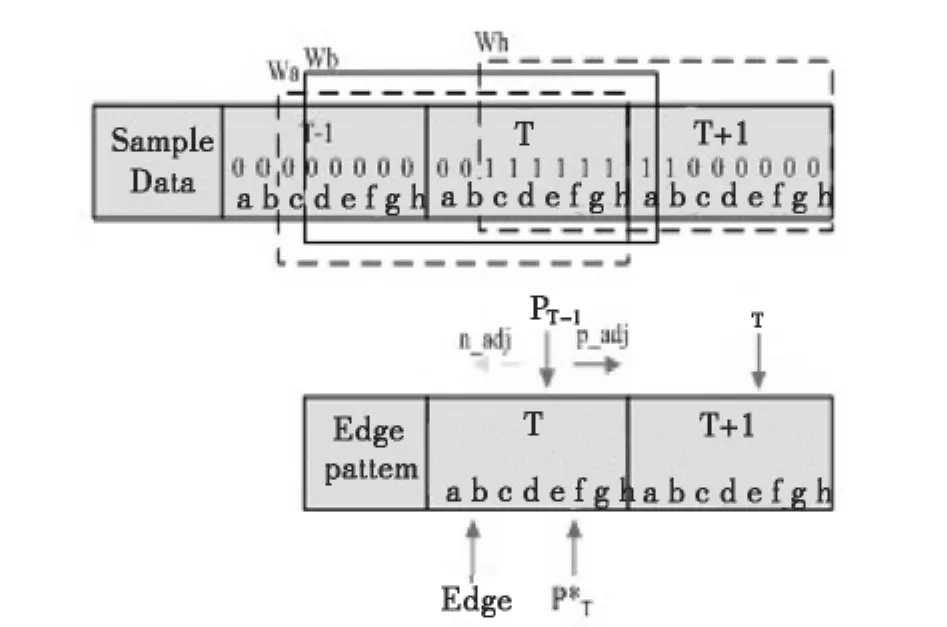

最佳采样相位判决模块的功能是通过检测采样数据中跳变沿的位置,判决当前数据最佳采样相位,原理图如图3所示。

图3 最佳采样相位判断原理

边沿检测模块将来自过采样模块的采样数据流缓存,在采样周期T-1到T+1采样到的24个比特中,通过在滑动窗口中的数据匹配(如000111或11110000),寻找采样周期T内的发生的边沿跳变,并根据跳变位置生成8位跳变沿图样。滑动窗口起到了低通滤波器的作用,能够避免了数据毛刺对判决的干扰。窗口宽度越大,抑制毛刺的性能越好,但是对于一个8倍过采样系统,线路时钟周期与采样时钟应满足,即每个接收数据周期最少有7个采样点,因此最大窗口宽度为14。对比将相邻采样周期采样数据异或来寻找数据边沿的方法,滑动窗口设计使用较多的逻辑资源换取更高的可靠性。

本设计中,在每个采样周期T内,首先比较上一采样周期的实际采样相位PT-1和根据当前采样周期内跳变沿位置推算得到的最佳采样相位P*T,根据二者的相对关系产生正负调整指示。之后在PT-1的基础上,根据正负调整指示向前或向后调整一个相位作为判决结果。这样的设计能够在保证了较好的频率相位跟随性能的同时,避免了最佳采样相位的剧烈抖动。需要注意的是,当PT-1=N-1且正调整有效时,则采样周期T内没有有效采样数据;而当PT-1=0且负调整有效时,则采样周期T内的第0和第N-1相位均有效。因此每个采样周期内有效的采样点个数可能为0,1或2个,该模块输出2比特的数据和一个2比特的数据有效标识信号。

3.数据恢复

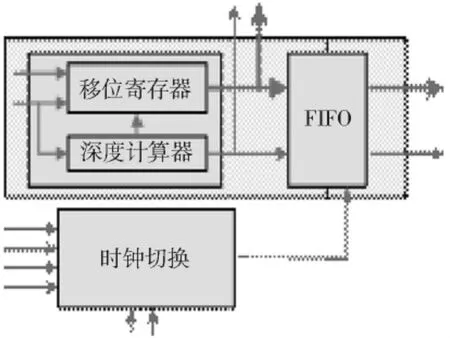

数据恢复模块的功能是根据最佳采样相位判决结果,恢复线路时钟并提取最佳采样数据,结构如图4所示。

图4 恢复线路时钟结构图

时钟恢复子模块通过在多个相位的本地采样时钟间切换,恢复出线路时钟。由于本设计中仅使用了4个相位的本地时钟,因此当最佳采样时刻分别为0~7时,对应的采样时钟相位分别为180°,180°,270°,270°,0°,0°,90°,90°,磁盘阵列数据恢复。该模块功能实现的关键在于保证不同相位时钟信号经过选择电路的路径延迟尽量相同,从而保证各时钟经过该模块后相对相位关系不改变。在本设计中,使用FPGA一个LUT6实现4选1选择器,选择器输入到输出的延迟小于0.1ns,完全满足设计需要。

数据缓冲器实现恢复数据的缓冲和串并转换。来自最佳采样相位判决模块的位宽为2比特的数据按时间顺序被送入一个移位寄存器缓冲,同时对缓冲深度计数。当缓冲深度大于等于8时,将缓冲器内最早的8比特数据送出,同时产生数据有效标志。在某些仅关心数据恢复,而不需要恢复线路时钟的系统中,该模块的输出即可作为CDR的模块的数据恢复结果。

异步FIFO用于已恢复数据的跨时钟域转换,写侧和读侧分别工作在本地参考时钟域和恢复时钟域,避免以恢复时钟直接采样接受数据带来的附加抖动。

三、仿真与实验结果

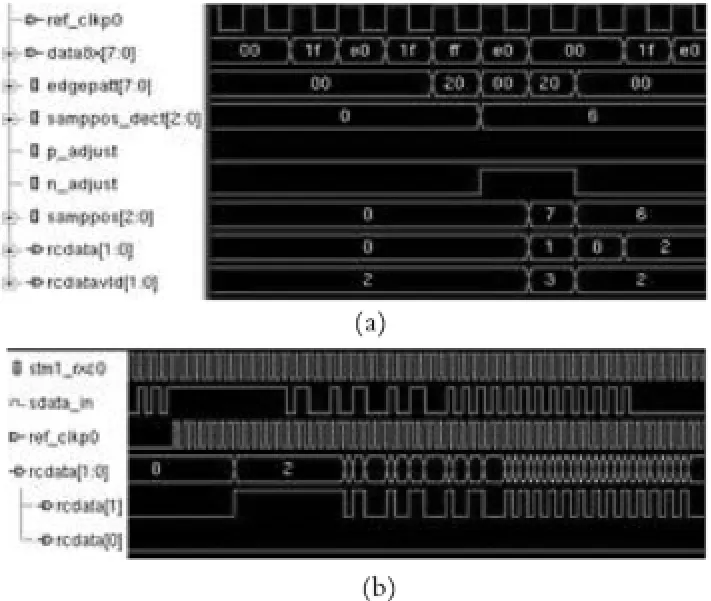

本设计使用verilog语言编程,在Altera公司CycloneII芯片上实现。首先使用Synopsys VCS对代码时序仿真,当输入数据速率为155.52Mb/s,本地参考时钟频率155.50MHz时,关键信号波形如图5(a)所示,而在仿真波形(b)中可以看到,该电路捕获时间(含数据延迟)仅为56ns,约9个时钟周期。实际上,当提高输入数据速率到311.04Mb/s,本地参考时钟频率311MHz,布线后仿真结果显示该电路仍然能够正确恢复数据。

图5 数据恢复仿真波形

实验采用SDH分析仪Agilent OmniBER OTN J7231B测试单板时钟数据恢复性能。由于本设计没有恢复线路时钟,仅对CDR的输入抖动容限进行了测试。图6为调制频率10Hz~1.3MHz范围内,在155.52MHz光口的测得的抖动容限。

图6 STM-1光口实测抖动容限

本文提出了一种利用FPGA的可编程输入延时单元构造一级延迟链,使用N/2个同频多相时钟实现N倍过采样高速时钟数据恢复电路设计,采用改进的边沿检测和最佳相位判决算法,提高了数据恢复可靠性。如果配合光接口时钟保护切换芯片(如ACS8515),则能够克服恢复时钟抖动较大的不足,而同时获得快速捕捉性能、较高的抖动容限和恢复时钟质量,可作为光通信设。

[1]江黎,钟洪声.一种全数字时钟数字恢复电路的设计与实现[J].通信技术,2008(11):121-123.

[2]尹晶,曾烈光.一种快速同步的时钟数据恢复电路的设计实现[J].光通信技术,2007(1):52-54.

[3]ITU-T.The control of jitter and wander within digital networks which are based on thesynchronous digital hierarchy(SDH).