ADS-B系统应答的一种纠错算法设计与实现

周建红 刘晓斌 张 超

(电子科技大学 成都 611731)

1 引言

我国民航传统的空管系统主要是基于一次雷达系统和二次监视雷达系统的雷达监管系统。雷达系统造价昂贵,覆盖面积有限,功能有限。而基于模式S的广播式自动相关监视系统(ADS-B)是ICAO在新航行系统中所推荐的一种新兴的航行监视技术,是空管监视领域的一项革命性技术[1]。ADS-B系统不仅成功应用于无雷达区域的远程航空器运行监视,而且与传统雷达监视技术相比,ADS-B技术具有使用成本低、精度误差小、监视能力强等明显优势,对于高密度飞行区域的空中交通服务有着广泛的应用前景[2,3,4]。

由于模式S应答信号由机载异频收发机经过脉冲位置编码发送,在高A/C应答fruit交叠的环境下,可能使模式S的ADS-B系统的应答信号被地面处理器接收后,会产生一些错误位,从而必须对ADS-B系统应答信号的每个比特位进行纠错处理。

2 ADS-B系统基带数字信号处理流程

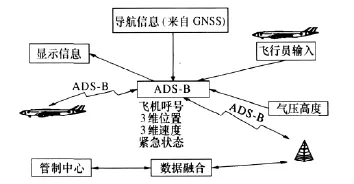

ADS-B是一种基于全球定位系统(GNSS)和利用空-地、空-空数据链来完成交通监视和信息传递的一种航行新技术系统。ADS-B使用机载导航系统得到飞机的精确位置和速度信息,利用机载电子设备向外周期性地广播飞机的呼号、位置、速度和其它一些参数信息。通过空地数据链,地面站接收这些信息并处理后,传给管制中心,实现地空监视;装有ADS-B设备的飞机也可以通过机载电子设备接收附近ADS-B飞机的广播信息,实现空空监视。ADS-B系统工作原理如图1所示。

图1 ADS-B系统工作原理示意图

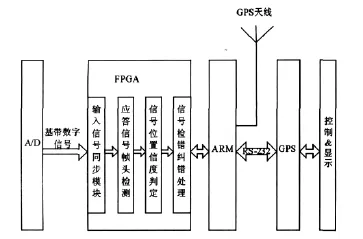

如图2所示:ADS-B系统基带数字信号处理可分为FPGA处理部分和ARM处理部分。

图2 ADS-B系统基带数字信号处理流程图

在基带数字信号处理前,信号经过A/D转换器,把模拟信号转化成数字信号,便于在FPGA中处理。

FPGA处理流程为:首先是检测ADS-B应答信号帧头,确定ADS-B信号的存在性,其次是ADS-B应答信号位置信度的判定与提取,最后是检测应答信号,如果检测出有错误的比特位,则纠正错误的比特位。

ARM处理流程:由于ADS-B系统具有消息交换的功能,不仅要处理发送自身飞行的各种信息数据,还要处理接收到的其它飞行器的ADS-B系统广播的数据,进行信息融合处理,同时上传到显示设备或其他功能设备,实现防撞灯方面的安全处理。这些功能的实现就需要ARM来处理。

3 循环冗余编码(CRC)的工作原理

循环冗余编码(CRC)是一种常用的冗余编码,是在二进制通信系统中常用的差错检测方法,它是通过在原始数据后加冗余校验码来检测差错,冗余位越多,检验出传输错误的机率越大。

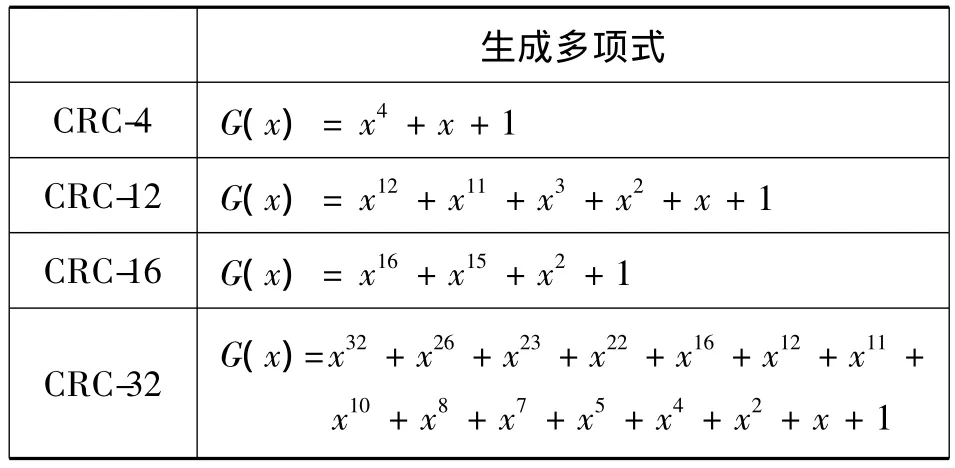

CRC校验的基本思想是利用线性编码理论。在发送端,根据要传送的k位二进制码序列,以一定的规则产生一个校验用的r位监督码(即CRC码),并附在信息位后面,构成一个新的共n=k+r位的二进制码序列,最后发送出去。这种编码又叫(n,k)码。对于一个给定的(n,k)码,可以证明存在一个最高次幂为r的多项式G(x)。根据G(x)可以生成k位信息的校验码,而G(x)叫做这个CRC码的生成多项式[5]。常见的生成多项式如表1所示。

校验码生成过程为:发送方与接收方事先约定一个生成多项式G(x),该多项式作为除数多项式。假设发送信息用信息多项式P(x)表示,将P(x)左移r位得到M(x),这样P(x)的右边就会空出r位,这就是校验码的位置。通过M(x)除以多项式G(x)得到的余数就是校验码R(x)。R(x)可表示为:

其中mod表示模二求余运算[6]。

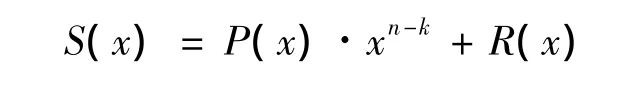

假设发送方发送码字为S(x),则有:

其中n和k分别是发送码字和消息对应的二进制序列的比特数,即发送码字S(x)由k位比特消息码与后面跟着n-k位校验码组成。在接收端,接收码字S'(x)同样被G(x)去除,得到R'(x):

检查R'(x)是否为一个常数(通常为0),如果R'(x)为一个常数,就认为传输正确,否则就认为传输中发生错误。

表1 常见的生成多项式

4 纠错算法设计

4.1 ADS-B应答信号编码

基于模式S的ADS-B应答信号采用CRC编码方式,每一个ADS-B应答信号(56位/112位),都由数据位(32位/88位)和校验码(24位)组合生成。基于模式S的ADS-B系统下行数据链采用一种改进的(缩短的)使用下列生成多项式的(112,88)(即n=112,k=88)CRC 编码。

ADS-B接收机系统在收到应答信号后解出地址和校验位以判断数据和地址是否被正确传输,如果发生错误,然后采用一定的纠错技术对应答信号进行修正。

4.2 置信度判定

基于模式S的ADS-B系统下行数据链信号是脉冲位置调制的,即对于任一比特位,脉冲能量出现在前0.5μs区间内表示为”1”,出现在后0.5μs区间内表示为”0”。因此,我们可以通过比较ADS-B应答信号任一比特位的前0.5μs区间内信号强度是否大于它的第二个0.5μs区间内信号强度,若大于则判为二进制1,否则判为二进制0。目前有多种方法可以实现这种判定,为了提高置信度判定的准确性,这里采用基线多样点算法[7]。基线多样点算法充分利用了每个比特位的所有10个采样值。最高的分数决定比特位的值,如果相等则为比特”0”。如果差值大于等于3[7]则为高置信度,否则为低置信度。这样我们就得到了应答信号的码字数组和每个码字对应的置信度信息[8]。

4.3 ADS-B应答信号纠错

由于模式S使用了飞机地址点名的询问机制,要求信息在单次传输中有效地实现,这就要求基于模式S的 ADS-B系统具有纠错功能。因此,在ADS-B系统中,完成前面的数据帧头检测、数据位置信度判定后,还需对应答信号进行有效的纠错。

目前常见的纠错技术[9]有三种:第一个是“Conservative”技术,它是基于现有的滑动窗技术,只能对24比特窗内里的比特位进行纠错,这个约束限制了它只能应用于只有一个较强的A/C fruit与之交迭的情况。第二个是“Whole Message”技术,它将整个A/C fruit对比特位和置信度判定的影响模型化;第三个是“Brute Force”技术,它是针对随机分布的不超过d-1(d为CRC码的汉明距离)比特的错误图样。

“Brute Force”技术纠错原理[7,9]:循环冗余校验码的不同比特位发生错误时,应该使余数不同,即每一个错误位置对应一个唯一的CRC校正子,并且对这些单个位校正子进行组合(异或)以后,得到那个组合的错误校正子。如果已经正确地完成置信度判定,那么应答信号所有可能的错误应该只出现在低置信度比特位上。于是尝试结合所有低置信度比特位对应的校正子,然后接收与错误校正子匹配的那一个组合(假设只有一个成功匹配,如果有两个或多个匹配,就丢弃该信号),最后把这个组合对应的那些低置信度比特位取反即完成纠错。

基于处理时间和未检错率考虑,“Brute Force”技术限定要处理的低置信度比特位数的最大值为d-1(d为CRC码的汉明距离)。如果应答信号里有n个低置信度比特位,则需要考虑的组合数为:

未检错率与情况的数量成正比,即也按n的指数增长。

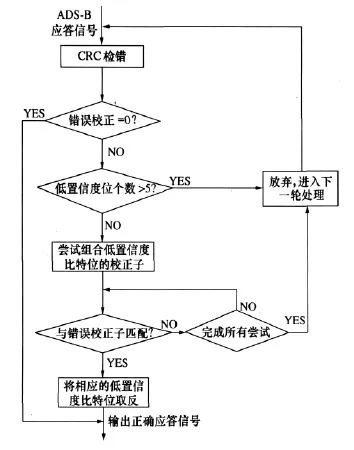

由于ADS-B应答信号采用(112,88)CRC编码,而(112,88)CRC码的汉明距离是6,这意味着如果应答信号错误比特位个数小于或等于5,那么就没有任何未检测到的错误。因此,本文在第三种技术的基础上提出了一种基于循环冗余编码(CRC)的纠错算法,其基本思想是:首先利用CRC进行检错,如果检出有错,然后采用“Brute Force”技术尝试所有低置信度比特位的单个位校正子的组合校验子(如果低置信度比特位个数超过5个,则直接丢弃该应答信号),把这些组合校验子与错误校正子相比对,相等时,则将产生该组合校正子对应的比特位取反即完成纠错,最后输出正确的ADS-B应答信号。基于此,纠错算法信号处理流程如图3所示。

图3 纠错算法信号处理流程图

5 FPGA实现

5.1 逻辑设计

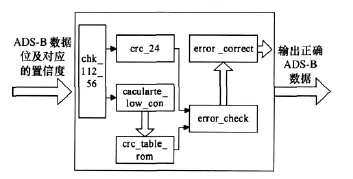

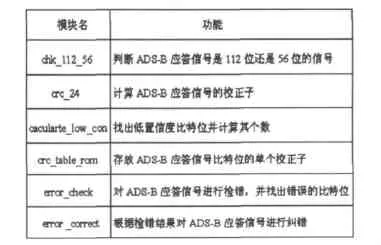

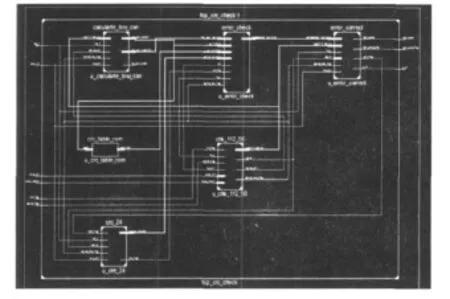

基于循环冗余编码(CRC)对ADS-B系统应答信号进行纠错处理。将112位或56位ADS-B应答信号经过某特定的生成多项式G(x),得到错误校正子R。当R为零时,表明应答信号正确,直接接收信号;当R不为零时,表明应答信号有错误,进而进行纠错处理。其FPGA逻辑设计方案如图4所示,各个模块的名称及功能如表2所示。

图4 纠错算法FPGA逻辑设计方案框图

表2 模块列表

5.2 仿真验证

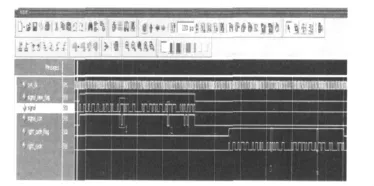

在完成算法设计后,为了验证方案的合理性,本文首先采用Verilog HDL语言描述纠错算法,然后联合Xilinx公司的ISE软件与Mentor公司的Modelsim软件对其进行了电路功能仿真实验。纠错算法的功能仿真结果如图5所示。仿真中只保留了关键信号,从图5中可知,纠错模块输入了有效的112位比特位信号(信号signal),且这112位中有4个比特位的置信度为低置信度(信号signal-con有4个低电平,当signal-con为低电平时,相应的比特位的置信度为低置信度,当signal-con为高电平时,相应比特位的置信度为高置信度)。经过纠错模块处理后,低置信度位对应的比特位都被取反,输出正确的112位比特位(信号right-code)。举例说明:经过前面的置信度提取模块处理后输出的比特位(图中数字标记1旁)为低置信度的比特位‘1’,但是经过纠错模块后(标记3旁的长方形)输出比特位‘0’。同理,数字标记2中的低置信度的比特位,经过纠错模块后同样被取反(图中数字标记4中对应的比特位),因此表明上述算法能够实现对ADS-B应答信号的纠错功能。图6为用ISE软件综合得到的算法整体设计的RTL级电路。

图5 纠错算法功能仿真图

图6 整体设计的RTL电路图

6 结束语

本文讨论了基于模式S的ADS-B系统基带数字信号处理中的纠错算法,并给出了实现该算法的电路方案。然后采用Verilog HDL语言完成了算法设计,通过电路仿真实验验证了该算法的可行性。实验结果表明此算法能够正确地检测出ADS-B应答信号在传输过程中出错的比特位,并纠正其错误,有效地保证了ADS-B应答信号传输的可靠性。

[1]顾春平.空中交通管制监视新技术简介[J].现代雷达,2010(9):1-5.

[2]吕小平.空中交通管理文集[M].北京:航天工业出版社,2009.

[3]张军.现代空中交通管理[M].北京:北京航空航天大学出版社,2005.

[4]张天平.ADS-B技术及其在空管中的发展与应用[J].电子产品世界,2009(6):34-35.

[5]云创工作室.Verilog HDL程序设计与实践[M].北京:人民邮电出版社,2009.

[6]CHEN Shi-yi.Error Correcting Cyclic Redundancy Checks Based on Confidence Declaration[C].International Conference on ITS Telecommunication Proceedings.2006:511-512.

[7]ADS-B 1090 MOPS,Revision A,Appendix I Extended Squitter Enhanced Reception Techniques[S].RTAC,2003.

[8]Michael C.Stevens.Secondary Surveillance Radar[M].Artech House Boston and London,1998.

[9]DO-260A.Minimum Operational Performance Standards for 1090 MHz Extended Squitter Automatic Dependent Surveillance Broadcast(ADS-B).RTCA,2003.

[10]Verilog数字系统设计教程[M].北京:北京航空航天大学出版社,2005.