信号采集中峰值检测电路的设计与实现

郭宗平,王厚军,戴志坚

(电子科技大学自动化学院,四川 成都 611731)

0 引 言

峰值检测是示波器中数据采集方式之一(另外有取样方式和平均方式)[1],这种技术起源于存储深度不能满足捕获毛刺的需要[2]。取样方式是通过平均的时间间隔对信号进行取样来进行创建波形,正常取样方式时,要捕捉窄的毛刺,示波器必须以高的采样率才能捕捉到窄的毛刺,并且将全部采样数据全部存储起来。而当信号的频率比较低时,用示波器去观察信号需要将示波器时基档位调到等效采样率比较低的档位,而这时需要等效采样率很低,利用取样方式就不能捕捉到毛刺信号,利用峰值检测技术就可以解决这个问题。峰值检测不像正常取样那样给出一个详细的完整波形显示,而是以最高的采样率捕捉信号,简单的忽略某些采样,只记录发生在每个采样间隔期间内的最大和最小值,这样就不用增加存储存储深度还可以捕捉毛刺或偶发事件[3]。峰值检测模式下,即使使用的是等效采样率较低的时基档位,也能捕捉到可能出现的某些毛刺信号。峰值检测是数字示波器的重要技术指标之一,主要用来实现以下3个功能:(1)波形的毛刺捕捉;(2)包络的显示功能,峰值检测的方法对于捕捉调制信号(例如AM波形)是非常有用的;(3)限制混叠的作用[4]。

1 峰值检测模块的设计

1.1 实现峰值检测的方法

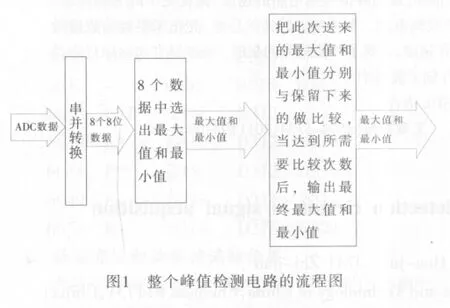

在峰值检测模式下,ADC以尽可能高的采样率进行采样,这样可以捕捉更窄的毛刺信号。该项目中把在峰值检测模式下ADC的采样率设为800MS/s,相当于峰值检测的速率为800MS/s。由于ADC转换后的数据速度很快,FPGA难以处理,因此首先利用FPGA内部的差分接收机把这些数据做串并转换[5],使得数据位变为64位,相当于8个8位的数据,这样就把速度降下来了。当ADC的采样率为800MS/s时,经过降速后时钟速度变为100 MS/s。然后从8个8位数据中选出最大值和最小值,分别与上次的最大值和最小值做比较,最大值比上次的大就保留下来,否则保持不变;最小值比上次的小就保留下来,否则也保持不变。当比较次数达到设定的值后,把最终的最大值和最小值输出,并送往存储器。流程图如图1所示。

峰值检测模式下数据并不像普通采样那样直接进入存储器,而是先经过峰值检测模块筛选出最大值和最小值后,再将它们存入。存数时钟由时基档位决定,这样将ADC采样时钟和存储的时钟区分开来,使得低时基档位下同样能捕捉到信号的毛刺。采用VHDL硬件语言进行数字电路设计具有很好的灵活性[6],在设计中,采用流水线的思想,大大提高了峰值检测模块的处理速度[7-8]。

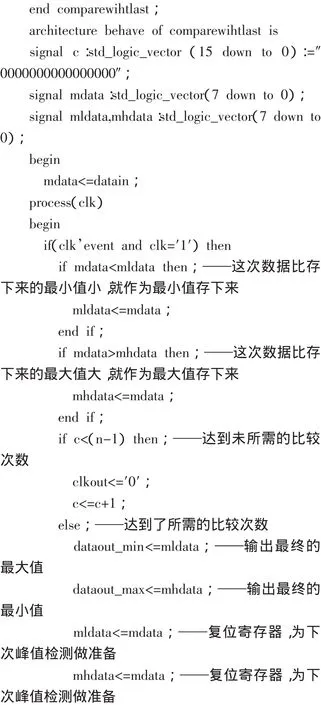

1.2 峰值检测模块的具体实现

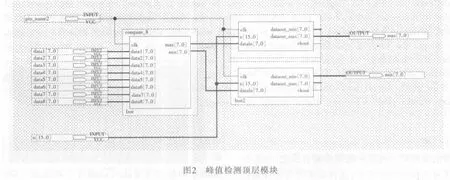

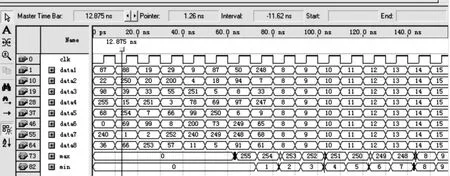

从图2中,可以看到3个模块,1个为Compare_8,这个模块的作用是把送过来的并行8个数据中选出最大值和最小值输出;另外2个均为Comparewithlast,这个模块的作用就是把此次送过来的数据与上一次存下来的数据做比较,如果比上次的最大值大就把此次送过来的值作为最大值,如果比上次保留下来的最小值小就把此次送过来的值作为最小值。当比较次数达到设定的次数以后,就输出最大值和最小值,用了2个Comparewithlast模块,上面那个用来得到最大值max[7∶0],下面这个用来得到最小值 min[7∶0]。比较次数由 n[15∶0]来设置,在示波器中根据具体的时基档位来设置不同的值。

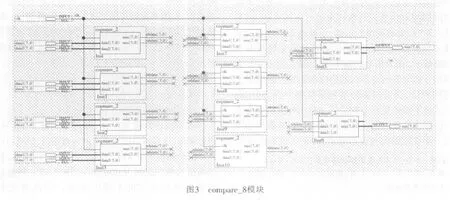

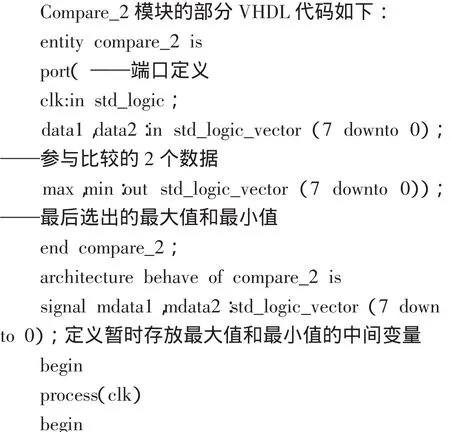

Compare_8模块内部采用了三级流水线结构[5,9],如图3所示。这样可以大大增加电路的工作速度,ADC出来的数据经过串并转换后变为并行的8个8位并行数据,两两比较,需要经过三级比较才能得到最大值和最小值。经过第1级后,从这8个数中选出4个最大值4个最小值;第2级再分别把这从第1级得出的4个最大值选出2个,从第1级得出的4个最小值选出2个;第3级从2级选出的2个最大值中选出1个输出,从2级选出的2个最小值中选择1个输出。这个模块由10个Compare_2模块组成,Compare_2模块的作用就是从2个数中选出最大值和最小值。Compare_8模块的作用就是从这8个数中把最大值和最小值找出来。

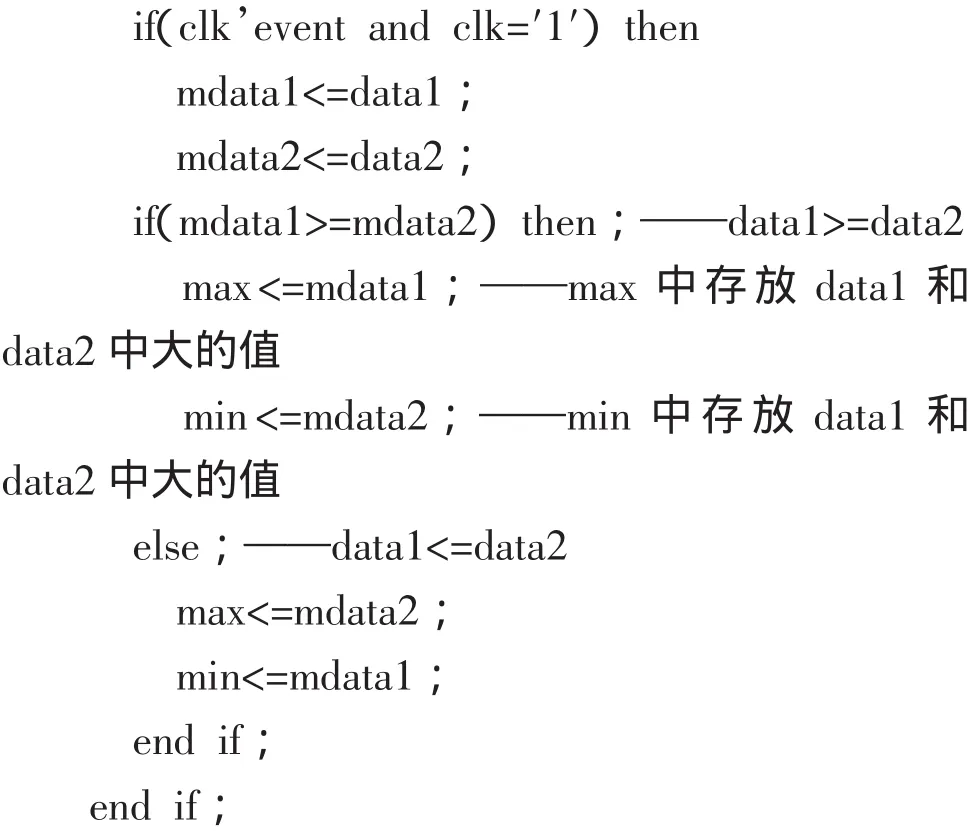

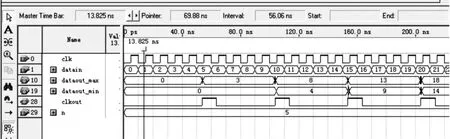

图4为Compare_8模块电路时序仿真图,data1~data8为经串并转换后的8个数据,clk为与数据同步的时钟,max为比较出来的最大值,min为比较出来的最小值。从图中可以看出,当并行的数据流速度为100M时,经过6个时钟的延迟后,最大值和最小值都正确的被选择出来了。

图4 compare_8模块电路时序仿真图

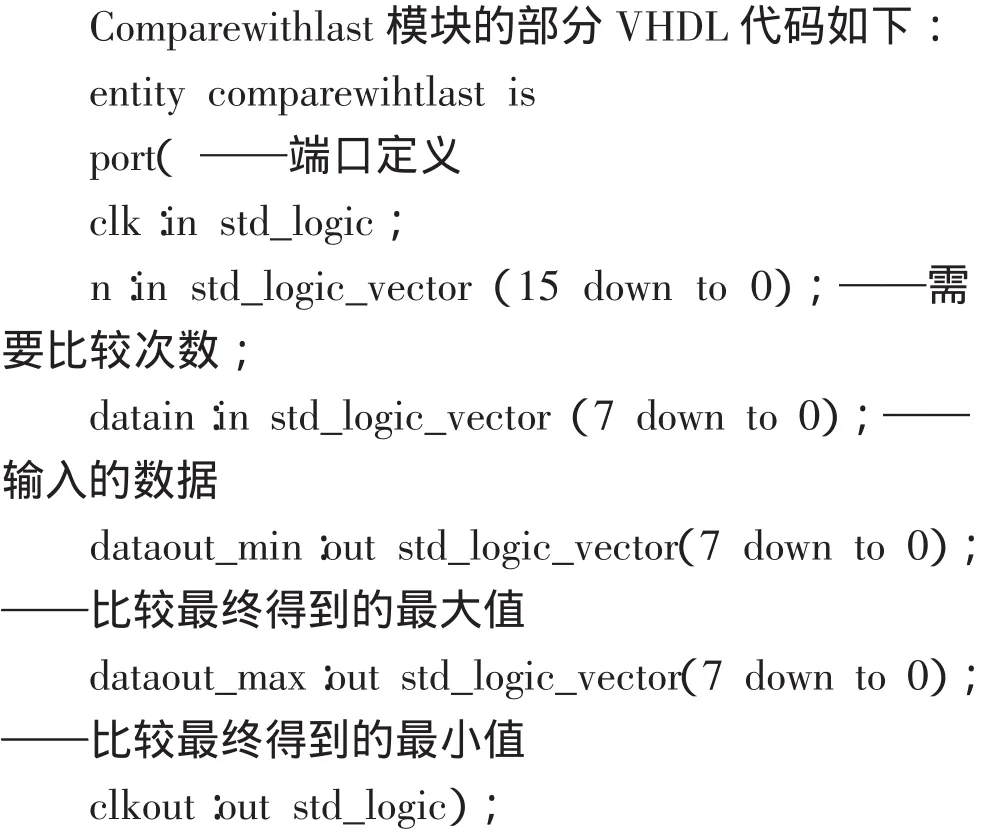

图5 comparewithlast模块电路时序仿真图

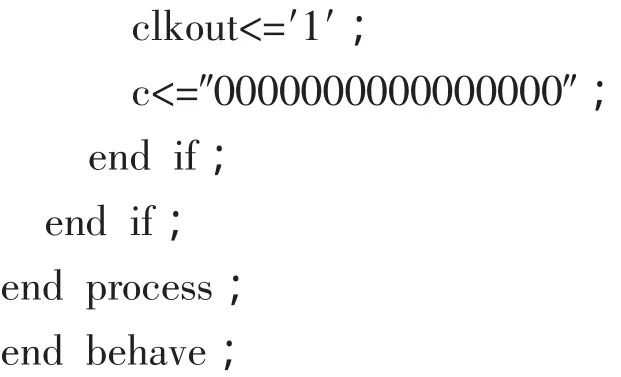

Comparewithlast这个模块的时序仿真图如图5所示。图5中,datain为100 M的串行数据,clk为输入时钟,dataout_max为最终选出的最大值,dataout_min为最终选出来的最小值,clkout为输出时钟,n为需要比较的次数。从图5中可以看出,n的值设为5,这些数据比较5次以后就将最大值和最小值都正确地输出。

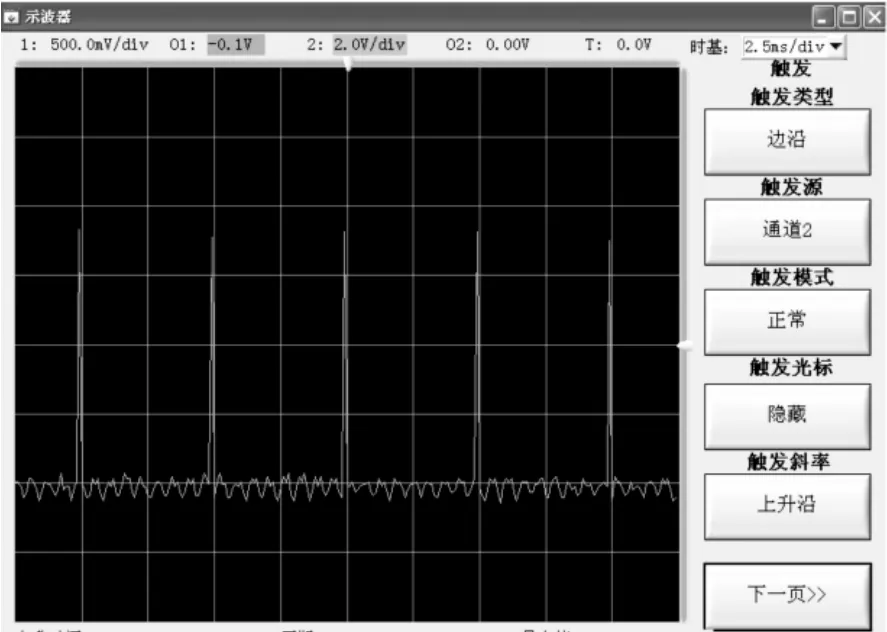

该峰值检测模块在多功能综合分析仪中的示波器模块中试验过,通过信号源输出周期5ms,宽度为2.5ns的脉冲信号对峰值检测功能进行测试,打开示波器的峰值检测功能(若在普通采样方式下,此时的等效采样率为100KS/s,即2次采样点之间的间隔是10μs,不能捕捉到如此窄的脉冲)完全捕捉到了窄脉冲信号,如图6所示。

图6 峰值检测模式下捕捉到2.5ns脉宽的毛刺信号

2 结束语

现场可编程门阵列(FPGA)器件体积小、速度快、集成度高,能够用硬件电路来实现算法程序。在FPGA中实现峰值检测模块,能够保证峰值检测的速度和可靠性,随着采样率的不断提高以及FPGA的工作速度不断提高,能捕捉的毛刺的宽度越来越窄,峰值检测技术在信号采集领域将发挥更大的作用。

[1] 沈兰荪.高速数据采集系统的原理与应用[M].北京:人民邮电出版社,1995:1-200.

[2] 马明建,周长城.数据采集与处理技术[M].西安:西安交通大学出版社,2000:1-31.

[3] 邱渡裕.200 MHz手持式示波表数字系统与电源设计[D].成都:电子科技大学,2006:32-43.

[4] 古天祥,王厚军,习友宝.电子测量原理[M].北京:机械工业出版社,2004:20-200.

[5] 黄任.VHDL入门·解惑·经典实例·经验总结[M].北京:北京航空航天大学出版社,2004:20-170.

[6] 沈立,朱来文,陈宏伟.高速数字设计[M].北京:电子工业出版社,2004:100-300.

[7] 曾繁泰,陈美金.VHDL程序设计[M].北京:清华大学出版社,2000:10-40.

[8] 陈耀和.VHDL语言设计技术[M].北京:电子工业出版社,2004:8-50.

[9]侯伯亨,顾新.VHDL硬件描述语言与数字逻辑电路设计[M].西安:西安电子科技大学出版社,1998:49-119.