ESD保护栅结构20V N沟道沟槽VDMOSFET设计

殷允超,黄秋萍

(苏州大学,江苏 苏州 215021)

1 引言

功率VDMOSFET 是将微电子技术和电力电子技术融合起来的新一代功率半导体器件。因其具有开关速度快、安全工作区宽、输入阻抗高、负温度系数、无二次击穿等一系列优点,在高频、中低功率领域得到广泛应用。

对于低压小电流VDMOSFET产品,随着器件的单个尺寸越来越小、结构越来越复杂,由于各种原因导致的静电释放(ESD)现象变得越来越显著。高静电电压会在单个器件中导致高电场和大电流密度,这些会使器件产生热损伤或使绝缘体被破坏。据统计,在所有半导体器件的失效机制中,ESD失效几乎占到10%[1]。

本文以20V N沟道沟槽VDMOSFET为例,提出了一种带有ESD保护栅结构的VDMOSFET设计制造方法,并进行了测试数据分析。

2 沟槽VDMOSFET的理论模型

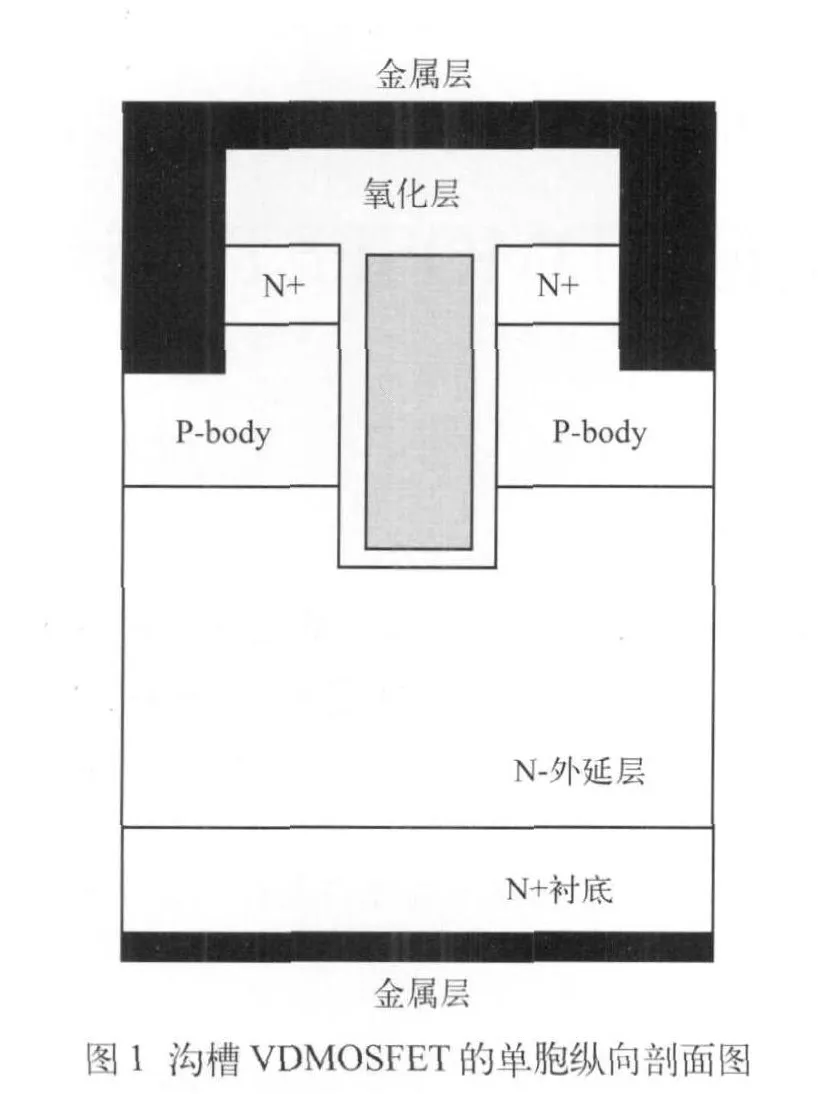

2.1 沟槽VDMOSFET的结构以及工作原理

沟槽VDMOS器件是在高阻外延层(N-)上采用平面自对准双扩散工艺,利用硼磷(砷)两次扩散差,在器件垂直方向上形成多子导电沟道,如图1所示。当栅源电压(VGS)大于器件的开启电压(VTH)时,垂直沟道表面形成强反型层,即电子沟道。在漏源电压(VDS)的驱动下,源区电子经外延层漂移至衬底漏极;当VGS小于VTH,垂直方向上不存在导电沟道,漏极与源极之间形成一个反偏PN结[2]。耗尽层主要扩展在外延层一侧,理论击穿电压值可以由外延的浓度和厚度决定。

2.2 ESD保护结构的理论实现

静电放电是直接接触或静电场感应引起的两个不同静电势的物体之间静电荷的传输。人体或设备仪器都可能带有极高的静电,静电电压甚至高达几千伏特以上,它几乎可以损坏绝大部分半导体器件和集成电路[3]。

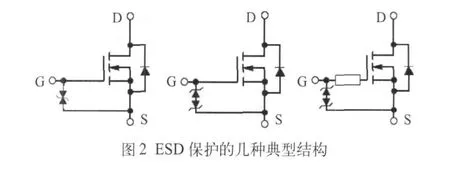

对于VDMOSFET来说,最容易被静电损坏的是栅极(G)和源极(S)之间的栅氧层,通常的保护方法是在常规VDMOSFET的基础上利用不同掺杂类型的多晶硅形成背靠背的多晶硅PN结,然后在栅极和源极之间把多个这样的PN结串起来作为ESD的保护结构[4],为了增加ESD保护的效果,有时也将电阻一起串联,基本保护类型如图2所示。

当发生ESD时,加在栅氧化层上的电压可以由背靠背的多晶硅PN结来承受,因此器件不会发生介质击穿。在此结构中,由于增加的通路中至少包含一对背靠背PN结,而PN结反向漏电较小,也就不会影响器件栅极和源极之间的绝缘性,但会增大栅极的漏电,这也是ESD保护型VDMOSFET的一个缺点。

3 20V N沟道沟槽VDMOSFET主要参数指标

本文的器件封装形式为TSSOP-8,具体的参数要求如下:漏源击穿电压BVDSS>20V,栅源击穿电压BVGSS>±12V,持续电流ID=6A,额定功率PD=2W(TA=25℃),导通电阻(Rdson@Vgs=4.5V)<20mΩ,阈值电压VTH=0.6V~0.9V(典型值为0.75V)。

栅源之间的ESD水平为HBM标准下大于2.5kV。

4 设计实现

4.1 外延规格的确定

首先是确定外延层参数,外延层的电阻率由器件所承受的击穿电压来定。我们对体二极管进行单边突变结近似,所以用公式(1)可计算出外延层的杂质浓度。

在这里BVds为器件击穿电压,ρ为电阻率,q为单位电荷1.60×10-19C,μ为外延层电子迁移率,在此取1 320cm2/V.S。由于设计为20V产品,我们取BVdss=23V,计算出NB=3.59×1016/cm3,ρ=0.132Ω.cm。

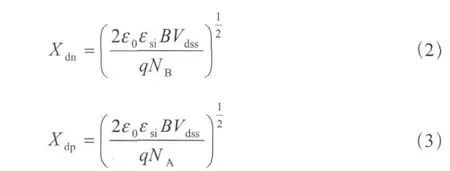

外延层厚度We由N+结深和Vds为击穿电压时的N+区和P区侧的耗尽层宽度所决定[5],即We=Xdn+Xdp+Xjn+。

这里ε0=8.85×10-14,εsi=11.7,BVdss=23V,q=1.6×10-19C,NB=3.59×1016/cm3,代入式(2)得:Xdn=0.91μm,此时可以确定沟槽深度需大于0.91,为保证余量,后续设计中取沟槽深度为1.1μm~1.3μm。

NA为P区表面的掺杂浓度,取NA=1×1016/cm3,带入式(3)得出Xdp=1.73μm。

对于Xjn+我们采用As注入,取Xjn+=0.35 μm。于是We=0.91μm+1.73μm+0.35μm=2.99μm。由于制造工艺中有场氧化环节,以场氧化0.7μm计算,需要腐蚀掉约0.35μm的外延,为保险起见,该产品外延厚度取3.5μm。最终确定的外延规格为浓度0.132Ω.cm、厚度为3.5μm。

4.2 终端结构设计

本设计中,我们采用了场板、多晶硅场限环和截止环的复合终端结构,场限环由沟槽型浮置多晶硅构成,截止环也采用沟槽型内填多晶硅设计。这种设计不但可以有效提高器件的耐压,还可以减少光刻版的数量,节省了成本[6]。具体的设计示意图如图3所示。其中上方深色部分为金属,中间色部分为多晶,下方浅色部分为氧化层。

4.3 ESD保护结构的设计

设计ESD保护结构,首先我们应该确定多晶硅二极管对的数量。由于每对多晶硅二极管所能承受的电压约为4V~6V,而该产品希望得到12V以上的BVgss,所以本设计基于普通VDMOSFET的基础,在栅极区制作三对背靠背的多晶PN结,这三对PN结串起来并联在VDMOSFET的栅极和源极之间,起到保护栅氧化层的目的。

具体的实现方法为在栅极区淀积掺有N型杂质磷的多晶硅,并且间断性地注入P型杂质硼形成PN结。通过改变硼的注入剂量以及退火温度和时间,选择合适的多晶硅面积,就可以调整ESD保护的能力。图4为本设计中栅极区的剖面示意图。

4.4 版图设计

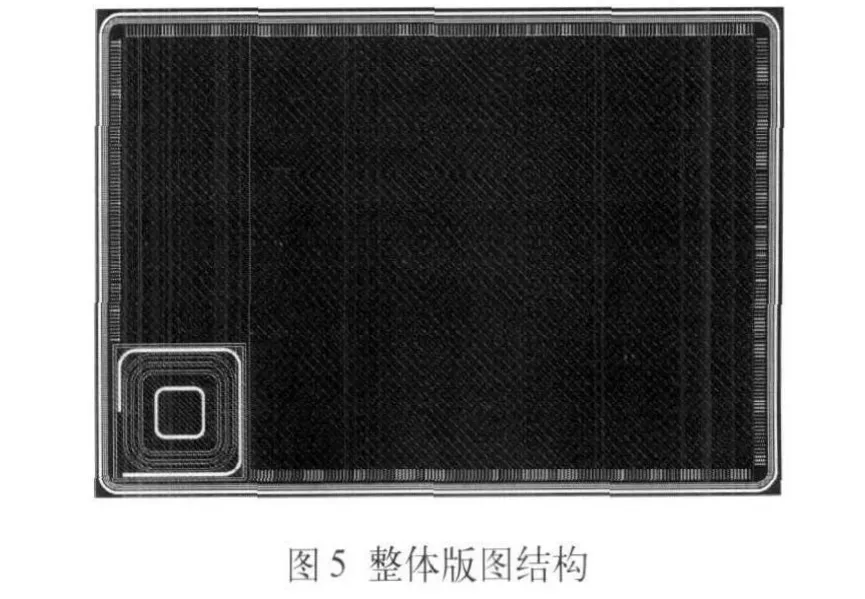

版图设计时,要尽量减小芯片面积和多晶硅栅的输入电阻。本设计中采用长方形的设计,其中单胞尺寸(pitch)设计为1μm;为保证栅极多晶硅注入的面积余量,栅极区大小为220μm×220μm。整个芯片的面积为700μm×1 100μm(包含60μm的划片道),包含的单胞数量约为58.2万个。整体版图如图5所示。

4.5 工艺流程设计

在集成电路的加工工艺中,光刻版的数量直接决定了加工成本,本设计中使用特殊的流程将光刻版的数量压缩为6层,分别为有源区(Active)、沟槽(Trench)、多晶(Poly)、源极注入(N+)、孔(Contact)和金属(Metal)。主要的工艺流程如下:

场氧化→有源区曝光(光刻版1)→显影→湿法腐蚀→去胶→TEOS淀积→增密→沟槽曝光(光刻版2)→显影→TEOS腐蚀→去胶→沟槽腐蚀→牺牲氧化→湿法腐蚀→栅氧→ESD-poly 淀积→原位掺杂/退火→ESD-poly 硼注入→多晶曝光(光刻版3)→显影→多晶腐蚀→去胶→硼注入→P-Well推阱→N+曝光(光刻版4)→砷注入 →退火→BPSG淀积→回流→孔曝光(光刻版5)→显影→ANISO孔腐蚀→去胶→二氟化硼(BF2)注入+→硼注入→BPSG回流→钛/氮化钛(Ti/TiN)→快速热退火(RTA)→钨填充→金属(AlSiCu)→金属曝光(光刻版6)→金属腐蚀→合金→晶圆背面减薄→背金(钛镍银)。

4.6 晶圆片CP数据以及分析

在分片单中,主要对沟槽深度、栅氧化层厚度、P阱注入能力和剂量、ESD-poly的注入等条件进行分片,具体的分片单以及CP测试结果如表1(其中△代表基本条件,▲代表分片条件,每种条件2片,偶数片号省略)。

由测试结果可以看出:

(1)沟槽深度分片:沟槽越深,BVDSS值越低,相应导通电阻也越低。这是因为VDMOSFET的击穿点一般在沟槽的底部,沟槽越深,相当于外延的厚度降低,击穿电压也低,导通电阻也跟着变小。

(2)栅氧化层分片:栅氧越厚,VTH的值会越大。这是因为栅氧越厚,沟道(耗尽层)就越难形成。

(3)P阱分片:P阱注入剂量越大,VTH会越高。这是因为P阱注入剂量增加时P阱的电荷量增加,即沟道表面浓度增加,沟道(耗尽层)也就越难形成。

(4)ESD-poly注入分片:多晶注入剂量越大,相应的栅源之间的漏电越小。这是ESD保护结构的多晶PN结漏电变小所致。

对比设计要求,我们可以确定的条件为:沟槽1.3μm,栅氧厚度20nm,P阱注入剂量每增加1×1012,VTH增加0.6V,为了确定其他条件,我们选择1#、9#进行封装,待成品测试后再决定。

5 晶圆封装以及成品测试分析

5.1 器件的封装形式

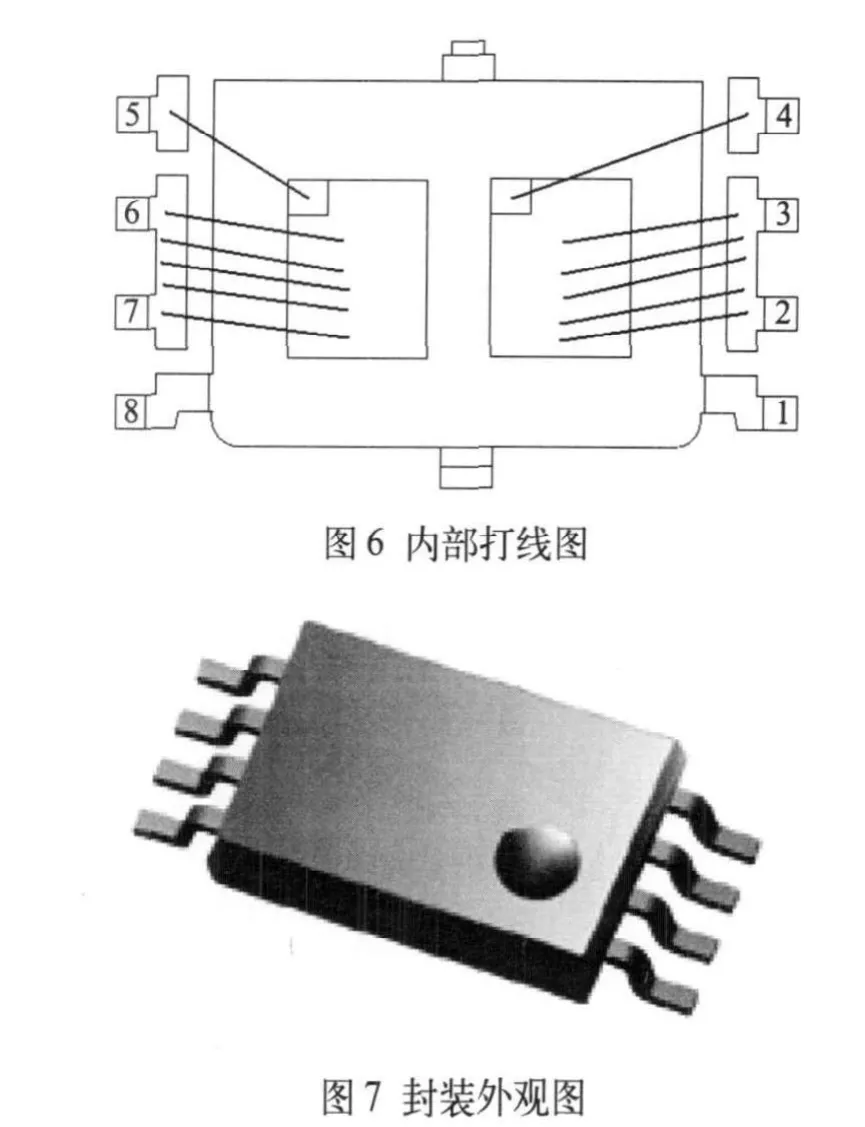

封装采用TSSOP-8形式,打线方案为:42 μm的铜丝、栅极1根、源极5根。内部打线以及外观图如图6、图7所示。

5.2 直流以及ESD测试

接下来我们对成品进行测试,BVdss、VTH、VFSD以及漏电均未有明显改变。而Rdson会增加封装寄生电阻,如1#Rdson具体值为:16.3mΩ @Vgs=4.5V;封装测试的良率:1# 为96.4% 、9#为 95.8%;ESD的测试值为1# 2.8kV HBM、9# 2.3kV HBM。最终我们选择1# 微调P阱剂量到1.3×1013作为最终条件。

6 结论

本文通过理论计算、仿真等工具给出了ESD保护型20V N沟道沟槽VDMOSFET的结构、外延及版图,并通过实际的流片、封装得到了最佳的工艺条件。

[1]R G Wangner, J Soden, C F Hawkins. Extent and cost of EOS/ESD damage in an IC manufacturing process[C].In:Proc.15th EOS/ESD Symposium,1993. 49-55.

[2]闫冬梅,张雯.50V/40mΩ VDMOSFET单胞尺寸的最佳设计[J].微处理机,2004, 2:5.

[3]李泽宏,易黎,张磊.多晶硅ESD结构保护的垂直双扩散金属氧化物半导体功率器件,中国专利,200610022264.2[P].2007-5-16.

[4]沈伟星.低压功率沟槽MOSFET的设计与研究[D].硕士学位论文.上海大学.68.2006.

[5]王蓉,李德昌.低压功率VDMOS的结构设计研究[J].电子科技,2010,23(4): 33-34.

[6]朱袁正,秦旭光.一种深沟槽大功率MOS器件及其制造方法,中国专利.200710302461.4[P].2008-7-2.