射频识别阅读器中信道选择滤波器的设计*

李 斌,田应洪,张 勇,张润曦,赖宗声

1.华东师范大学微电子电路与系统研究所,上海 200062;2.华东师范大学纳光电集成与先进装备教育部工程研究中心,上海 200062

LI Bin,TIAN Yinghong,ZHANGYong,ZHANGRunxi,LAIZongsheng*

1.Institute of Microelectronics Circuit&System,East China Normal University,Shanghai 200062,China;2.Engineering Research Center for Nanophotonics&Advanced Instrument,Ministry of Education,East China Normal University,Shanghai 200062,China

射频识别(RFID)技术在当今无线通信领域应用十分广泛。相对于 LF(120~135 kHz)波段和 HF(13.56 MHz)波段,UHF波段的 RFID技术能够在m级距离上提供数百 kbit/s的数据通信,因而备受关注[1]。目前成功商业应用的 UHF射频识别系统阅读器往往采用分立元件构造[2],共同的缺点是体积大、功耗大。随着 CMOS工艺技术的发展进步,如果能够提供基于 CMOS工艺的单片阅读器将极大的降低成本,应用前景也将更为广阔;而且单片集成的阅读器方案也符合当前多应用[3]便携式终端的发展趋势,为未来多应用整合提供可能。

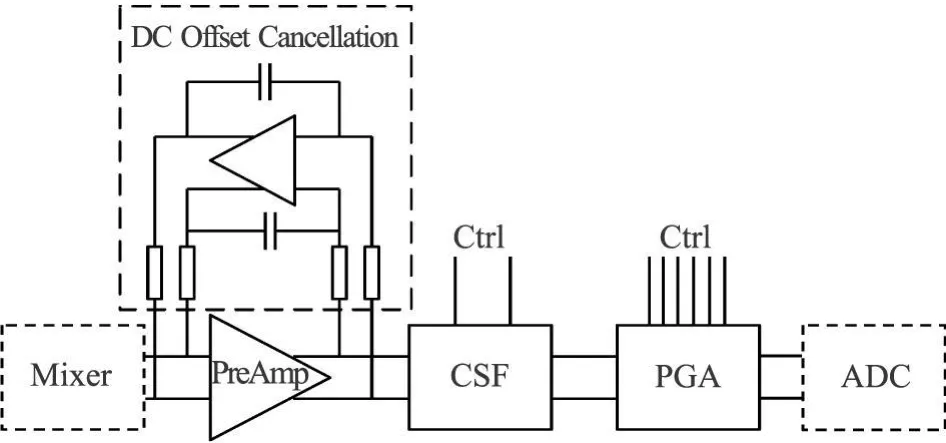

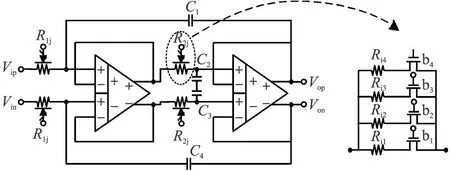

本文设计的信道选择滤波器用于 UHF RFID阅读器接收机模拟基带部分,接收机采用 I/Q两支路正交的零中频结构,图 1是接收机模拟基带结构图。根据 EPCglobal C1G2协议要求,UHF RFID阅读器接收的最高数据速率达到 640 kbit/s,最大信号带宽不超过 1.28 MHz;对于 40 kbit/s的最低速率,其信号带宽小于 250 kHz,于是,接收基带信道选择滤波器的带宽为 0.3~1.3 MHz范围内可调[4]。

图 1 信道选择滤波器用于RFID模拟基带

另外,根据 transmission mask的要求,相邻两信道的功率差为 40 d B。在本信道最小信号条件下,仍要保证本信道与相邻信道同时保持通信,这就要求信道选择滤波器能够克服临道比本道高 40 dB的干扰,于是在设计的时候要求信道选择滤波器在两倍频处有大于 45 dB的抑制。

根据 UHF RFID接收机结构的特点,在多读写器环境中,接收机将面临幅度较大的干扰信号,这就要求滤波器有能力处理大幅度的输入信号,即对其线性度要求较高。为了得到更高的线性度与更好的噪声特性,设计采用运算放大器 -RC结构滤波器模式。通过仿真,决定采用六阶 Chebyshev低通滤波器结构来实现信道选择滤波器的设计。

文章首先给出了六阶 Chebyshev低通滤波器设计过程;然后给出 Chebyshev低通滤波器的版图以及滤波器和运放的仿真结果;最后做出结论。

1 六阶 Chebyshev低通滤波器设计

1.1 二阶 Chebyshev低通滤波节

图 2给出了其二阶低通滤波节(Biquad)结构,其传递函数为:

尽管带内的平坦特性不如 Butterworth近似[5],但它具有更快的幅度衰减特点[6]。

图 2 二阶Chebyshev低通滤波节

从图 2可以看到,滤波器中的运算放大器接成了缓冲器形式,是典型的双端输入、单端输出的运算放大器。由于缓冲器的两个输入端均悬空,当输入信号为差分形式时,无法构成全差分缓冲器[7]。通常的解决方法是用两个单端输出的运算放大器去实现一个全差分结构的缓冲器,即一个运放作为正输入端,另一个运放作为负输入端,这就造成了器件数量的加倍,输入端的匹配也很难达到,所形成的全差分缓冲器的性能并不理想。如何形成全差分的缓冲器,在运放的设计过程中需要着重考虑。

1.2 运放的设计

运算放大器是运算放大器 -RC滤波器的核心部件。根据系统的设计要求,运算放大器开环增益在 70 d B以上,增益带宽积大于 65 MHz,相位裕度取在 65°~70°左右,SR值应取大于 12 V/μs。上文中提出缓冲器输入端悬空的问题,采用全平衡差动放大器 FBDDA(Fully Balanced Differential Difference Amplifier)可以方便的解决。

图 3给出了 FBDDA的示意图及按照负反馈方式构成的全差分缓冲器结构。FBDDA的输入输出关系可以表示为:

Ao为理想状态下运放的开环增益。当采用负反馈时可以得到如下的关系:

以上关系仅当 Ao→∞时才可以成立,所以在设计运放时开环增益越大越好。

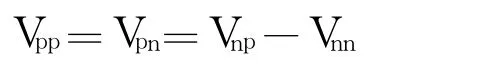

图 3 FBDDA与全差分缓冲器

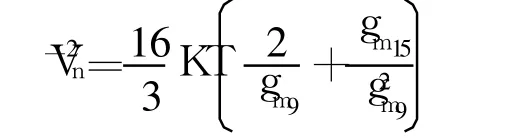

图 4所示为 FBDDA。图 4(a)是一种两级结构的运算放大器,是 FBDDA的核心电路,图 4(b)与图4(c)所示电路分别用来稳定运算放大器第一级输出与第二级输出的共模电平。运算放大器的第一级放大器由两个差分对构成,使得电路具有四个输入端。为了获得良好的噪声系数,电路的输入管为PMOS管 (M9、M10、M11、M12),负载管为 NMOS管(M15、M16)。运算放大器的第二级为共源级结构,输入管采用 NMOS管(M14、M17),负载管采用 PMOS管(M6、M18)。电路采用米勒补偿电容(Cc)和调零电阻(Rc)以保证运放的闭环稳定性。经过计算可以得到全平衡差动电路的小信号增益如下式所示:

图4 全差分差动放大器电路

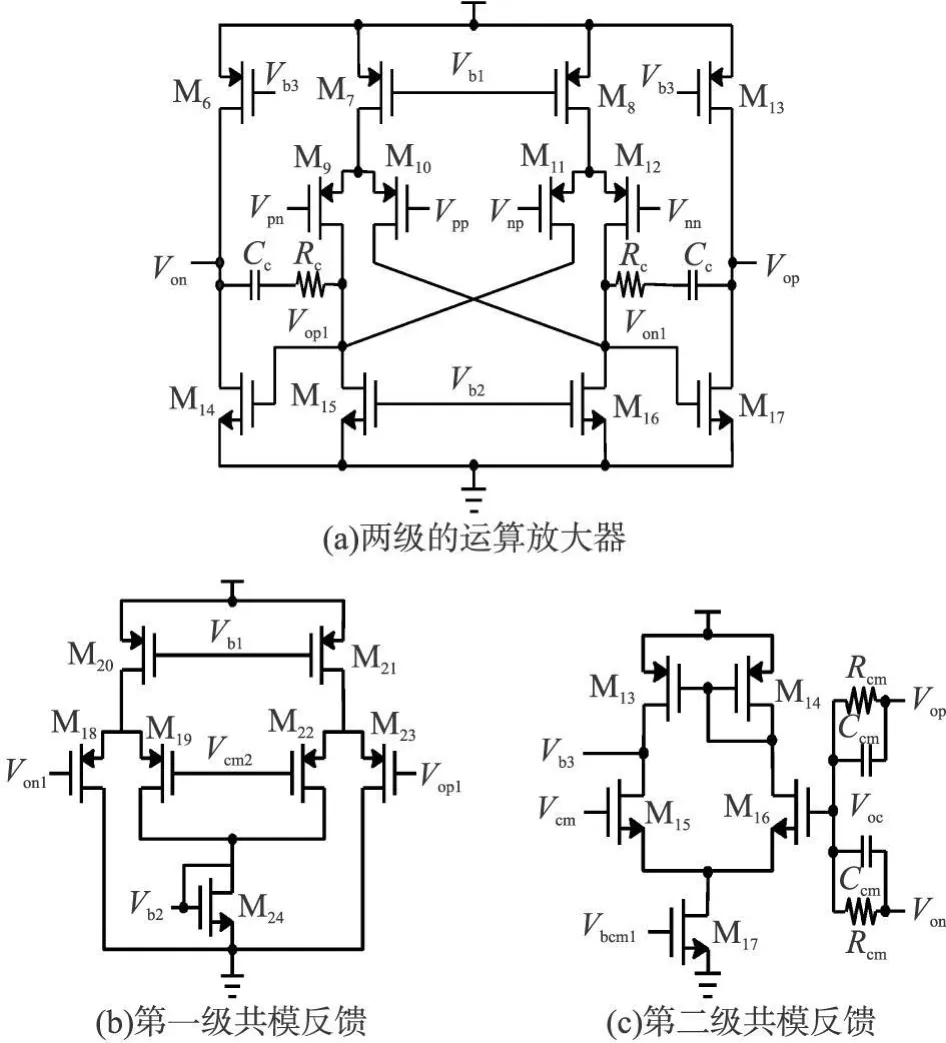

其中 gm和 ro分别表示 MOS管的跨导和输出电阻。为了提高运放的增益,可以增大 gm和 ro。经过计算放大器的等效输入热噪声可表示为:

其中 K为波耳兹曼常数(1.38×10-23J/K),T为开尔文温度。从上式可以看出,要减小整个运放的噪声,输入管应使用较大宽长比的 PMOS管,负载管应使用较小宽长比的 NMOS管。一般的共模反馈电路在设计时都是放在第二级的输出端,用来稳定运放的输出电压[8]。本文为了满足在所有工艺角中运算放大器的性能,在运放的第一级也添加了共模反馈电路,用来稳定第一级的输出电平。本文设计的两种不同结构的共模反馈电路如图 4(b)、4(c)所示。

1.3 六阶 Chebyshev低通滤波器设计

图 5给出了采用 FBDDA构造的二阶 Chebyshev低通滤波器结构,图 6给出了 FBDDA构造的六阶级联 Chebyshev低通滤波器结构 (C2和 C3、C6和 C7、C10和 C11间接参考电平 1.6 V)。

图 5 全差分二阶低通切比雪夫滤波器

图 6 全差分六阶切比雪夫滤波器

为了实现截止频率的切换并防止由电阻电容误差引起的频偏,使用 MOS开关控制接入电路中电阻的大小,电容为固定的 3pf。在电路中通过译码器利用数字信号控制开关的通断,实现了截止频率在300 kHz~1.3 MHz中可调,表 1为经过优化后信道选择滤波器的电阻取值方案。

2 版图设计与仿真结果

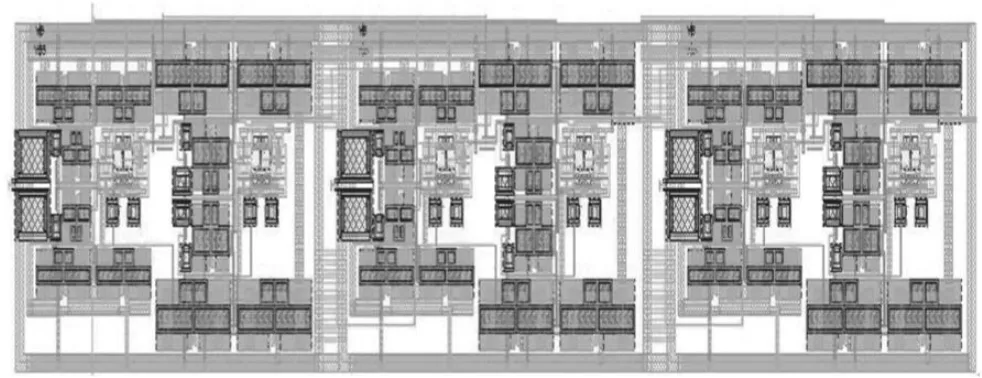

本文的六阶 Chebyshev低通滤波器采用 IBM 0.18μm工艺进行设计,仿真。图 7是对滤波器的版图,面积1 600μm×400μm。

图 7 六阶Chebyshev低通滤波器版图

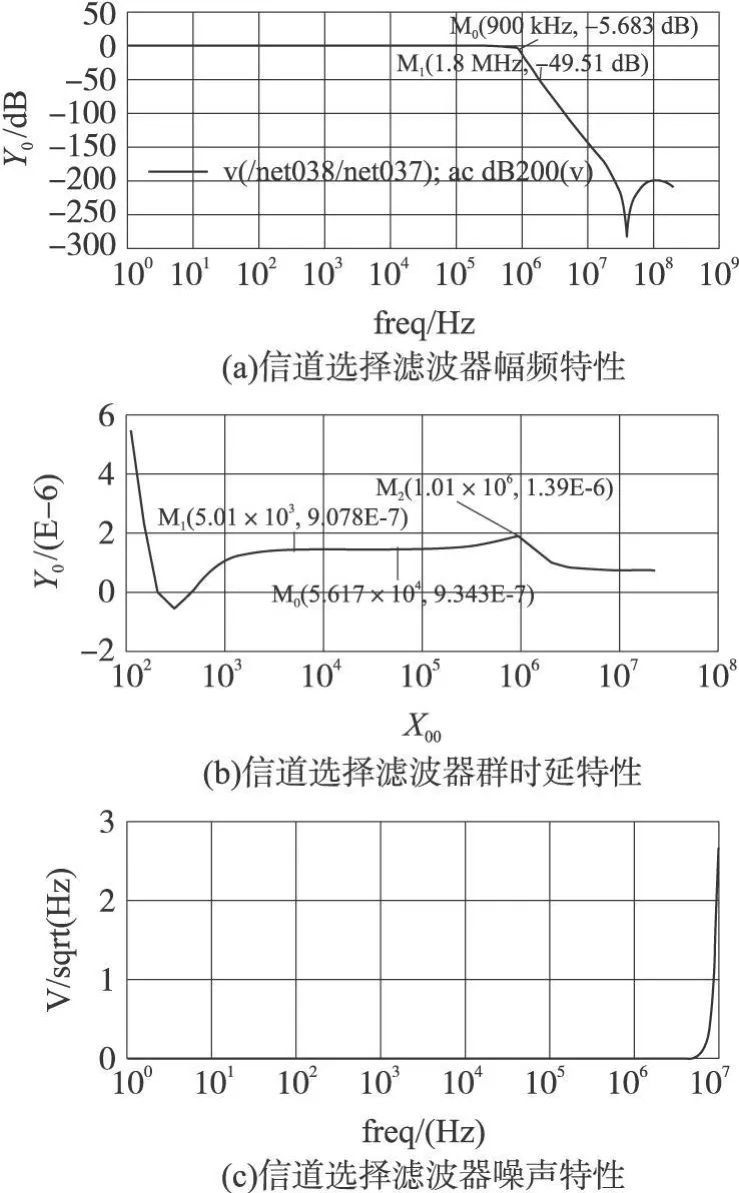

图 8为截止频率设为 900 kHz时滤波器的交流、噪声及群时延特性。从图 8(a)中可以看到,滤波器的 -3 d B带宽在 900 kHz左右,带内增益稳定在 0 dB,在 1.8 MHz频率处具有大于 49 dB的幅度衰减,满足信道选择滤波器的设计指标;从图 8(b)可以看出,滤波器在整个通带内的群时延在 1μs左右,变化量不超过 0.5μs;在图 8(c)中,10 kHz频率处的输入噪声电压为 44 nV/Hz,1 MHz频率处的输入噪声电压为 80 nV/Hz,通带内等效噪声系数为 42 dB,满足了 UHF RFID阅读器系统的要求。

图8 信道选择滤波器的特性

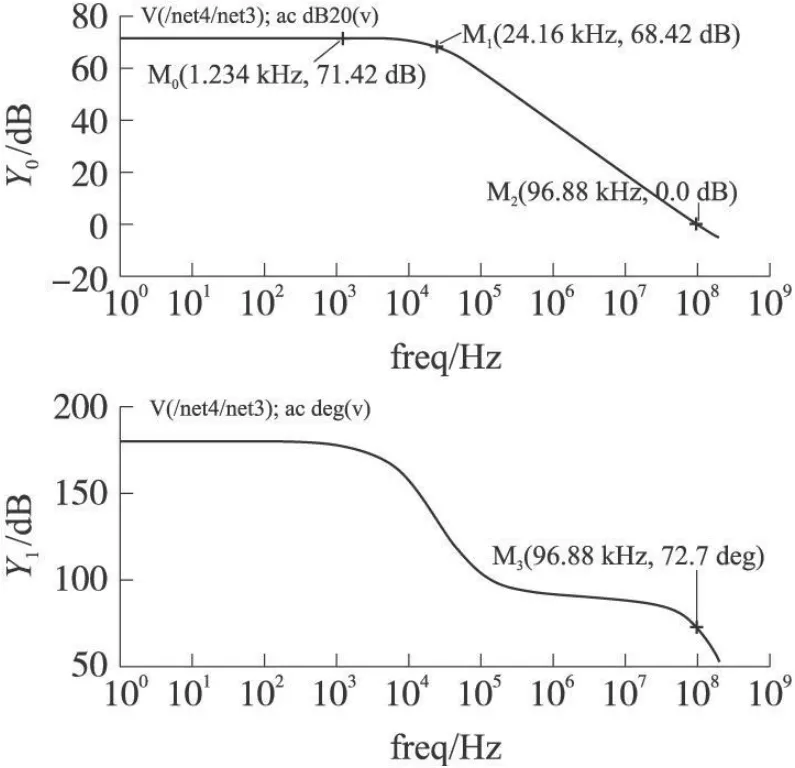

图 9是全平衡差动放大器开环情况的幅频、相频特性。从仿真的结果可以看出运放的增益为71 dB,GBW为 96 MHz,外接 2 pF电容负载时的相位裕度为 72.7°,可以满足闭环稳定工作的条件,不会出现振荡的情况。图 10是全平衡差动放大器的噪声特性,可以计算得到等效噪声系数约为 16 dB。

图 9 FBDDA开环幅频、相频特性

图 10 FBDDA噪声特性

表 2总结了 Chebyshev信道选择低通滤波器在27℃、TT条件下相关性能的仿真结果。对其它工艺角及温度的仿真结果也均达到系统的要求。

表2 信道选择滤波器的相关性能仿真结果

3 结论

本文介绍了一种用在 UHFRFID模拟基带中的信道选择滤波器,详细描述了它的工作原理和电路结构,给出了具体的设计过程,获得了比较理想的噪声特性和线性度。

[1] Lee Jei-yong,Choi Jae-hong,Lee K H,et al.A UHF Mobile RFID Reader IC with Self-Leakage Canceller[C]//IEEE Radio Frequency Integrated Circuits(RFIC)Symposium.Korea,2007,273-276.

[2]Advanced Universal Reader Architecture(AURA)[EB/OL].At:http://www.skyetek.com.

[3]Gustafsson M,Parssinen A,Bjorksten P,et al.ALow Noise Figure 1.2-V CMOSGPSReceiver Integrated asa Part of a Multimode Receiver[J].IEEE J Solid-State Circuits,2007,42(7):1492-1500.

[4]Couch L W.Digital and Analog Communication Systems[M].Fifth Edition,Prentice Hall,1999.

[5] 马德群.射频系统内低中频滤波器的设计和研究[D].复旦大学博士论文,2004.

[6]Su K.Analog Filters[M].Second Edition,Kluwer,2002.

[7]Alzaher H,Ismail M.A CMOSFully Balanced Differential Difference Amplifier and Its Applications.IEEE Transactions on Circuits and Systems-PartⅡ:Analog and Digital Signal Processing,48(6)June,2001.