图形测试:多工位模拟和混合信号器件并行测试效率的关键

Jack Weimer

(泰瑞达,Eagle 业务部)

1 并行测试效率

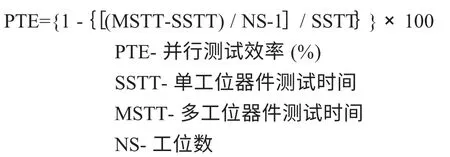

并行测试效率(Parallel Test Efficiency :PTE)是一个关于多工位器件测试工作效率的计量。

用百分数表示,PTE 是一个测试系统的品质和是否适合高产量测试的指示器。PTE 用以下公式计算:

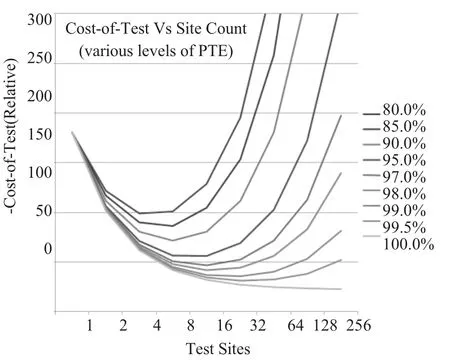

综观历史,最好的有效率的并行测试范例是在DRAM测试领域。由于这个市场极高的产量和无边的价格压力,独特的测试系统和器件分选机被开发提供最高的量产效率。这些测试单元可同时测试多达256个器件,而且同测工位数还在不停增长。这些具有巨大测试工位数的测试系统要达到其测试成本(COT)目标,最终产生好的经济效益,PTE必须尽量接近100%(见图1)。

图1 PTE Chart

为了生成如图1所示的PTE 图表,必须作一些有关测试单元成本和每工位增加成本的假设。不同的成本假设图表结果会有些不同。尽管如此,该图表提供了一个生产管理者经常会面对的产量权衡的可信的例子。虽然该模型中没涉及,但值得注意的是由于测试机台和/或分选机扩展的不连续,测试单元的成本可能会随着同测数的提高而非线性改变。

通过分析,该图表显示32个工位同测一般要求PTE 到99%以上。成功的16个工位同测要求PTE 大于97%,8个工位同测要求PTE 至少在85%。这些数据点突显了一个测试系统高并行测试效率的重要性。PTE的提高是走向更高工位同测数,达到更低的测试成本的先决条件。

2 图形测试

给模拟和混合信号器件测试带来更高的并行测试效率。

很久以来,ATE 产业已经认识到多工位测试是有效率的测试成本(COT)模式。和单工位测试比较,多工位测试所节省的成本是可观的。多工位测试可以大大缩减完成一定产能所需的测试单元数量(测试机和分选机或探针台,机械手,接口连接硬件的组合),占地面积及操作工。高并行测试效率是最大化这种模式效率,降低整个测试成本的基本要素。

为了理解这些限制多工位模拟和混合信号器件测试并行测试效率的因素,有必要把典型的模拟测试方法和传统的数字测试方法进行对比。由于数字器件测试通常不需要详细的数据结果,数字器件测试一般按pass-fail 模式操作。而在模拟测试中,多数测试设计为输出详细的数据结果,可用于统计分析。数字测试是利用硬件激励(无软件介入)带有预定控制时序的激励响应数据,自然是图形测试。

数字器件的响应通常是随着图形的运行而实时地进行on-the-fly 评估。模拟测试常常是在低端设备上,不采用图形或硬件激励的方法来完成。为了把模拟测试匹配到数字测试模型,需要硬件技术使模拟和混合信号测试在多工位测试中真正同时进行。

由于详细的数据结果对统计过程控制(SPC:Statistical Process Control)和模拟器件生产是必需的,模拟图形测试必须合并数字图形技术的速度和并行性同时能提供详细的测试结果作数据记录。模拟图形测试的方法因此必须采用硬件激励预定的测试条件。为了和数字并行测试模式完全一致,模拟的测试也需要实时的on-the-fly 评估测试结果。

今天的现实是大多数的半导体生产商没有用和存储器测试中常见的的并行测试效率来测模拟和混合信号器件。典型的DRAM并行测试效率大于99.9%,而许多模拟和混合信号器件并行测试效率在80%到98%之间,取决于应用程序和测试系统。

3 有效并行测试的测试机架构

影响并行测试效率的一个关键因素是每一工位必须具有独立的资源。有效率的多工位测试平台必须提供专门只用于各个工位的资源。工位间共享资源会使测试运行成为串行过程。这是一个测试系统没有很好的设计有效并行测试的典型问题。测试系统工位间共享资源会限制测试机的效力,降低可测的最大工位数导致测试机效率的降低。

有效率的多工位测试机架构的另一个重要方面是资源的通道密度。测试系统必须提供大量的资源通道来支持足够多的测试工位数。从经济的观点,如果PTE 够大,测试工位数越多,测试费用会越低。以模拟测试为例,每个工位上需要有一定数量的V/I 通道。

如今,多数测试机厂商在测试头里放置资源来提高测量的精度和性能。因此,测试头内部的资源插槽是很重要的,尤其是考虑到通道密度。有效率的测试系统设计会最好地利用插槽的空间。通道密度必须和每一资源的覆盖面和特征相平衡。由于模拟测试要求的多样性,测试机厂商需要提供多种通道密度高覆盖面大的资源。

从混合信号测试系统的数字部分来看,数字通道的PSQ 数量(per pattern sequencer)是影响测试效率的一个重要因素。每一测试工位条件跳转运行是佷常见的。条件跳转可能是必须的,或者是缩短测试时间的一种方法。有效率的架构会在比较少的通道上提供独立的PSQ 控制。

另一个重要的系统设计是数字和模拟信号的同步。许多测试情况下要求数字信号和模拟信号之间紧密联系。因此,有效率的测试系统应该提供直接精确的同步方法。

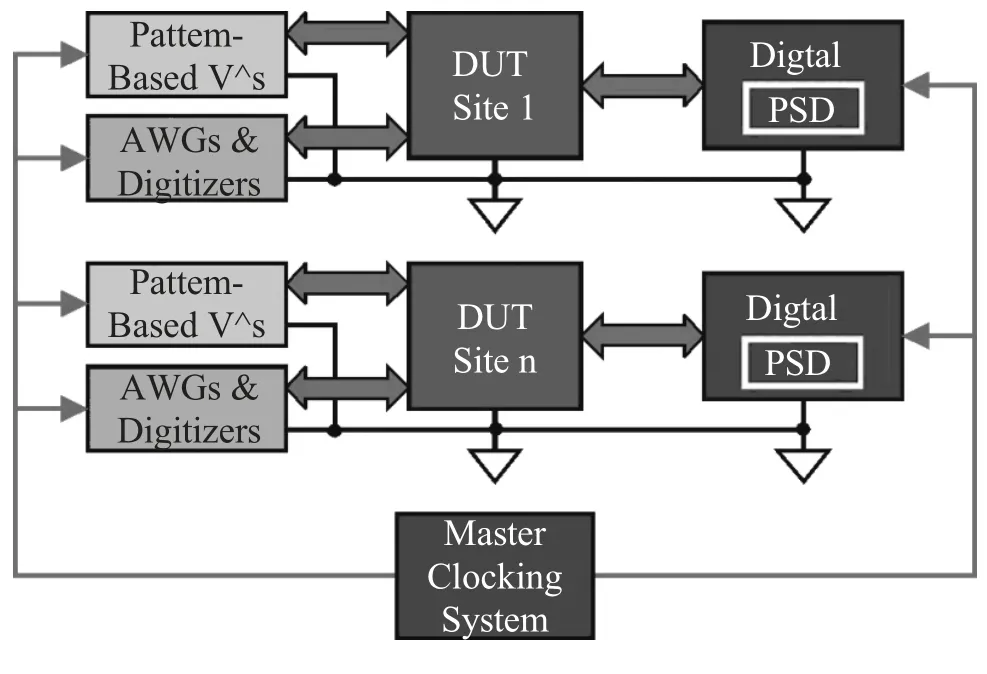

图2 Multisite Mixed-Signal Architecture

图2 表示一个多工位混合信号测试系统的简单架构。图中,每一工位都有各自专门的资源,模拟和数字资源通过主时钟同步。该架构对中等数量的工位数是有效率的,但要达到32 工位以上则需要更加复杂的方法。

在第二,三部分,我们将介绍模拟图形测试的硬件,并概述泰瑞达的SmartPinR技术。