数字信道化高效结构的FPGA实现

马元良

(青海民族大学,西宁 810007)

0 引言

数字信道化技术在软件无线电系统和宽带数字接收机中使用较为普遍,该技术的应用可以将高速采集到的数据均匀分配到各个子带信道进行同时处理,且彼此之间具有独立性。数字信道化结构设计是该技术能否工程化实现的重点,即在考虑可实现问题上,需要采用高效结构来实现。由于信道化处理通常会耗费很大的运算量和硬件资源,因此如何高效地实现信道化过程一直是电子通信领域研究的热点和难点 。本文重点研究数字信道化的高效实现结构以及FPGA实现问题。

1 数字信道化方法研究

1.1 基于多相滤波结构的数字信道化

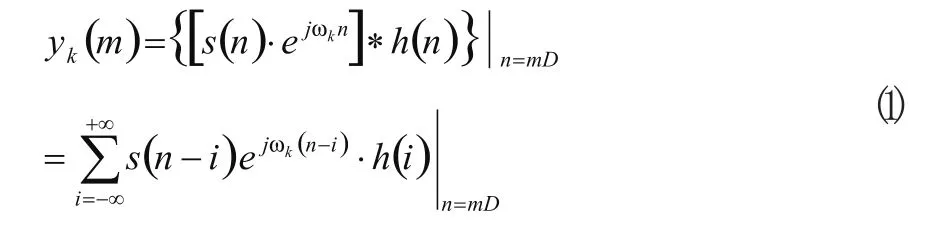

多相滤波结构是从低通结构转换而来的,令s(n)为输入信号,h(n)为低通滤波器冲激响应,假设均匀划分为K个信道,抽取比为D,在采用临界抽取条件下,即K=D,可以由低通结构推导出多相滤波结构,则第K路信道的输出为[2~4]

如果假设信号D倍抽取后多相结构表达式为(sp(m)=s(mD-p),而多相滤波器分量表达式为(hp(m)=h(mD-p) ,用 带入公式中,可得:

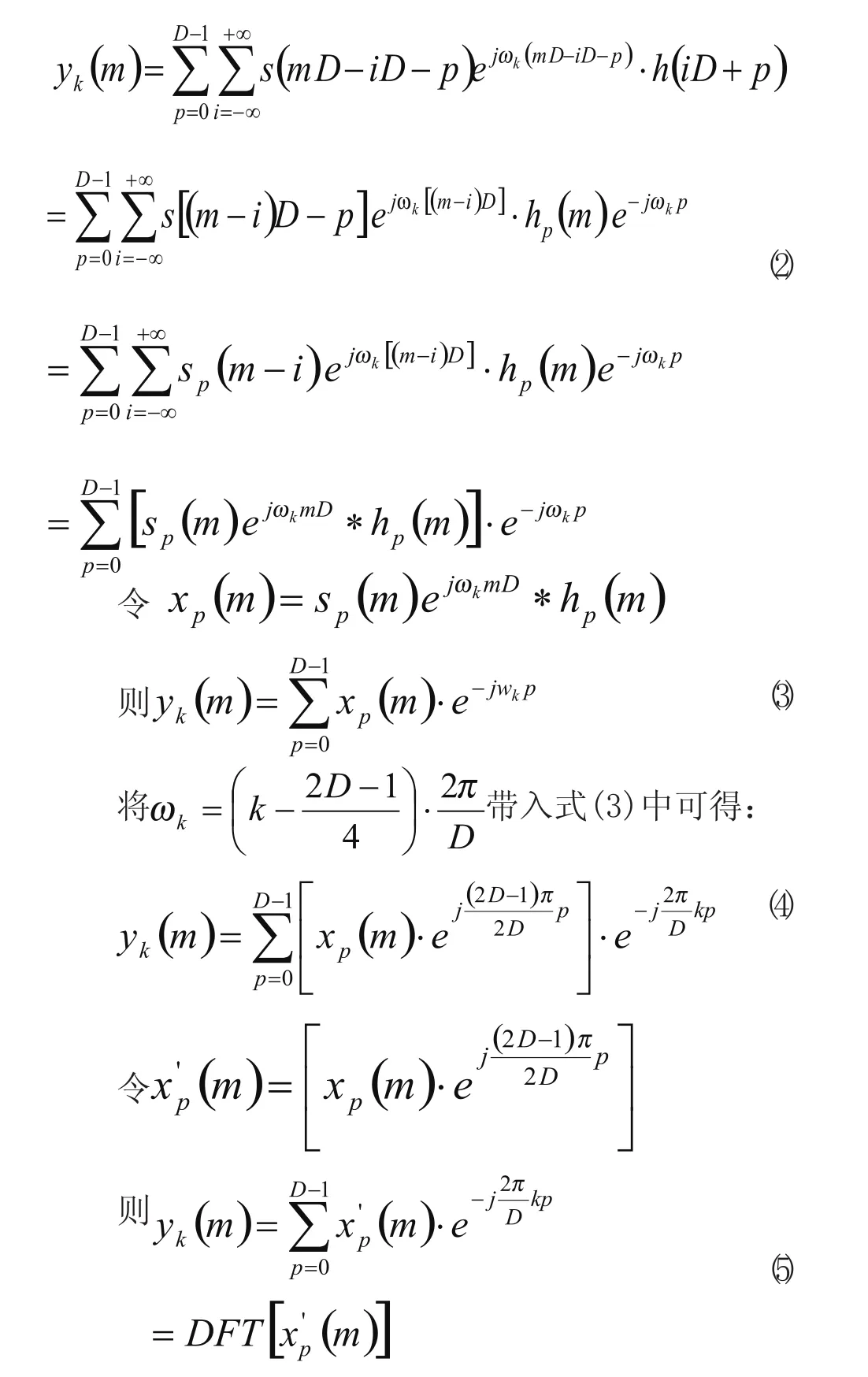

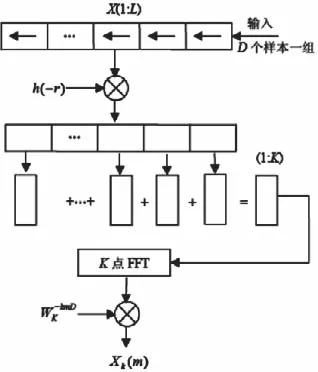

图1 数字信道化高效结构

从低通结构到多相结构的推导和转换过程,可得到高效信道化接收模型,如图1所示。

该转换中首先将高速A/D转换后的数据进行D倍抽取,并将抽取置于混频之前,然后再混频、滤波,之后采用DFT结构实现。利用FFT代替DFT,可提高数据处理速度,同时多相结构滤波器阶数仅为低通结构滤波器阶输得1/D倍,节省了大量硬件资源,充分体现了该结构的高效性[5]。

1.2 基于短时傅立叶变换的数字信道化

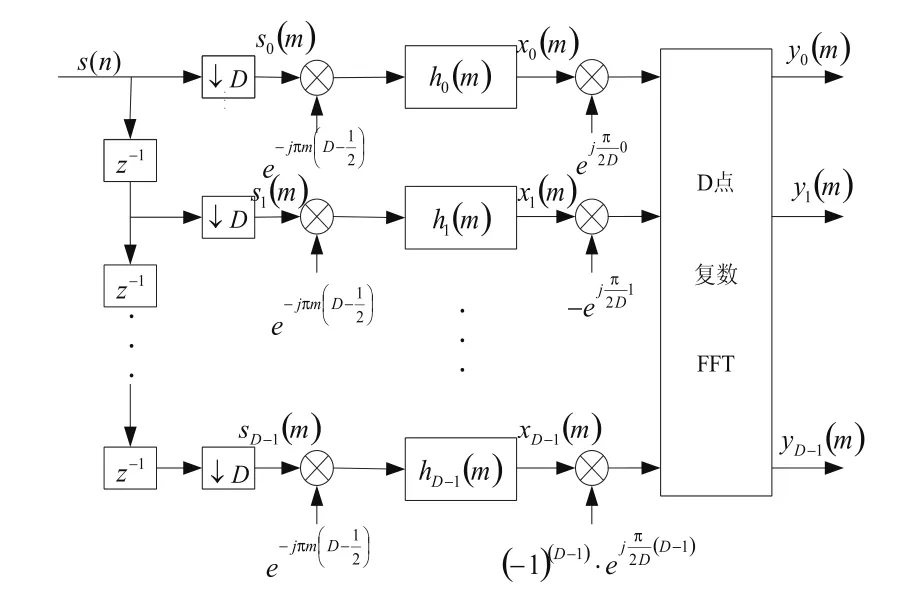

短时傅立叶变换也称为加窗傅立叶变换,是对信号时域加窗后再做傅立叶变换求信号的局部谱,其定义为:

其中ω*(m-n)为时间窗;m为时间窗的延迟参数。信号通过滤波器组,可以看成信号与此滤波器组的卷积,即每个频率分量均为信号与某个相应滤波器的卷积结果,即采用FFT方法实现该种滤波器组。短时傅立叶变换是通过矩形滑动窗去截取采样信号,窗长度为N,对截取后的信号进行FFT。当输入数据率与输出数据率相同时,每输入数据滑动一点,则做一次FFT,其输出为

图2 短时傅立叶变换信道化结构

根据短时傅立叶变换推导可以得到该信道化结构如图2所示。

从结构实现角度看,同样可采用基于多相滤波的方法和结构,只是需要用窗函数代替其中的补零滤波器,基于STFT的方法具有灵活性,只要输出数据率满足带宽要求,输出数据率便可灵活改变,而多相滤波结构输出数据率只能为信道宽度的F倍。但是就硬件实现来说,这种方法不能用同一个时钟工作;而多相滤波结构方法可以用同一个时钟工作,易于实现。

2 系统设计与实现

2.1 系统设计指标

数字信道化设计指标如下:

1)采样率:0.8GHz;

2)无模糊带宽:400MHz;

3)子信道数:8;

4)滤波器阻带衰减:≧60dB;

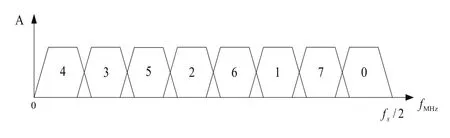

针对以上设计指标,本设计采用了ATMEL公司模数转换器AT84AS003,采样精度10Bits,最高采样率1.5Gsps,FPGA采用了ALTERA公司StratixII系列EP2S60芯片。数字信道化在FPGA内部实现,选择多相滤波结构模型。根据无模糊带宽400MHz、子带数目为8,可知子带宽度为50MHz。按照实信号信道化分结构,实信号滤波器组划分结构如图3所示。

图3 实信号滤波器组信道划分

2.2 系统实现

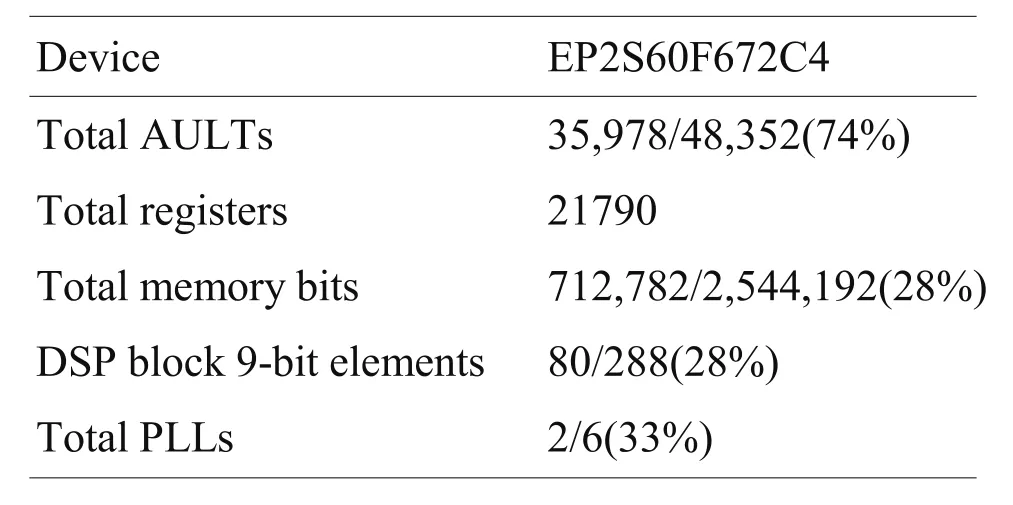

根据多相滤波结构,原型滤波器按照通带频率25MHz,截止带频率30MHz,阻带衰减60dB设计,原型滤波器阶数为316阶。考虑到该芯片乘法器资源有限,为了减少乘法器的使用,该部分采用分布式算法实现FIR滤波,无需占用乘法器资源。复系数乘法和8点复数FFT采用乘法器实现。表1给出了FPGA实现该数字信道化接收机系统资源占用情况。

表1 系统FPGA资源占用情况

3 系统仿真

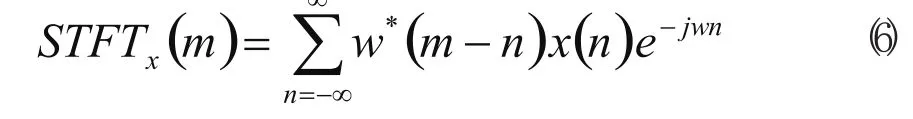

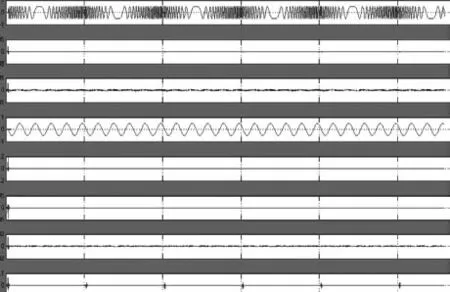

输入信号分别为正弦信号和LFM信号,具体参数如下:正弦信号频率89MHz;LFM信号:中心频率443MHz,调制带宽6MHz。仿真结果如图4所示。

图4 各子带信道输出结果

从仿真结果可以看到:LFM信号出现在信道0,正弦信号出现在信道3。对照图2所示的信道划分结构,可知该仿真结果与实际信道划分结构相符,信道化输出结果正确。

4 结论

本文介绍了一种数字信道化高效结构的FPGA实现方法,分别对多相滤波结构和短时傅立叶变换结构两种信道化技术进行了分析对比。设计了一个实际的数字信道化系统,并通过系统仿真和实际系统测试,验证了该数字信道化结果的正确性。由于该数字信道化基于软件无线电设计思想,对于不同的技术指标和系统,只需改变部分软件程序即可实现,因此具有一定的通用性和实用价值。

[1] James Tsui.宽带数字接收机[M].北京:电子工业出版社,2002.

[2] Zahirniak D.R,Sharpin D.L,Fields T.W.A.hardwar-eefficient,multirate,digital channelized receiver architecture[J].Aerospace and Electronic Systems,IEEE Transactions on.Volume 34,Issue 1,Jan.1998 Page(s):137-152.

[3] 杨小牛,楼才义,徐建良.软件无线电原理与应用[M].电子工业出版社,2001.

[4] HARRIS F,DICK C,RICE M.Digital receivers and transmitters using polyphase filter banks for wireless communications[J].IEEE Transactions on Microwave Theory and Techniques,2003,51(4):1395-1412.

[5] 张文旭,司锡才,孙强毅.一种高效信道化接收机设计与实现[J].电子技术应用,2008.11.

[6] Maharatna,K.;Banerjee,S.;Grass, E.;Krstic, M.;Troya,A.Modified virtually scaling-free adaptive CORDIC rotator algorithm and architecture[J].Circuits and Systems for Video Technology,IEEE Transactions on.Volume 15,Issue 11,Nov.2005 Page(s):1463-1474.

[7] Gruciiala,H.;Slowik,A.The complex signals instantaneous frequency measurement using multichannel IFM systems[C].