自主可控EDA 金光SPICE 的技术特点及应用方法研究

余 菲,曹志强

(1. 深圳职业技术大学 电子与通信工程学院;2. 深圳职业技术大学 集成电路学院,广东 深圳 518055)

一、引言

集成电路是由半导体材料制成的微型电子器件和互连线路,是信息技术的基础,对于国家经济发展和国防安全具有重要意义[1-2]。集成电路设计分为前端设计和后端设计两个部分,需要用到EDA(electronic design automation,电子设计自动化)工具[3]。EDA 工具是集成电路设计的核心要素,能够提高芯片设计效率和质量,降低芯片设计成本和风险[4]。

目前,全球EDA 市场由美国三家公司垄断[5],分别是Synopsys、Cadence 和Mentor Graphics,它们占据了90%以上的市场份额。国产EDA 软件虽然在低端芯片设计领域有一定市场份额,但在高端芯片设计领域还难以与国际主流产品竞争[6],主要原因是缺乏核心算法、缺乏工艺支持、缺乏生态建设等。因此,加快国产EDA 软件的发展,突破关键技术瓶颈,提升自主可控能力,是我国集成电路产业发展的迫切需求[7]。

金光SPICE是一款由深圳职业技术大学设计并公开发布的国产自主可控的集成电路EDA 产品,能够支持纳米级先进工艺模型,实现晶体管级的高精度仿真,成本远低于同类国际主流产品。SPICE( Simulation Program with Integrated Circuit Emphasis)是一种用于模拟电子电路行为的通用仿真算法[8],Synopsys、Cadence 和Mentor Graphics都分别推出了相应的SPICE EDA 软件:HSPICE、Spectre 和TSPICE。开发和应用自主可控的EDA,深入研究相应的设计方法,有助于提升国产EDA软件的应用水平和市场竞争力[9-10],助力我国集成电路产业发展。

二、金光SPICE 的主要技术特点

金光SPICE的基本原理是基于SPICE仿真程序的核心算法,即修正节点分析法(Modified Nodal Analysis,MNA)[11],将电路中的所有元件和节点用线性方程组表示,然后利用数值方法求解方程组,得到电路中各个节点的电压和电流。金光SPICE 还采用了多种优化技术,如多层次仿真、多线程并行计算、自适应步长控制等,提高了仿真的速度和精度。自主可控EDA 金光SPICE 技术相对于其他国际主流EDA 技术有以下特点:

(1)支持纳米级先进工艺模型,如BSIM3、BSIM4、BSIM5[12]等,能够实现晶体管级的高精度仿真。

(2)设计了非常易用的电路图编辑器,快速地将电路图及相关的仿真控制转化为SPICE网表,并且完全兼容电路级仿真工具HSPICE 的模型语法及自定义语法。

(3)独创了“仿真控制虚拟器件”,可以直接在属性页面添加仿真类型、温度及精度控制等,并设置器件默认模型参数,方便使用者进行功能定性仿真。目前有4 种仿真类型,分别是瞬态仿真、静态工作点仿真、AC 仿真、DC 扫描以及温度仿真。

(4)IP 引入功能:金光SPICE 可以支持私人定制模块,也就是IP(Intellectual Property)的引入。可以将设计好的定制模块直接引入系统,无需二次制作,便捷地实现工程项目管理功能以及层次化调用功能。例如,如果有一个设计好的运算放大器模块,可以将其保存为一个.asc 文件,然后在电路图中添加一个Hierarchical Block 虚拟器件,最后在属性页面中指定该文件的路径。

(5)X 器件功能:金光SPICE 还独创了一些特殊的器件,如变压器、自定义器件等,并可以在电路图中添加一个X Symbol 虚拟器件,然后在属性页面中指定该子电路的名称和SPICE代码,实现自定义特殊器件。

三、基于自主可控EDA 金光SPICE 的集成电路设计实例

(一)反相器链的电路设计与分析

反相器链是由多个反相器串联组成的电路[12-13],反相器链结构如图1 所示。它可以实现信号的放大和反转[14]。反相器的面积越大,驱动能力越强,但是也会增加其寄生电容,从而影响其延时。因此,在设计反相器链时,不能只考虑负载电容对最后一个反相器延时的影响,还要考虑输入电容对前面各个反相器延时的影响。为了优化反相器链的性能和功耗,一种常用的方法是采用逐级递增的尺寸比例,使得每个反相器的延时都接近于最小值。在确定尺寸比例时,需要综合考虑各个反相器的电源电压和反相器尺寸、工艺参数、噪声容限等因素,以达到最佳的设计效果。

图1 反相器链基本结构

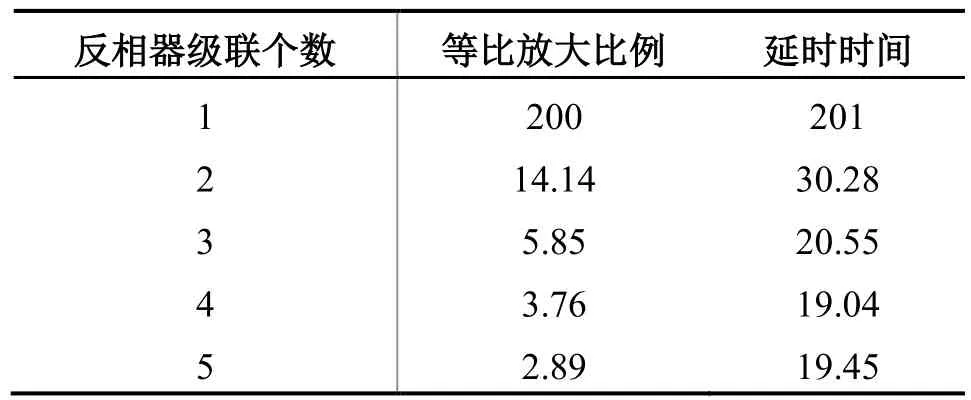

假设现在要用反相器链来驱动20pF 电容负载,反相器数量最少,延时时间最小,输入电容负载为0.1pF。根据以下公式得出一组数据如表1 所示。

表1 反相器级联个数与延时时间的关系

当反相器连续4 个级联时,每组等比放大3.76倍,延时最小时间为19.04ns。根据以上的参考数据,利用金光SPICE 设计了一个反相器链电路,如图2所示。

图2 级联四组反相器链

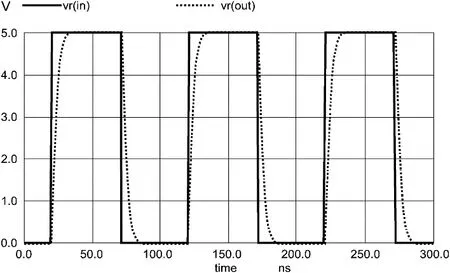

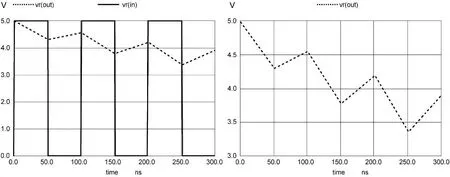

在此电路中,输入电容负载为0.1pF,输出要驱动20pF 电容,四组反相器的沟道长度都为0.25u,每组反相器中后一级PMOS 管是前一级的PMOS 管的二倍W,使用的是TT 工艺角,每组反相器都等比放大3.8 倍左右,基于金光SPICE的仿真波形图如图3 所示。

图3 反相器链仿真结果

从结果来看,电压的转换时间不是太理想,特别是输出时高电平转低电平比较慢,没有达到预想的结果。调节MOSFET 的宽长比可以调整Req,以达到调整CMOS反相器的传输延时的效果。即:

λ 为沟长调制效应系数。此时电路的性能最佳,无论是传输延时间还是转换时间都达到了预想值。最终把每组mos管的W/L比值改成了1:1;后一级的反相器是前一级的3.8 倍,才得到最佳的结果,如图4 所示。

图4 调整之后的反相器链仿真结果

(二)施密特触发器电路设计与分析

施密特触发器[15]是一种常用的波形整形电路,它有两个重要的特点:一是它有两个不同的阈值电压,可以防止噪声干扰电路的正常工作;二是它有正反馈作用,可以使输出波形的边沿变得很陡,提高信号的质量。

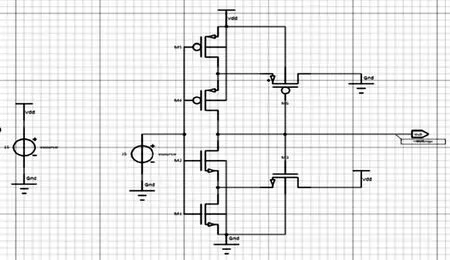

电源电压VDD=5V,低转换点电压VSPL=2V、高转换点电压 VSPH=3V,阈值电压值约为VTHN≈0.6V,VTHP≈0.7V,设计施密特触发器并仿真出施密特触发器传输特性,设计出的结果要满足低转换点电压VSPL 在1.4-1.6 V 范围内、高转换点电压VSPH 在3.4-3.6V 范围内。

图5 施密特触发器电路图

图6 施密特触发器特性仿真结果

最终测得低转换点电压VSPL不在1.4-1.6 V范围内、高转换点电压VSPH 不在3.4-3.6 V 范围内。

解决方案就是当M3 的宽长比增加时,等效电阻相应减小,输入电压就要增大;当M6 的宽长比增加时,等效电阻相应的减小,输入电压就要减小;总的来说M3 和M6 的宽长比越大,停滞效果越好。此时M3和M6 的宽长比为L=0.5u,W=5u。调整过后的仿真结果如图7 所示。

图7 调整过后的施密特触发器特性仿真结果

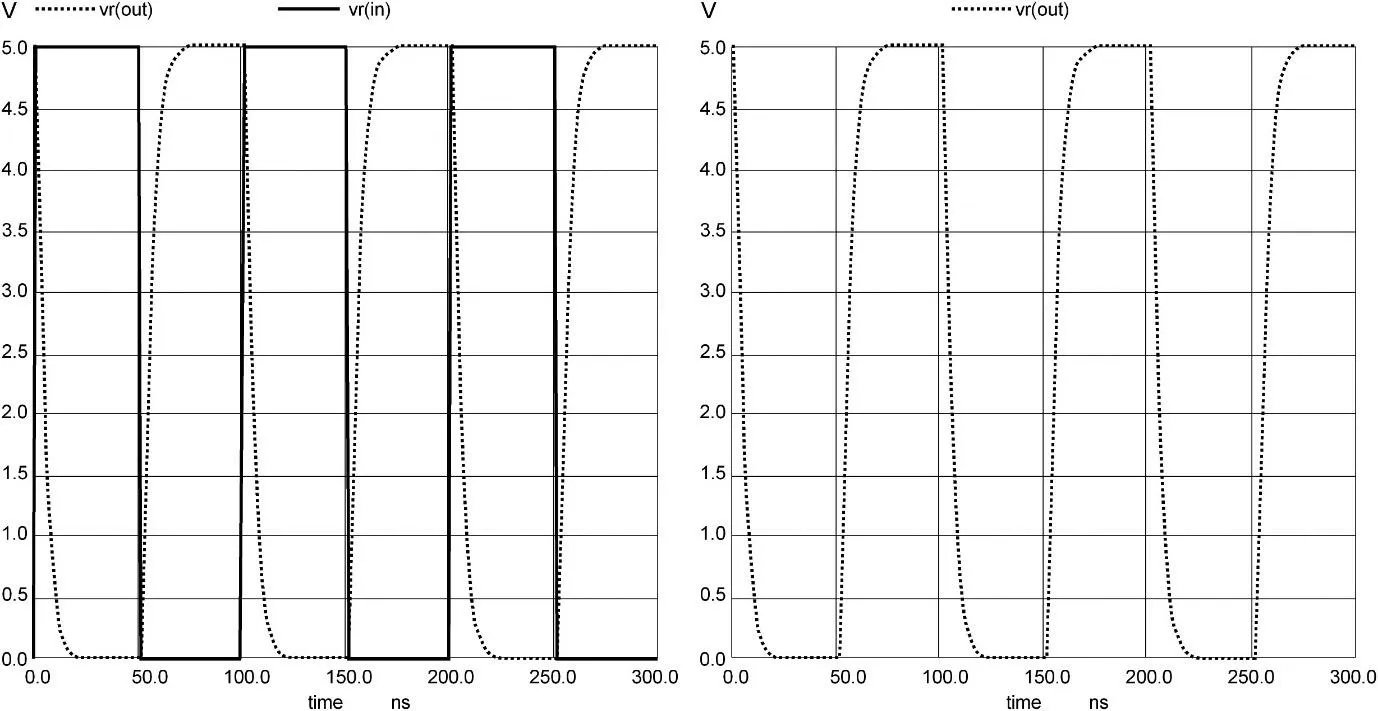

根据上面已经设计好的电路,在输出端加一个20pF 的电容负载。为了提高输出信号的上升沿和下降沿的速度,以及减少输出信号的延迟。上升和下降时间要减到最小。确保测量的上升和下降时间tr、tf 在大于6ns 小于10ns 范围内。仿真结果如图8 所示。

图8 施密特触发器时序仿真结果

从结果来看,电容放电和充电很缓慢,电压上升升不到VDD,下降降不到GND;为了改进结果,施密特触发器驱动大负载电容时,需要增加六个MOS 管的宽长比,增加MOS 管的电流驱动能力,以及减少MOS 管的开关阻抗。调整后的结果如图9 所示。

图9 调整过后的施密特触发器时序仿真结果

最佳设计尺寸为M1 和M5 的宽长比为L=0.25u,W=25u;M4 和M2 的宽长是M1 的二倍;M3 的宽长比为L=0.25u,W=36.2u;M6 的宽长比为L=0.25u,W=32.9u。

当施密特触发器驱动大负载电容时,意味着输出端连接了一个很大的电容器,这会增加输出端的寄生电容,从而影响输出信号的上升沿和下降沿的速度,以及输出信号的延迟。为了提高输出信号的质量,需要增加六个MOS 管的宽长比,这样可以带来两方面的好处:

(1)增加MOS 管的电流驱动能力。当MOS管导通时,它相当于一个电阻器,其阻值与宽长比成反比。因此,增加宽长比可以降低导通电阻,从而增加通过MOS 管的电流。这样可以更快地给负载电容充放电,提高输出信号的上升沿和下降沿的速度。

(2)减少MOS 管的开关阻抗。当MOS 管截止时,它相当于一个开关,其开关阻抗与宽长比成正比。因此,增加宽长比可以提高开关阻抗,从而减少漏电流。这样可以更好地保持输出信号的稳定性和准确性。

四、结论

自主可控集成电路EDA 是我国信息技术自主可控领域的核心技术。金光SPICE 实现了集成电路SPICE工具的完整功能,具有高速、高精度、高效率、高可靠性、高兼容性等特点,能够满足不同类型、不同规模、不同工艺的集成电路设计需求,提供完善的电路图编辑、仿真分析、优化验证等功能。

金光SPICE 内部提供大量的教学资源、案例和模型,支持与其他EDA 工具的数据交换和互操作。本文利用金光SPICE 完成了反相器链和施密特触发器的设计,比较了它们在驱动20pf 的电容时的性能差异。结果表明,施密特触发器具有更好的抗噪声能力和更快的响应速度,适合用于信号整形和缓冲等场合。反相器链则具有更低的功耗和更小的面积,适合用于信号反相和放大等场合。

上述研究证实,基于金光SPICE 的集成电路设计方法能够有效地提高集成电路设计的质量和效率,降低设计的成本和风险,具有较强的实用价值和推广意义。