大电荷处理能力红外探测器读出电路像素设计

杨斯博,李敬国,袁 媛

(中电科光电科技有限公司,北京 100015)

1 引 言

焦平面红外探测器的核心是如图1所示的探测器阵列与读出电路倒装互联在一起的混成芯片,其工作原理是探测器阵列在视场内受到特定波段的红外光激发,每个像素单元产生微弱的光电流,这些电流通过铟柱流入或流出与之相对应的读出电路的像素级,通过时序的控制,在像素级的积分电容上产生与光电流相应的电压信号,然后读出电路按序输出给后端采集系统成像。作为红外探测器的重要组成部分,读出电路的性能指标对红外探测器的总体成像质量有着直接的影响。随着红外探测器技术的发展,读出电路逐渐往更大的规模阵列和更小的像元间距突破以获得更细腻的成像质量,这也造成像素的像元面积被进一步压缩,积分电容的布局受到限制,提高了像素的设计难度。[1]

2 读出电路电荷处理能力与红外探测器性能的关系

动态范围(DR)和噪声等效温差(NETD)是衡量红外探测器灵敏度的主要指标,在20 ℃~35 ℃温差条件下,根据NETD的计算公式:

(1)

NETD为温差与信噪比SNR的比值,SNR计算公式如下:

(2)

其中,Nph是光子噪声电子数,按下面的公式获得:

(3)

Ndark是暗电流噪声电子数,依下列公式求得:

(4)

NR是由固定图形噪声、热噪声、1/f噪声、KTC噪声等组成的读出电路的噪声。

由于本探测器需要在110 K这个相对较高的温度下工作,探测器的暗电流会随着工作温度的升高而迅速增大,从而对探测器的最终信噪比造成严重影响,从而造成NETD数值升高,成像质量不佳。从读出电路着手考虑,需要在读出电路噪音中需要将KTC噪音降到最低。

KTC噪声是像素单元因复位动作而产生的一项噪声,其表达式为:

Vn=(KT/CP)1/2

(5)

Cp是前置放大器输入端电容,是包括输入级积分电容的节点全部电容值总和。[2]

从设计的角度考虑减小KTC噪声,CP作为分母项,我们可以通过设计尽可能大的积分电容达到减小KTC噪声的目的,电路的积分电容越大,KTC噪声Vn就会越小,相应的红外探测器性能指标也会越好。

3 大电荷处理能力像素单元设计

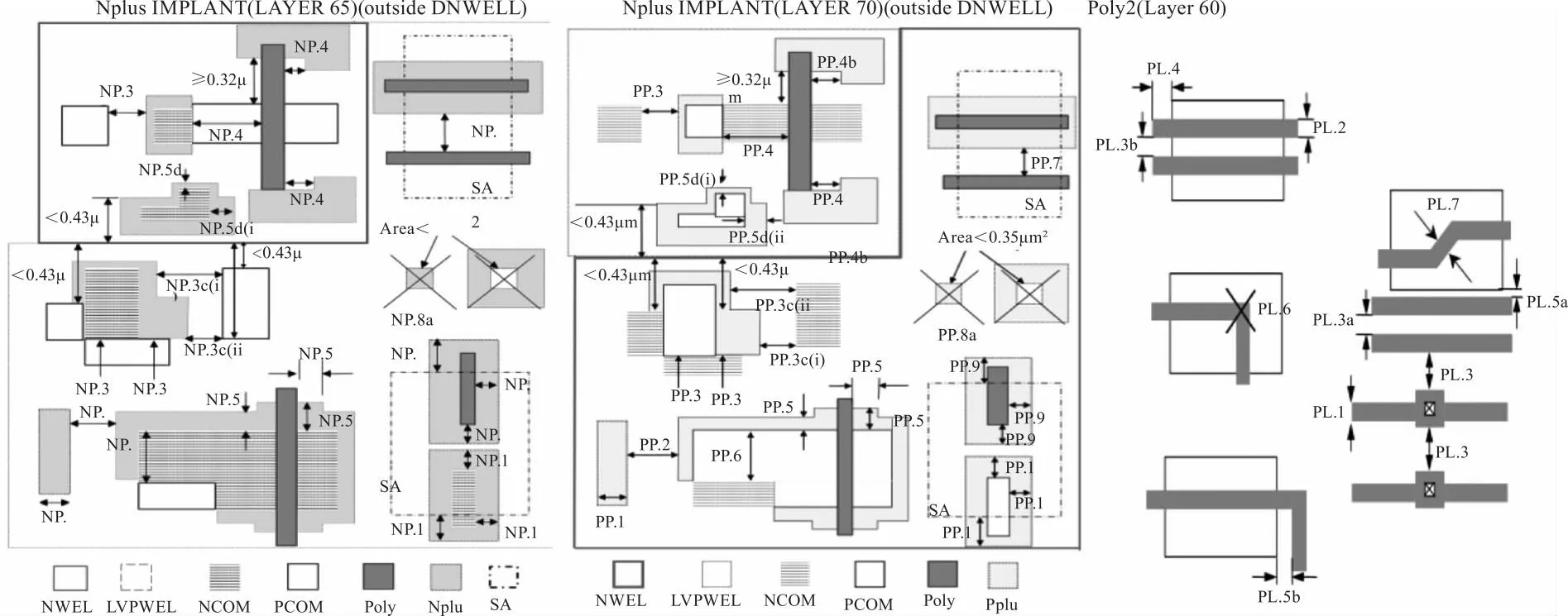

电路的积分电容布置在像素单元内,一般采用MOS电容设计,其单位面积电容密度较大。版图设计要遵守符合半导体集成电路制造可靠性的最小的设计规则(Design Rule),图2列举出一些版图设计规则。

为了能够保证高中化学分层教学能够发挥出应有的作用,不断地提升高中化学教学水平以及学生的化学综合能力,相关的教职人员在实际教学的过程当中必须要对教学目标进行准确的分层处理。只有在明确的教学目标下,相关的高中化学教职人员才能够顺利的开展分层教学,进而实现既定教学目标。

图2 0.18 μm工艺设计规则

设计规则中构成的MOS管的金属和金属、多晶硅与多晶硅,N阱与NMOS之间有严格的距离限制,违反这些规则可能导致制造工艺失败从而引起电路失效。由于本款电路像元中心间距仅为15 μm,因此在非常有限的像素区域内很难布置出大的积分电容,这对像素单元的版图设计是不小的挑战。本次设计采用如下三个方法提升像素的积分电容。

3.1 输入级结构选型

读出电路像素的输入级直接通过铟柱与探测器相连,常用的输入级结构主要有以下几种:自积分(SI)、直接注入型(DI)、源跟随器型(SF)、电容跨导放大器结构(CTIA)等,各种结构在噪声、占用面积等方面各有优劣[3],性能对比见表1所示。

表1 各种输入级结构性能对比

本次设计选择DI搭配SF的像素级结构,这种结构在噪声表现、线性度和占用面积方面均有不错的表现,其典型结构如图3所示。

图3 输入级结构

在这种结构中,CK_INT连接的是GPOL管,可以为探测器提供稳定偏压,使探测器工作在反偏区。RSTB_INT是积分电容的复位管,当高电平脉冲时,MOS管开启,积分电容C1被复位。开关管GAIN连接电容C2,可以做增益切换使用,开启时电容C2并入积分电容。开关SH是采样开关,这个设计使得电路具备IWR工作模式,在IWR模式下,C1/C2作为积分电容,C3 作为采样电容,在ITR模式下SH常开,C1、C2、C3并联。RSTB_SH是采样电容C3的复位管,原理同RSTB_INT。SF管作为为多路传输器提供电压信号并增加驱动能力的源跟随器使用。在行选管RS被选通时,源随输出电压输出至列总线上。DI结构输入级在各项指标表现均衡,并且结构十分简单,较少的占用面积可以腾出更多的空间布置积分电容,于是我们采用DI结构用做输入级结构[4]。

3.2 优化MOS电容设计

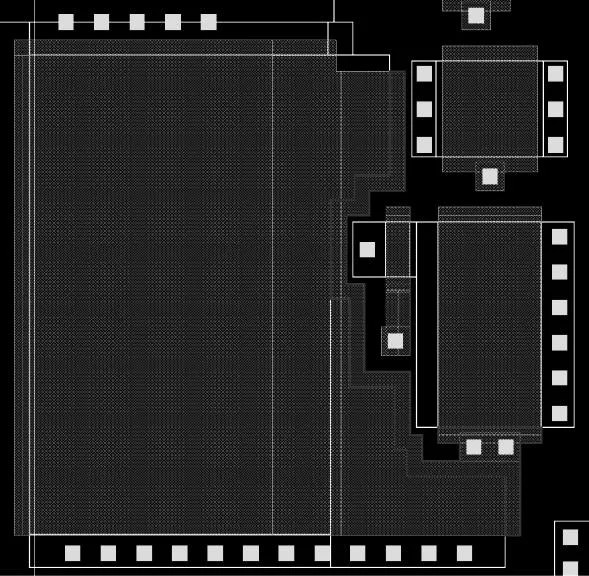

集成电路版图设计一般调用PDK(Process Design Kit)中标准的MOS器件,通过设置宽、长参数以及插指数便可直接得到MOS器件的版图图形,如图4所示。这种方法十分方便,缺点是这样调用的MOS器件均是规整的矩形,无法充分利用像素面积。采用自定义设计的积分电容MOS器件,手动按层绘制,可以设计出不规则图形的MOS器件,通过细微调整,在满足DRC规则的前提下,可以充分利用像素空间,优化后的MOS电容如图5所示。

图4 典型PCELL MOS器件版图

图5 自定义设计MOS器件版图

根据版图LVS的提取结果,采用自定义设计的MOS器件有效栅氧面积达到148.76 μm2,而采用PCELL设计的积分电容面积仅为127.8 μm2,采用自定义设计的MOS器件相较于PCELL电容值增大16 %。

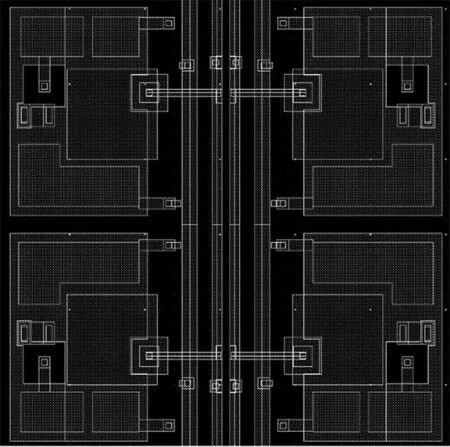

3.3 采用立体垂直式MIM电容叠层设计

多层金属布线集成电路工艺的金属与金属之间通过绝缘钝化层隔离,在两层导体之间夹杂绝缘介质的结构形成了天然的电容器,这种电容器称为MIM电容器,结构如图6所示。像素单元中的积分电容采用MOS管的栅氧化层电容,但是受像素单元面积限制不能做的很大。MIM电容结构在集成电路后道工艺中制作,不占用MOS器件结构的面积,在底层的MOS电容无法再增大的情况下,可以在MOS电容上方并联叠加MIM电容,充分利用像素单元纵向空间结构,达到增大积分电容的目的。

图6 MIM电容器结构剖面图

因为MIM电容的上下极板均为金属,在进行版图设计时要综合考虑贯穿像素阵列的横向和纵向信号线,预留走线空间。还要在数字信号线与敏感模拟节点间布设屏蔽金属层,避免数字信号对模拟节点通过寄生的干扰。经过几十种布线方案的迭代,最终确定叠加MIM电容的尺寸分别为11 μm2、25.25 μm2、8.09 μm2,按照其电容密度2 fF/μm2计算,最终MIM电容大小分别为22 fF、50.5 fF、16.18 fF。像素中并联叠加的MIM电容如图7所示,其中METALTOP为MIM电容的上极板,METAL5为MIM电容的下极板。像素设计最终的完整版图如图8所示。

图7 像素中并联的MIM电容

图8 像素单元完整版图

按NMOS电容密度5 fF/μm2计算,电路在ITR工作模式下,最大积分电容达到832.48 fF,按照正常输出摆幅2.1 V计算,根据公式:

Q=C·V

(6)

计算得出电路的最大电荷处理能力达到10.92 Me-。

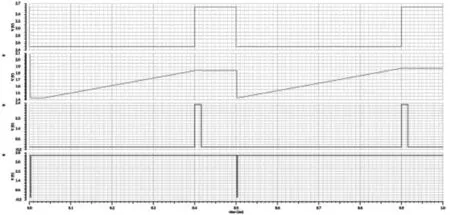

4 读出电路设计仿真结果

使用ADE软件对电路进行模拟仿真,仿真积分时长设置为400 μs,仿真结果如图9所示:

图9 像素单元控制信号与积分电压仿真结果

像素单元在CKINT_MP波形的低电平期间积分,积分电容上的信号电压VINT随着积分时间的增加而线性增加。在积分完成后行选信号RS变为高电平开启,积分得到信号得以向后级传输。RST_INT作为积分电容的复位开关,在下一帧动作开始前置为低电平将积分信号复位,为下一帧积分做准备。

仿真相同积分时间、相同激励条件下一款15微米中心距积分电容为485 fF的读出电路做对比,如图10所示,可见具备大带电荷处理能的读出电路积分斜率更低,相同激励条件下更不容易达到饱和电平。

图10 与小电容读出电路仿真对比

对像素单元进行扫描仿真,设置探测器电流范围0~4.5 nA,步长0.5 nA,仿真电路输出电压值与激励电流对应情况,如图11所示。

图11 仿真不同激励下的积分电压结果

对仿真结果总结并计算出每个步长下电压变化量见表2。

表2 ITR线性度仿真值

将上述数据列表做曲线,得方程y=0.4567x+1.4347,R2值为0.9815,如图12所示。

图12 ITR模式线性度仿真计算

由图12可知,仿真值与拟合曲线对应的值最大绝对偏差小于4 mV,输出最大范围为2.1 V,因此,非线性度小于0.2 %,读出电路工作正常,符合设计预期。

5 结 论

本文论述了红外焦平面探测器读出电路电荷处理能力对探测器NETD的影响,针对减小读出电路KTC噪声,设计了一款小像元间距大电荷处理能力读出电路,电路设计通过采用DI输入级结构、优化设计MOSCAP和并联叠层MIM电容三种方法,提升了像素单元积分电容值,最终使读出电路实现了在ITR模式下10.92 Me-的电荷处理能力。经过仿真验证读出电路可以正常工作,且I-V线性度良好。