功率VDMOS器件辐射效应研究进展

张玉宝,魏亚东,杨剑群,3 ,蒋继成,姚钢,李兴冀

(1.黑龙江省原子能研究院,哈尔滨 150086; 2.哈尔滨工业大学材料科学与工程学院,哈尔滨 150001; 3.哈尔滨工业大学重庆研究院,重庆 401120)

0 引言

垂直型双扩散金属-氧化物-半导体晶体管(VDMOS)具有控制电路简单、安全工作区宽、输入阻抗高、驱动能力强、热稳定性好、工艺流程短等诸多优点,作为功率变换及转换功能的主要器件,大量应用于不间断电源、汽车电气、空调变温及AC/DC转换器等电子系统,为电子系统的正常工作提供能源[1]。对VDMOS器件辐射损伤进行机理分析,构建定量评价模型,验证评估方法,发展器件加固技术,促进其在航空航天及宇宙探索领域中的发展,这已成为学者们关注的焦点。

目前,功率VDMOS器件的辐照效应加固研究在抗瞬态剂量及剂量率、累积剂量及位移缺陷等方面取得了突破性的进展。加固措施在抗瞬时剂量率方面令器件扰动不发生烧毁,在数十微秒恢复Si计数的等效剂量率为2×109Gy/s。在抗累积剂量加固方面,器件导通电阻及开启电压等参数变化量在30%以内的Si计数辐射总剂量为1×104Gy,在抗位移缺陷加固方面,器件的源-漏电流、导通电阻及正向跨导等参数均未见明显变化的中子辐射通量为1×1014n。功率VDMOS器件在抗瞬时剂量/剂量率、总剂量及中子辐射等方面的突出表现使其广泛应用于核能、核弹存储等电子系统中。本研究针对VDMOS器件的工作特性、辐照效应及抗辐射加固研究,梳理其空间辐射效应研究现状及抗辐射加固手段,基于工艺条件的不断优化,提高VDMOS抗辐照能力,为研发抗辐射系列的VDMOS产品奠定基础。

1 VDMOS器件的基本结构与工作特性

VDMOS器件相对于传统MOS器件具有独特的设计,其漏极位于芯粒单元底部,采用杂质双扩散技术是设计的关键,通过掩膜遮挡及两次扩散过程形成了横向浓度差,从而建立器件沟道。沟道设计是VDMOS器件的重要方面,采用垂直导通电流的方法,可有效提高硅片利用面积,为器件性能优化提供可能性,使其在电流导通方面具有更高的效率。N型沟道VDMOS器件的基本结构可分为两部分,即元胞区和终端区。元胞区由多个元胞并联构成,这种并联设计有助于增加导通电流,提高器件的整体性能。终端区包含场板、终端结、场限环等结构,可显著提高器件的击穿电压,增强其在高电压环境下的稳定性[1]。图1是N型沟道VDMOS器件的基本结构,突出了元胞区和终端区两部分,有助于理解器件的内部结构及各部分的作用。VDMOS器件设计提高了硅片利用率及击穿电压,对于集成电路的制造具有重要意义,为高性能电子器件的发展及制造提供了有力支持。

VDMOS器件的工作原理主要体现在开关功能,通过调节栅极电压的大小来控制器件内沟道电流的大小,通过调整栅极电压,VDMOS器件能够在沟道内建立或切断电流通路,从而实现开关功能,故VDMOS器件属于一种电压控制电流型的器件。根据沟道的掺杂类型分为两类,即N沟道VDMOS器件与P沟道VDMOS器件,这一区分主要基于沟道中的载流子类型。N沟道VDMOS器件中的沟道主要由电子负责传导电流,而P沟道VDMOS器件中的沟道则主要由正电荷(空穴)负责。还有一种分类是基于器件的开启方式,即根据VDMOS器件的工作状态分为增强型VDMOS器件和耗尽型VDMOS器件。增强型VDMOS器件在正常工作条件下需外加正向栅极电压才能形成有效的沟道,而耗尽型VDMOS器件则是在正常工作条件下已经具有形成有效沟道的能力。VDMOS器件凭借其电压控制电流的特性为电子器件设计及电路应用提供了多样化选择。

N沟道增强型VDMOS器件的工作原理是基于栅极电压的调控实现开关功能。在关断状态下,当栅极电压为0 V时,P体块区沟道未形成反型,导致导电沟道无法在器件表面形成,因此漏极与源极之间电流很小。但当栅极电压大于阈值电压时,N型导电沟道在器件表面形成,使得漏极与源极之间导通,实现了器件的开启。这个过程是通过栅极电压的变化来控制的,栅极电压的增加使器件逐渐从关断状态转变为导通状态。输出特性曲线是评估VDMOS器件性能的重要工具(如图2所示),反映了在固定栅极电压下随着漏极电压的增大,器件从关断到开启的转变过程。这些曲线通常分为线性区、饱和区、截止区、击穿区、准饱和区等工作区域,每个区域对应着不同的工作状态和电流特性,有助于深入理解器件行为。准饱和区是VDMOS器件独有的输出特性区域,在这个区域,随着栅极电压(VGS)的增加器件的漏极电流不再呈线性增长,而是趋于饱和,这一特性使得VDMOS器件在特定工作条件下表现出独特的电流响应,具有一定的应用优势。输出特性曲线反映了器件在不同工作状态下的电流特性,而准饱和区则为其提供了独特的电流响应特性。

图2 VDMOS器件输出特性曲线和工作区域划分Fig.2 VDMOS device output characteristic curve and working area division

2 VDMOS器件的总剂量效应研究

总剂量效应对MOS场效应晶体管的影响体现在多个方面,包括阈值电压的漂移、漏极电流的增加、迁移率及跨导的下降等重要效应。这些影响因素主要源自器件长时间暴露于辐射环境下所引起的电离效应。

电离辐射效应对阈值电压变化的影响是影响MOS场效应晶体管的关键因素之一。阈值电压是器件进入正常工作状态所需的起始电压,而电离辐射会导致阈值电压发生变化,从而影响器件的工作状态及性能表现。总剂量效应导致阈值电压漂移的表达式如下所示[6]:

(1)

其中,ΔVot为氧化物陷阱电荷引起的阈值电压漂移量,单位为V。ΔVit为界面态陷阱电荷引起的阈值电压漂移量,单位为V。ΔNot为总剂量效应在氧化层中产生的氧化物陷阱电荷密度,单位为cm-2。ΔNit为总剂量效应在氧化层和体材料的截面处产生的界面态陷阱电荷密度,单位为cm-2。Cox为单位面积的氧化层电容,单位为F/cm2。

图3是电离辐射效应造成的NMOS场效应晶体管阈值电压漂移量与时间的关系,可以明显看出其分为4个阶段[7,8-10]:

图3 N型VDMOS阈值电压漂移量与时间的关系Fig.3 Relation between threshold voltage drift of N-type VDMOS and time

第一阶段:空穴注入导致负向偏移,在辐照过程中,SiO2层经历了空穴注入,导致NMOS场效应晶体管的阈值电压发生负向偏移。这负向偏移的阈值电压变化引发了SiO2层内形成导电沟道的过程。

第二阶段:空穴输运导致正向偏移,随着辐照的结束,空穴在Si-SiO2界面逐渐输运。NMOS场效应晶体管的阈值电压开始逐渐正向偏移,反映了空穴在SiO2层中的运动及影响。

第三阶段:陷阱电荷形成引起正向偏移,空穴在Si-SiO2界面Si的一侧被深层陷阱俘获,转变为氧化物陷阱电荷。这种陷阱电荷的形成导致NMOS场效应晶体管的阈值电压再次正向偏移,发生了一定程度的退火现象。

第四阶段:反弹效应与电性态生成。在最后阶段发生了一种反弹效应,即带有负电性的受主态在Si-SiO2界面生成。界面态与氧化物陷阱电荷经过一定程度的退火,令NMOS场效应晶体管的阈值电压漂移到接近初始状态。这一过程反映了辐照后电性态得以修复并趋近于初始状态。

对于PMOS晶体管,图4给出了总剂量效应导致P型VDMOS晶体管阈值电压漂移量与时间的关系[11]。

图4 P型VDMOS阈值电压漂移量与时间的关系Fig.4 Relation between threshold voltage drift of P-type VDMOS and time

PMOS的阈值电压在前两阶段受到总剂量效应的影响与NMOS相似。但在第三阶段与NMOS不同,在PMOS中,氧化物陷阱电荷与界面态带正电,导致氧化物陷阱电荷的退火与界面态的生成,这一变化导致PMOS场效应晶体管的阈值电压向初始值变化,与NMOS在相同阶段的行为不同。

从VDMOS的结构上看,其内部寄生着一个NPN型晶体管。因此VDMOS对总电离剂量(TID)效应很敏感。近年来,由于机理相对较为明晰,对于总剂量效应对VDMOS影响机理的研究逐渐趋向于新结构的VDMOS器件研发及制造。

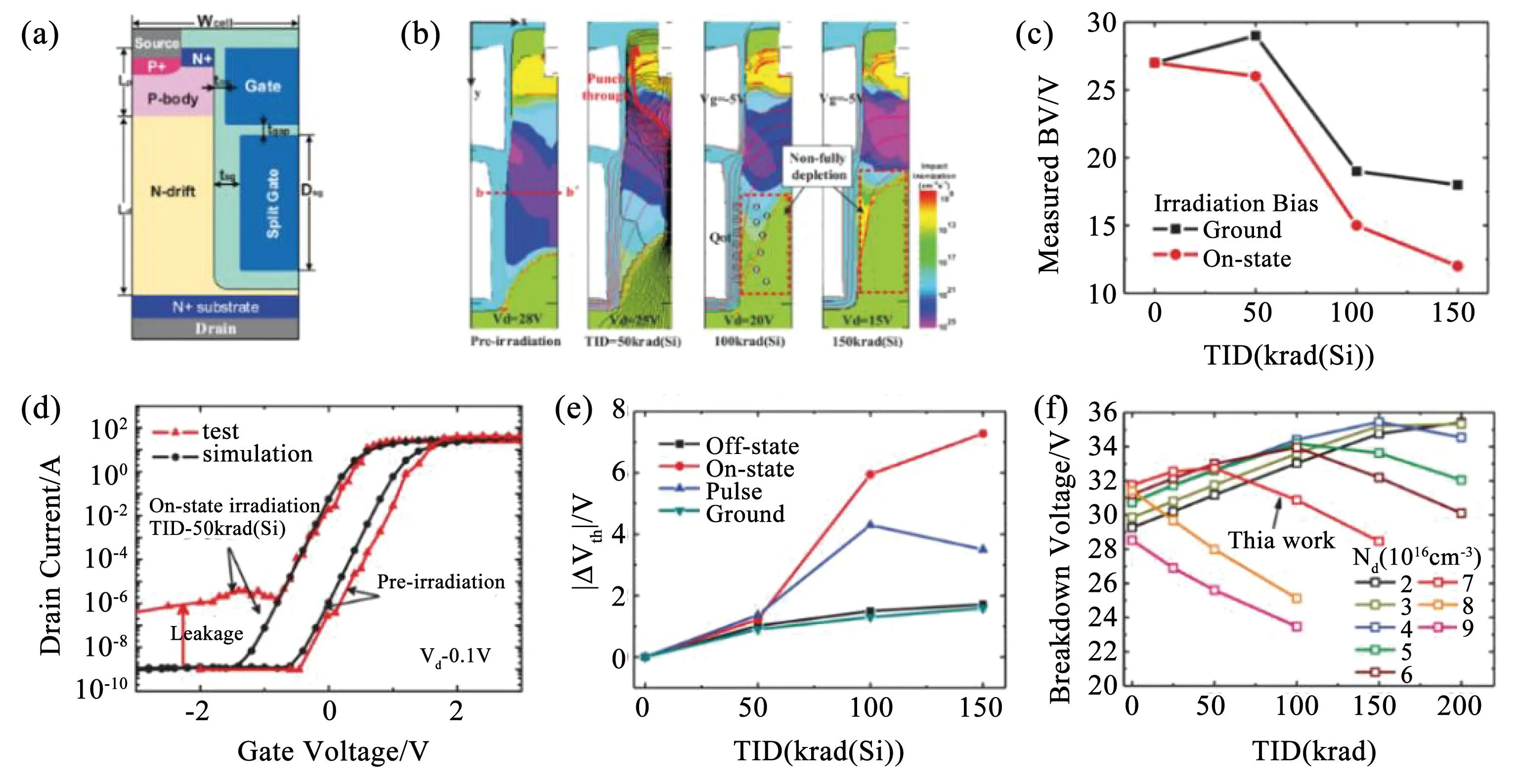

从结构设计角度来看,乔明等结合γ射线辐照试验与TCAD仿真较为系统地研究了30 V分裂栅沟槽(SGT)VDMOS中的总电离剂量效应,如图5所示[8]。相比传统的平面结构,SGT结构的工艺制造步骤引入了多重氧化与退火工艺,因此沟槽结构中的氧化物缺陷浓度较高。从阈值电压漂移的角度看,栅氧化物中的电场强度(Eox)高达0.9 MV/cm,使得很大一部分氧化物电荷转移到了界面,形成界面俘获电荷。试验中辐照后产生较大的泄露电流来源于栅极氧化物中俘获电荷造成的泄露路径。这些俘获电荷对体电场分布有很大的影响,导致击穿电压(BV)下降,在总剂量为100 krad(Si)的辐照下,BV下降到14 V。为了实现对总剂量辐照的加固,提出3种方法:通过减少退火步骤减小氧化物电荷,降低漏极的掺杂浓度,在SGT VDMOS中引入高掺杂保护区。

(a)30-V SGT VDMOS的横截面; (b)总剂量辐照下的等势面与冲击-电离产生率分布; (c)器件位于开关态下,总剂量和BV之间的关系; (d)辐照前后器件转移特性的仿真与测试结果;(e)器件位于不同偏压下,总剂量与阈值电压的关系;(f)不同的漏极掺杂浓度Nd下BV随总剂量的变化情况图5 SGT-VDMOS中的总电离剂量效应研究Fig.5 Study on the effect of total ionization dose in SGT-VDMOS

VDMOS制造过程中的温度分布、杂质扩散及注入参数不同导致工艺参数的变化,总剂量响应对工艺变化敏感,使得同一晶片(晶片内)生产的器件或同一批次(批次内)生产器件的总剂量响应不同。2023年,崔江维等通过60Co-γ射线辐照实验研究了B1500A与BC3193两类硅基VDMOS器件的批次内总剂量响应变化,如图6所示。试验结果显示,在总剂量不断增加的情况下,批次内装置参数的可变性发生变化。辐照后,阈值电压、亚阈值摆幅、输出电容与二极管正向电压的可变性增加。通过提取器件中总剂量响应辐照引起的Not和Nit,建立了参数变化与俘获电荷之间的关系,分析可知,辐照后俘获电荷的积累放大了同一批器件的工艺差异,导致器件的阈值电压、亚阈值摆幅、最大跨导、输出电容及二极管正向电压的差异。表1给出了电参数的变化与辐照后俘获电荷之间的相关性。为建立科学合理的批内器件总剂量效应评估及筛选方法、保障航天器电源系统的稳定性及可靠性奠定了基础。

表1 辐照前后电参数变化Tab.1 Changes of electrical parameters before and after irradiation

3 VDMOS器件辐照诱导退化效应的机理:单粒子效应

单粒子效应是指单个高能粒子入射后,能量被半导体器件吸收,器件体内电子从价带跃迁到导带,产生大量的电子空穴对,电子空穴对在电场的作用下漂移,使得器件状态发生改变或直接烧毁的效应。单粒子效应的发生是偶然性的,但是对半导体器件的影响是巨大的。单粒子效应包括单粒子翻转(Single Event Upset,SEU)、单粒子闩锁(Single Event Latchup,SEL)、单粒子烧毁(Single Event Burnout,SEB)及单粒子栅击穿(Single Event Gate Rupture,SEGR)等,其中 SEU是非破坏性的,可能会对整个电力电子系统造成逻辑上的错误,称为软错误,而 SEL、SEB、SEGR都是破坏性的,一旦发生会对器件产生毁灭性的打击,称为硬错误。对于单个器件来说,SEB与SEGR是需要主要考虑的单粒子效应,故功率器件的加固主要针对SEB与SEGR。

单粒子效应导致寄生三极管产生SEB[14]。在漏极正向偏置的作用下,体区产生的电势差使得寄生NPN晶体管导通,经过一定时间的重复正反馈,局部点出现集中电流束,导致该处PN结的性能减弱,令器件发生烧毁。栅极电压在SEB中具有重要的影响,L.L.Foro 等通过中子试验发现中子引发FS-IGBT(Field Stop Insulated Gate Bipolar Transistor)的烧毁。相关软件可模型仿真SEB与入射粒子位置、能量、种类的关系。

栅极位置在电子器件中容易发生SEGR现象,这是一种由入射粒子引起的栅极破裂现象。当单粒子到达栅极区域时,栅中会产生电子-空穴对,这是由于粒子与材料相互作用产生的效应。在晶体管处于正向偏置条件下,电场的作用使得空穴朝着栅极氧化物介质/硅的有源层界面漂移,并最终在该界面聚集。在假设有源层界面处积攒的空穴产生的电场达到栅极氧化物介质电场的零界值时,即使栅极氧化物介质是绝缘体,也会发生SEGR效应。SEGR的发生条件与SEB类似,与入射粒子的类型及所含能量有关,这意味着不同的入射粒子可能导致不同类型的SEGR。Javanainen Arto等提出了SEGR的半经验预测公式,其中包含辐射剂量率LET、入射粒子类型等参数,用于定量预测SEGR的可能性。一旦发生栅穿,器件将受到严重损害,栅极将表现出大电流及压降,这可能导致器件失效。

随着功率器件新结构及新材料的发展,对单粒子效应的研究也越来越多样化,除了对单粒子效应进行深入研究,人们对沟槽型器件、超结器件等新器件结构的单粒子辐射特性及新的栅介质材料对单粒子辐射的敏感性进行了大量研究。周新田等使用分段定义掺杂浓度构建了多个缓冲层[17]。在击穿电压(BV)、阈值电压(Vth)及导通电阻(RON)变化不明显的条件下,实现了更低的电场峰值与更低的碰撞电离率,从而在相同的注入位置及线性能量传递值下有更高的设定阈值电压。

图7(a)、(b)、(c)分别给出了3种器件在相同偏置条件下的SEB性能。可以看出,在注入位置=2 μm、LET=0.1 pc/μm、偏置VDS=79 V的服役条件下,尽管带均匀缓冲层的B-MOS结构泄露电流曲线变小,但是与C-MOS器件一样都出现了器件烧毁,相比之下,MB-MOS未出现烧毁现象,表现出相对较强的抗SEB能力。

(a)传统VDMOS结构(C-MOS);(b) 缓冲层VDMOS结构(B-MOS) ;(c) 非均匀缓冲层VDMOS结构(MB-MOS);(d) VDS为79 V时漏电流随时间的变化情况;(e) 入射时间为0.1 μs时,器件的电场分布图7 多缓冲层结构的VDMOS抗单粒子烧毁效应研究Fig.7 Research on anti-single particle burn-out effect of VDMOS with multi-buffer layer structure

图7(e) 显示了当入射时间为0.1 μs时,3种器件的电场分布。可以看出,在离子撞击后的瞬态过程中,B-MOS器件与MBMOS器件可提供比C-MOS器件更平滑、更小的电场分布。对于MB-MOS器件,峰值电场主要存在于器件表面,这是因为MB-MOS器件是在B-MOS器件基础上设置了不同浓度的缓冲层,结处的高电场在缓冲层中的电场损耗及不同浓度缓冲层之间的电场耗尽,在二者共同作用下提高了器件的二次击穿电压,达到了较好的抗SEB性能。

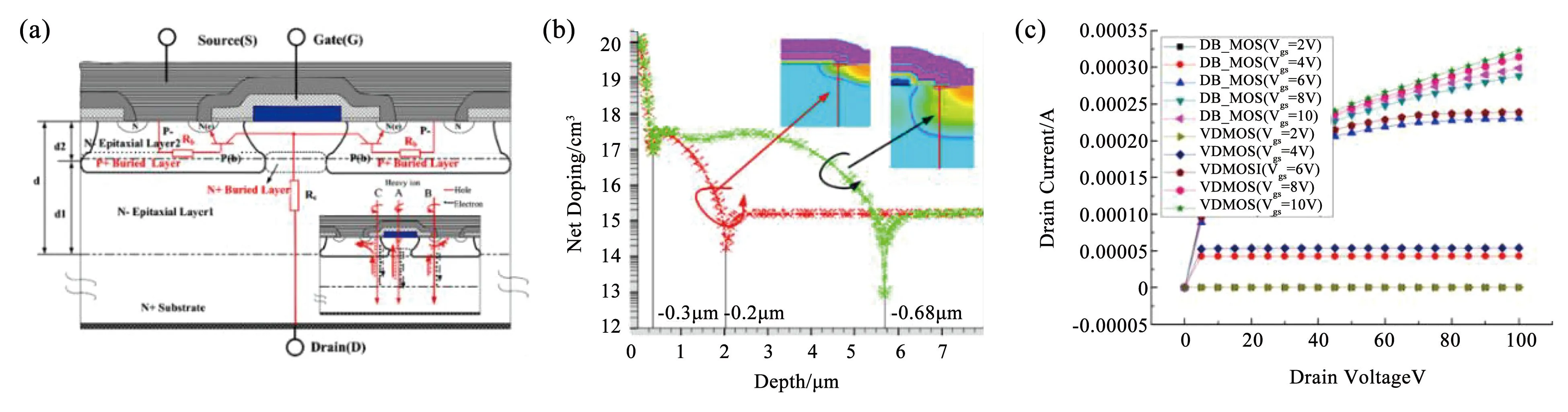

唐昭焕等针对N沟道功率VDMOS的单粒子烧毁与单粒子栅极破裂设计了一种加固结构,称为DB_MOS,如图8所示。该结构结合P+埋氧层中的复合中心与厚氧化层的高击穿电压特性,在VDMOS结构中分别设计了N+埋层、P+埋层及厚氧化层。这种加固设计极大提高了器件的抗单粒子辐射能力。结果表明,这种N沟道功率MOSFET在单粒子辐照环境下的安全工作区提高了300%,线性能量传输值为98 MeVcm2/mg。此结构可广泛应用于在空间服役环境中使用的单粒子辐照加固功率MOSFET。

(a)DB_MOS结构; (b)DB_MOS与常规VDMOS结构的寄生双极晶体管从发射极到集电极的模拟净掺杂分布曲线;(c) DB_MOS与常规VDMOS的模拟输出特性曲线图8 DB_VDMOS结构设计与抗单粒子辐射加固效果Fig.8 Structure design of DB_VDMOS and reinforcement effect against single particle radiation

4 VDMOS器件辐照诱导位移效应和剂量率效应研究

位移辐射损伤是在靶材料内由入射粒子(如质子、重离子、等高能电子)和晶格点阵原子碰撞生成。位移辐射损伤与电离效应在双极晶体管的氧化物电荷及界面造成的影响各不相同。通过对原子造成位移,形成间隙原子-空位对等缺陷损伤结构。

位移辐射对双极晶体管中的Si材料的晶格势场造成显著影响,导致整个晶体管的电性能下降。辐射损伤引起晶格结构非对称的原子弛豫,这主要是因为空穴被氧空位俘获,导致Si-Si键断裂,形成带有正电荷的氧化物陷阱电荷。一旦氧化物陷阱电荷形成,则会发生退火现象。退火程度受到时间、温度及应力等条件的影响,进一步影响了氧化物陷阱电荷的性质及分布。退火过程包括隧穿退火与热激发退火两种模式。隧穿退火通常在常温或接近常温下发生,而热激发退火需要较高的温度条件。辐照导致的氧化物陷阱电荷的退火机制是一个非常复杂的过程,涉及多种因素。图9是其中的部分情况,影响退火的因素包括温度、时间及应力等多个方面。

图9 氧化物陷阱电荷的退火 Fig.9 Annealing of oxide trap charge

由于制造工艺和晶格失配等原因,在Si/SiO2界面形成了Pb0中心,这种中心存在于特定的位置。Si/SiO2界面的界面态陷阱电荷表现出多态性,可带有正、负或中性电荷,分为类施主界面陷阱与类受主界面陷阱,这种多态性直接影响了界面的电性质。图10展示了Si/SiO2界面处的能带弯曲,这是因为在VDMOS器件的制备中对栅极施加电压改变了界面态陷阱电荷的极性,影响了能带的分布。VDMOS器件阈值电压的变化主要受到氧化物陷阱电荷与界面态陷阱电荷的影响,这两种电荷在Si/SiO2界面处的存在会直接影响器件性能。氧化物陷阱电荷相对较快地建立,而界面态陷阱电荷的建立则需要一定的时间,说明在器件运行过程中氧化物陷阱电荷的影响可能更迅速地体现出来,而界面态陷阱电荷的影响则相对较慢。

(a)VDMOS器件结构;(b) 阈值电压变化和辐照注量之间的关系;(c) 泄露电流和辐照注量之间的关系图10 P沟道VDMOS器件的质子辐照损伤效应的综合研究Fig.10 Comprehensive study on proton irradiation damage effects of P-channel VDMOS devices

图11 (a) VDMOS结构剖面电镜图;(b) 12 V偏压下不同处理方法下的转移特性曲线,偏压为12 V;(c) 不同处理方式下Not和Nit的变化情况Fig.11 (a) Electron microscope image of VDMOS structure profile; (b) Transfer characteristic curves for different treatment methods at 12 V bias (c)Variation of Not and Nit under different treatment methods

李兴冀等研究了3 MeV和6 MeV质子对P沟道VDMOS器件的位移及电离损伤特性,测量了阈值电压与漏电流等关键电参数,如图10(a)所示。实验结果表明,阈值电压左移,漏电流增大。电性能测量是用3 MeV和6 MeV质子原位进行的,电性能的变化是不同的。6 MeV质子的阈电压偏移高于3 MeV质子。3 MeV质子辐照后的漏电流高于6 MeV质子辐照后的漏电流。室温退火300 d,阈值电压漂移明显减小,对漏电流影响不大。泄漏电流的增加主要由位移引起,电离损伤主要改变阈值电压的漂移。随着辐照能流的增加,P沟道VDMOS器件的负阈值电压会发生显著变化。对于3 MeV和6 MeV的质子,VTH约为0.85 V和1.08 V。由6 MeV质子引起的VTH大于由3 MeV质子引起的VTH,因此由6 MeV质子引起的电离损伤大于3 MeV质子。退火前后,6 MeV和3 MeV质子的VTH值分别恢复到-3.02 eV和-2.97 eV。

由此可知,室温退火能够明显降低辐照引起的阈值电压漂移。根据SRIM计算和退火结果,VTH的变化可以用电离损伤来解释。图10(c)是在给定的VGS= 0.5 V下,6 MeV和3 MeV质子辐照下,P沟道VDOMOS器件的泄漏电流与辐射流量的关系。6 MeV和3 MeV质子的P沟道VDMOS器件的泄漏电流增长趋势相似,相同的辐射流量保持相同,再增加。在正常情况下,P沟道VDMOS器件的Si体中的PN结不导电,因为3 MeV和6 MeV质子穿透氧化层,不仅引起电离损伤,还引起Si体中的位移损伤。位移损伤可以为稳定的空位缺陷复合物产生有效的复合及俘获中心。当存在大量的位移损伤时,会在P型和N型区域上引入缺陷能级,导致PN结的形成,产生感应重组电流。一般来说,位移损伤与质子产生的空位数成正比。随着注量的增加,3 MeV和6 MeV质子的漏电流变化相似。但在给定的能量密度下,3 MeV质子的漏电流高于6 MeV质子的漏电流,故漏电流的变化可以用位移损伤来解释。

在剂量率效应方面,周新田等研究了辐照加固的VDMOS在γ射线辐照和加速退火过程中的退化,参考航空航天应用标准,考虑了不同剂量率及工作温度对实际工作环境的影响。研究发现,ELDRS效应对器件具有重要影响,且此影响在高温下进一步加剧,严重影响器件的可靠性。研究考虑了3种处理方式,分别为Si-ED、Se-ED、LR-ED。Si-ED处理步骤为低剂量率γ射线辐照同时100 ℃退火处理,Se-ED为高剂量率γ射线辐照后100 ℃退火处理,LR-ED为低剂量率γ射线辐照同时室温退火处理。实验表明,与顺序实验器件(Se-ED)相比,用栅偏压(+12 V)辐照的Si-ED具有较低的氧化物俘获电荷增量(Not)和较高的界面态增量(Nit)。但对于采用漏极偏置(200 V)辐照的Si-ED,其Not和Nit低于Se-EDs,这与采用三端偏置(200 V漏极偏置、10 V栅极偏置和源极接地)辐照的器件类似。此外,在所有情况下,与栅极偏置器件相比,漏极偏置器件的Nit更大,而三端偏置器件的Nit更小,尤其是在Si-ED中。因此Not和Nit的变化会导致器件的阈值电压、击穿电压、漏电流及导通电阻不同程度的退化,这将不可避免地威胁到电气系统的正常运行。实验考虑了不同的偏压条件,发现界面态增加的最差情况是低剂量率辐照结合正栅偏压下的高温环境,而氧化物俘获电荷增加的最差情况是在正漏偏压下高剂量率辐照后进行的加速退火过程。该结论可为后续的航天应用器件可靠性标准评估奠定理论基础。还发现负栅压可有效抑制氧化层中氧化物陷阱电荷及界面态的产生,特别是在低剂量率下,这为器件辐照加固提供了一种解决方案。

5 展望

功率VDMOS器件在电力电子系统中具有极高的应用价值,特别是在航天器中扮演着不可替代的角色,是航空航天和核能应用领域的重要组成。近年来,人们对VDMOS器件进行了系统的抗辐射加固研究,以提高其在辐射环境下的稳定性及可靠性,这对于保障器件在高辐射环境中的正常运行具有重要意义。目前,美国国际整流器公司提供的抗辐射产品线是最先进的,产品线涵盖从低压至中压器件,具有出色的抗总剂量能力,最高可达1000 krad(Si),为辐射环境下的应用提供了高度可靠的解决方案[22]。我国近年来在VDMOS器件抗辐射加固设计方面取得了一系列的突破,部分设计架构已达到国际先进水平,在提高器件在辐射环境中的性能方面具有独创性及领先性。

未来,还需进一步深入研究VDMOS器件的抗辐射效应,包括VDMOS器件的位移效应,基于宽禁带半导体的VDMOS加固设计及仿真。随着器件集成程度的不断提高,基于VDMOS单管组成的集成电路级别的抗辐照问题将得到解决。目前,工艺技术逐渐向原子尺度和电路工艺的方向发展,适用于微纳尺度、宽带隙及跨尺度VDMOS的抗辐照手段将实现高效发展,将对航天航空器件单元、电路及微系统高功率抗辐照应用等起到支撑作用。