基于UltraScale 架构FPGA 的DDR3 用户接口优化系统

文 丰,李晴爽,李辉景

(中北大学 电子测试技术国家重点实验室,山西 太原 030051)

0 引言

随着现代数据存储采集技术的高速发展,在数据采集过程中对于数据处理的要求越来越高,在保证得到的数据可靠且不丢失的同时,更要求数据处理速度快、实时性强、稳定性高且功耗低。高速数据采集作为现代卫星通信、传感器及数据记录仪等应用设备的核心装置,要采用满足高带宽、大容量的高速存储设备。DDR 是目前比较成熟的数据缓存技术[1]。

Xilinx UltraScale 架构的高性能FPGA 具有低功耗、高速DSP 和高块RAM-TO-LOGIC 比率的优点;同时还提供了大量的电源选项,在所需的系统性能和最小功耗之间提供了最优平衡;而且该芯片含有大量的高速差分线对GTH QUAD,可以很好地满足传输大量高速差分信号的要求。本课题将使用基于此架构的FPGA 设计DDR3 的读写操作。但DDR3 不能直接被处理器访问,因此需要设计一款控制器来管理DDR3 的正常读写[2-3]。

1 DDR3 SDRAM 的技术特点

DDR SDRAM 采用双信道同步存储方式。SDR SDRAM 在一个周期内可以读取或写入数据一次,DDR SDRAM 在一个周期内可以读取或写入数据两次。因此,DDR SDRAM 的传输速率是SDR SDRAM 的两倍[4]。目前,已有的DDR 产品的性能参数对比图如表1 所示。

表1 四代DDR 的性能参数对比

从上面的性能参数对比表中可以看到,每一代DDR的升级较前一代都会有着明显的功耗降低、电压减少、数据传输速率的提升[5]。但高性能的DDR 芯片也会给硬件电路设计带来很多问题,例如阻抗设计要求不满足、信号干扰严重等现象。对此应结合频率、速率等方面的具体要求选择。本课题根据取数速率的要求选择DDR3。DDR 性能的不断优化也给软件方面的设计应用带来了很多问题,造成用户开发困难,对此Xilinx 推出了其相应的IP 核,可以很好地解决DDR 底层逻辑设计困难的问题。用户通过MIG IP 核提供的用户接口,可以快速实现FPGA 对DDR3 的控制。

本课题选用镁光公司的MT41K256M16-125 芯片,该芯片包含时钟、地址、控制、数据4 种信号线。CK_P和CK_N 时钟信号输入芯片的全局差分时钟信号;A0~A13 和BA0~BA2 地址信号在DDR3 初始进程时负责对初始模式的寄存器参数的配置。包括配置长度、操作或者突发模式的设定等;数据信号DQ0~DQ15 实现16 bit 数据信号的传递,LDQS 和UDQS 差分数据信号分别控制两组数据的写入平衡,LDM 和UDM 信号是数据掩码信号。CKE 控制信号的自刷新以及使能输入,CS_N 控制片选信号的输入[6];RAS_N 是行选择信号,CAS_N 是列选择信号,WE_N 控制写使能,ODT 引脚接高使能、接低禁用DDR3 内部的终止电阻。ZQ 引脚用于输出驱动校准的外部参考引脚,此引脚与240 Ω 的电阻(RZQ)绑定,电阻再与VSSQ 绑定[7]。其中,VSSQ 代表DQ 电源地,VSS 代表DQ 电源地,VDD 和VDDQ 分别代表电源电压和DQ 电源电压,本课题DDR3 采用1.35 V 供电。

2 硬件设计

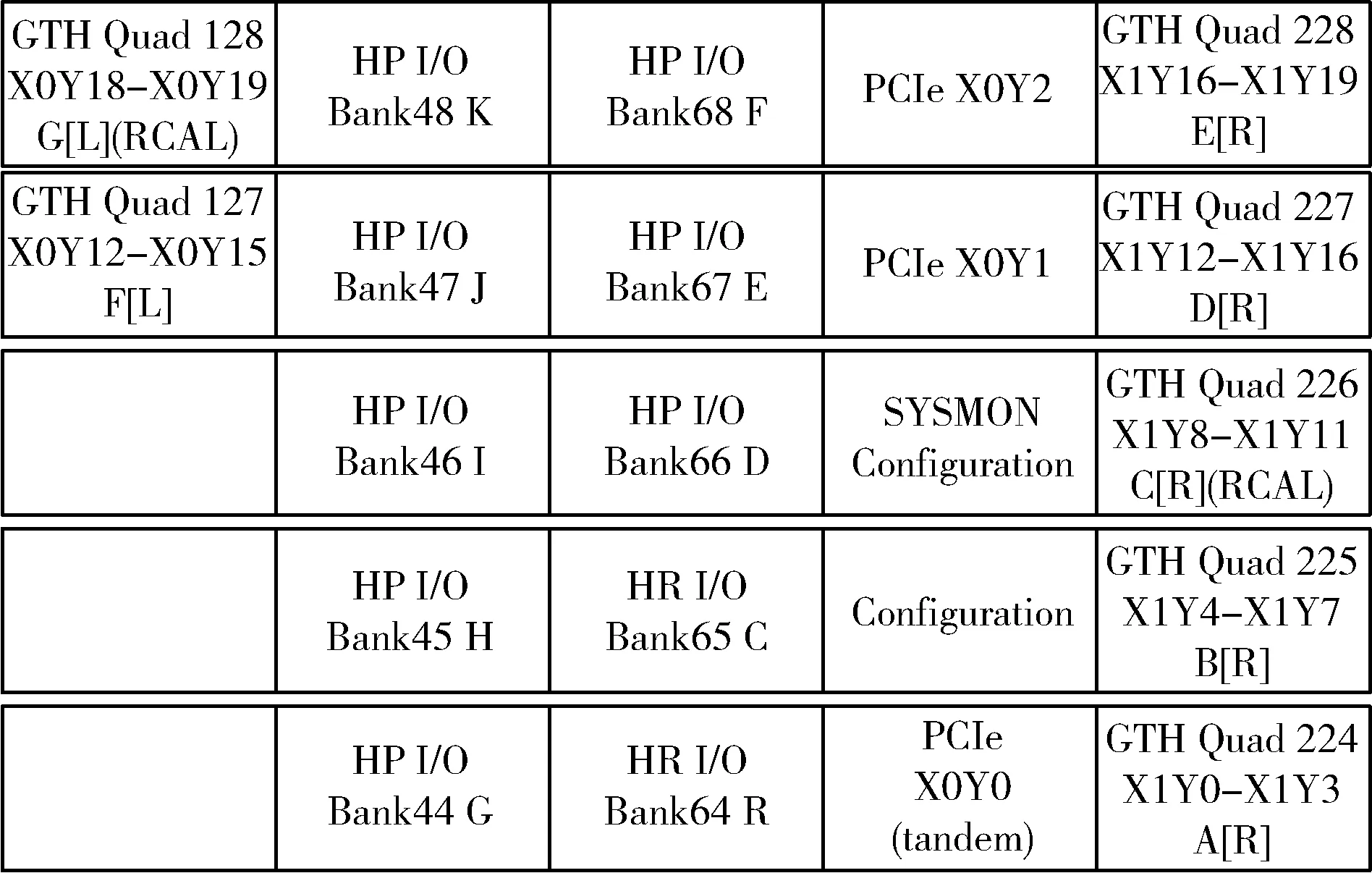

本课题使用的FPGA 芯片是基于Xilinx UltraScale架构的XCKU060-2FFVA1156I,该芯片包含2 个高电压HR I/O Bank 和8 个低电压HP I/O Bank,如图1 所示,完全可以满足1.35 V 供电的DDR3 芯片的使用。

图1 XCKU060-2FFVA1156I 的Bank 分配情况

FPGA 中每个Bank 设计有不同的lane,它们是T0、T1、T2、T3,每个lane 中的引脚编号为N0~N12,下面简单地介绍应用于XCKU060 的DDR3 的引脚分配规则。

(1)DDR3 的dqs 信号必须被分配在时钟对专用字节N6 与N7 上,与dqs 信号相关联的同组dq 信号必须被分配在同一个lane 内N1 和N12 引脚之外的其他引脚上,与之相关联的同组dm 信号必须被分配在相同lane的N0 引脚上。

(2)DDR3 的dqs 信号所处的lane 可以被认为是数据字节lane,数据字节lane 的N1 和N12 引脚可以被用来存放地址或控制信号。地址信号和控制信号可以在N0~N12 中的任何一个引脚上,但所有的地址,控制信号必须在同一个bank 中。

(3)每个bank 都有一个vrp 引脚需要连接DCI,在包含输入的I/O bank 以及仅包含输出的bank 内都需要vrp引脚,只包含输出的bank 需要vrp 引脚,因为地址信号和控制信号使用SSTL15DCI/SSTL135_DCI 来启动控制输出阻抗,当DCI 选择级联时,vrp 引脚可以被当做正常的I/O 口使用。

(4)内存复位引脚reset 可以被分配到任何地方,只要能够满足时长。

(5)系统时钟引脚ck 可以被分配到不同的bank,但必须在同一列的内存接口bank 内。

在45bank 对控制信号、时钟信号、地址信号和数据信号分配I/O 引脚,DDR3 与FPGA 的原理图如图2~图4 所示。

图2 DDR3 退耦电路

图4 DDR3 的1.35 V 供电电源模块电路

3 DDR3 连续读写的FPGA 实现

3.1 DDR3 SDRAM 的IP 核应用

DDR3 SDRAM IP 核是Xilinx 公司提供的用户使用接口,它将FPGA 的片内逻辑功能封装起来,在用户开发过程中,只需按照需求在IP 核向导中进行配置即可[8]。DDR3 的IP 核生成流程图如图5 所示。

图5 DDR3 SDRAM IP 核生成流程图

3.2 DDR3 SDRAM 的用户接口解决方案

对IP 核配置完成后即可得到DDR3 SDRAM 控制器的用户接口解决方案[9],如图6 所示。

用户通过用户接口模块对DDR3 进行读写操作,用户接口模块位于IP 核的最前端,直接对接用户逻辑控制模块。

内存控制模块在物理层模块和用户接口模块中间,IP 核的本地接口在内存控制模块前端与用户接口模块连接。内存控制模块可以帮用户提供DDR3 外部存储设备和用户设计模块之间的数据传送机制,并且可以帮用户提交读写请求给存储器;其后端连接至物理层接口,可以处理物理层接口模块的所有请求;同时,内存控制模块可以选择是否重新排序的功能,将其接收到的所有选择进行重新排序可以优化整个数据传输过程的数据吞吐量与时延[10]。

物理层模块的后端通过引脚连接至外部存储设备DDR3,其前端连接至内存控制模块。物理层模块可以暂时存储来自内存控制模块输入的DDR3 系统的数据、地址、控制等信号,并且产生控制DDR3 的指令信号,以此可以保证地址、数据信号与指令能够同步传送,并传输捕获到的DDR3 发出的数据给内存控制模块[11-12]。

3.3 DDR3 SDRAM 的读写操作说明

用户在IP 核的信息配置页面对DDR3 的参数进行设置时用户接口模块即被确定,用户逻辑控制模块的功能在于通过控制用户接口的信号得以控制DDR3 的读写操作[13-14]。

在读数期间由时钟信号、准备信号、使能写地址信号、使能信号和命令信号有效进行读操作,更新读地址。读期间的理想时序图如图7 所示。

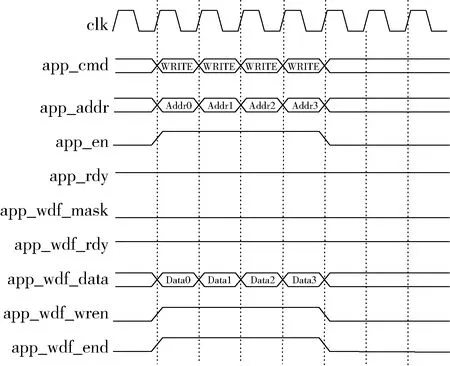

当写地址和写数据信号同时有效时才可以成功进行写操作。写操作与写地址不必同时进行,二者可以相差几个周期。当用户接口的准备信号和使能信号同时处于高使能状态时,写操作的命令和地址信号是有效的,当app_wdf_rdy 信号和app_wdf_wren 信号处于高使能状态时,写入数据的信号是有效的[15]。写操作时各信号的理想时序图如图8 所示。

图8 DDR3 写操作

4 用户接口优化方案

由于Xilinx 提供的DDR3 IP 核的用户接口信号逻辑设计比较复杂,用户在应用时比较难以设计,为了方便用户的使用,引入读写FIFO 和读写逻辑控制模块对DDR3 SDRAM IP 核进行用户接口优化。可以屏蔽掉IP核中复杂的用户接口,用简易的接口封装使得用户只需确保信号能够顺利地存入进行写操作,以及能够顺利地从读操作中读出使用,如图9 所示。

图9 类FIFO 接口封装结构图

DDR3 SDRAM 模块由IP 核,读写FIFO 和读写控制模块四部分组成。写FIFO 用于控制信号写入数据流,读FIFO 用来将DDR3 内读取的数据顺利输出,整个读写控制模块通过控制DDR3 整体的读写进行状态将读写效率控制在最佳状态。DDR3 读写状态机是DDR3 模块的关键设计,状态机存在3 种工作状态:在write 状态下进行写操作,在read 状态下进行读操作,在idle 状态下不进行任何操作。为了保证状态机的读写效率不被影响,在使用时不能频繁地切换读写状态。通过控制写FIFO 的编程空信号和读FIFO 的编程满信号以采用双门限设置的方法,数据将在写FIFO 数据已满的状态下丢失,而当读FIFO 已满状态下数据将会缓存在DDR3 内部。所以读操作低于写操作的优先级。

在型号为XCKU060-2FFVA1156I 的FPGA 以及型号为MT41K256M16 的DDR3 SDRAM 基础上对设计的DDR3 控制器进行验证。图10、图11 为在VIVADO 软件对DDR3 内部读写操作进行仿真得到的简易时序图。

图10 DDR3 内部写操作仿真时序图

图11 DDR3 内部读操作仿真时序图

从图10 中可以看出,当app_wdf_rdy 信号和app_wdf_wren 信号同时有效时可以准确写入对应的数据“00、01、02、03、00”。从图11 中可以看出当app_rd_data_valid 信号有效时,app_read_data 信号有效的输出“00、01、02”。该控制器的读写操作数据一致,验证了设计的有效性及准确性,可以有效使用该控制器实现DDR3 数据读写。

5 结论

本设计以Xilinx 公司的XCKU060 FPGA 为核心,通过对DDR3 SDRAM 分区存储实现了高速图像数据采集,并且保证了DDR3 在高速数据流缓存中工作的可靠性和较高的工作效率。在介绍DDR3 的读写操作是如何实现的的基础上,介绍了读写控制模块的用户接口优化。本设计模块接口应用简单、可移植性较高。该设计在航天、军事、医学和农业领域的高速图像处理领域有着广泛的应用前景。