p-GaN/n-Ga2O3结终端延伸肖特基二极管结构仿真研究

常青原,贾富春,李萌迪,侯 斌,杨 凌,马晓华

(西安电子科技大学,西安 710071)

0 引言

氧化镓大禁带宽度(Eg=4.8 eV)带来理论上的高临界击穿场强(Ec=8 MV/cm)[1-2],再结合电子迁移率(μ=250 cm2/Vs)[3-5],使其在功率开关应用领域具有高的品质因数。除了这些优异的材料性能外,大面积本征衬底可以用低成本的熔融法制造,同时也降低了材料缺陷密度[6],为氧化镓器件的快速发展提供了额外的优势。但Ga2O3极易引入氧空位等施主能级,导致P型Ga2O3难以制备[7]。作为当下研究热点的垂直体系Ga2O3SBD,具有较高的高温稳定性和良好的耐辐照特性,使其能够在高温度、高功率、高辐照的条件下工作,从而保证了其长期的稳定性和可靠性,因此在空间电子领域有着广泛的应用前景。但SBD肖特基接触边缘存在电场集中效应,高效的电场管理十分具有挑战性。目前国际上进行电场调制的主流方法有:场板终端[8-9]、离子注入终端[10-12]、p-NiOx终端[7]等,但目前SBD临界击穿场强仍低于Ga2O3材料极限值。

本文提出采用p-GaN结终端延伸结构调节SBD肖特基接触边缘电场分布,其优势在于P型GaN的P型掺杂浓度可具体表征、精确调控,可制备高质量的P型区域[13],提高器件反向特性。在本次研究中通过Silvaco仿真对比了有无p-GaN/n-Ga2O3JTE结构的SBD正反向特性,同时探究了p-GaN区域厚度对SBD性能的影响。发现采用p-GaN/n-Ga2O3JTE结构的肖特基二极管击穿电压由880 V增加到1 349 V,p-GaN深度由0.3 μm增加到1.2 μm,器件击穿电压由1 349 V进一步提升到1 685 V。通过仿真为流片实验提供了理论指导。

1 仿真参数设置

基于已有氧化镓流片经验,并参考国际Dong等[14]报道器件结构,给出了器件三维结构示意图,将以此为依据设计器件仿真结构,如图1所示。

图1 肖特基二极管三维结构示意图及三维结构剖面示意图

图1(a)和(b)分别为对照肖特基二极管和p-GaN/n-Ga2O3JTE肖特基二极管三维结构示意图。图1(c)和(d)分别为对照肖特基二极管和p-GaN/n-Ga2O3JTE肖特基二极管三维结构的剖面示意图。

器件仿真结构选用图1(c)和(d)中黑色虚线框圈出的二维截面,具体如图2所示。

图2 肖特基二极管二维仿真结构示意图

器件仿真采用的结构参数为:200 nm厚、30 μm宽的阳极,10 μm厚、40 μm宽、掺杂浓度为1×1016cm-3的n--Ga2O3漂移层,2 μm厚、40 μm宽、掺杂浓度为1×1020cm-3的n+-Ga2O3层,200 nm厚、40 μm宽的阴极。对于p-GaN/n-Ga2O3JTE肖特基二极管,p-GaN结构参数为0.3 μm厚、15 μm宽、掺杂浓度为1×1018cm-3的p-GaN层。图2中使用白色虚线对阳极边缘位置和p-GaN边缘位置在横轴上进行了标注。

仿真模型参考了Arpit Nandi团队报道的Ga2O3JBS器件[15],在该篇报道中优化模型参数后的Silvaco仿真结果与实验结果具有高度一致性,证明了仿真软件的精确性和本次仿真结果所具有参考价值。

2 仿真研究

2.1 p-GaN/n-Ga2O3 JTE结构对SBD性能的影响

通过仿真得到对照Ga2O3肖特基二极管导通电压为0.64 V(1 A/cm2),导通电阻为4.68 mΩ·cm2,击穿电压为880 V(10 A/cm2);0.3 μm p-GaN/n-Ga2O3JTE肖特基二极管导通电压为0.68 V(1 A/cm2),导通电阻为5.62 mΩ·cm2,击穿电压为1 349 V(10 A/cm2)。器件特性曲线如图3所示。发现采用JTE的肖特基二极管反向击穿电压得到了显著的优化,增加了近一倍,但在相同正向阳极偏压下,器件正向电流有所减小,这意味着器件导通电阻有所增加,器件正常开关工作过程中功耗增加。但相较于SBD反向击穿电压的巨大提升,正向特性的略微退化在可接受范围内。

图3 对照Ga2O3肖特基二极管和p-GaN/n-Ga2O3结终端延伸肖特基二极管正向和反向特性对比

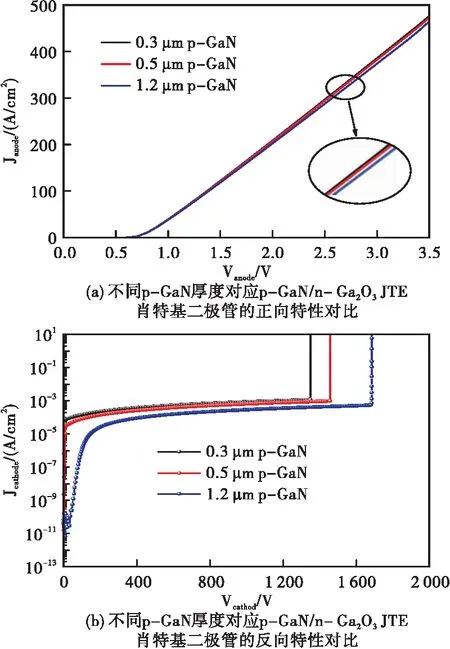

2.2 p-GaN厚度对SBD性能的影响

为进一步优化器件结构,为后续器件设计提供实际指导,接下来通过Silvaco仿真探究了p-GaN厚度(0.3 μm、0.5 μm和1.2 μm)对器件正反向特性的影响,仿真结果如图4所示。发现通过增加p-GaN厚度,器件反向泄漏电流逐步降低,击穿电压可进一步提升,由1 349 V进一步提升到1 685 V,同时器件正向特性略有退化。通过仿真说明在实际器件制造中,可通过增加p-GaN厚度,对肖特基二极管正向特性和反向特性进行折中设计,通过略微舍弃器件正向特性来获得反向特性的大幅提升。

图4 不同p-GaN厚度对应p-GaN/n-Ga2O3 JTE肖特基二极管的正向和反向特性对比

需要注意的是,在实际器件制备的过程中,p-GaN深度的增加给Ga2O3凹槽刻蚀带来了新的挑战。在相同的刻蚀配方下,更深的凹槽意味着刻蚀时间的加长。在此情况下,需要综合考虑光刻胶厚度和p-GaN厚度,抑或是优化刻蚀配方以获得更高的刻蚀选择比,在相同光刻胶厚度的条件下获得更深的凹槽。

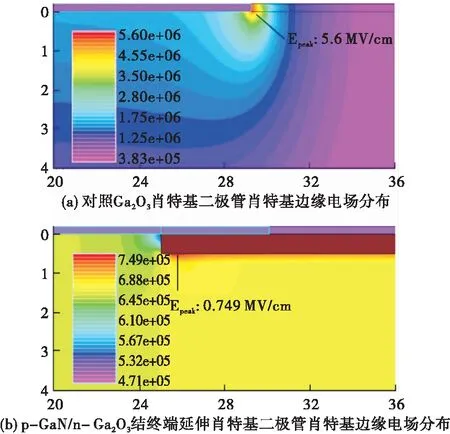

2.3 JTE结构提升击穿的内在机理

为探究p-GaN/n-Ga2O3JTE结构提升器件击穿电压的内在机理,运用Silvaco软件对-800 V偏压下的对照肖特基二极管和p-GaN/n-Ga2O3JTE肖特基二极管进行了电场仿真研究,仿真得到器件在-800 V下的电场分布,如图5所示。发现采用p-GaN/n-Ga2O3JTE结构后器件肖特基接触边缘的峰值电场由器件表面转移到器件体内并且其数值有所降低,由5.600 MV/cm降低到0.749 MV/cm。这意味着在相同的反向偏压下,采用p-GaN/n-Ga2O3JTE的肖特基二极管电子更难被肖特基接触边缘存在的峰值电场加速造成雪崩击穿,避免了器件的过早击穿。

图5 对照Ga2O3肖特基二极管和p-GaN/n-Ga2O3结终端延伸肖特基二极管电场分布对比

3 结论

本文基于Silvaco TCAD-ATLAS仿真软件,对照肖特基二极管和p-GaN/n-Ga2O3JTE肖特基二极管进行了仿真研究,探究了p-GaN/n-Ga2O3JTE结构对肖特基二极管正反向特性的影响。发现通过采用p-GaN/n-Ga2O3JTE结构,肖特基二极管击穿电压由880 V(10 A/cm2)提升到1 349 V(10 A/cm2)。并且通过增加p-GaN厚度到1.2 μm,器件击穿电压进一步提升到1 685 V,代价是正向导通电阻的略微增加。最后通过探究-800 V反向偏压下器件内部的电场分布,发现采用p-GaN/n-Ga2O3JTE结构后器件肖特基接触边缘的峰值电场由器件表面转移到器件体内并且其数值有所降低,由5.600 MV/cm降低到0.749 MV/cm。解释了p-GaN/n-Ga2O3JTE结构提升器件击穿的内在机理。为了得到最优的器件结构参数,下一步工作需要对p-GaN的掺杂浓度及p-GaN与阳极的交叠深度对器件特性的影响进行仿真研究。