FPGA中单指数核信号梯形成形算法优化与实现

祝 翔,何剑锋*,曾家骏,袁兆林

(1. 东华理工大学信息工程学院,江西 南昌 330013;2. 江西省放射性地学大数据技术工程实验室,江西 南昌 330013;3. 江西省核地学数据科学与系统工程技术研究中心,江西 南昌 330013)

1 引言

本文对单指数核信号梯形成形算法在FPGA的设计进行了优化,在Simulink环境下,设计搭建了基于Z变换的一般核脉冲梯形成形平台和模块化级联型结构核脉冲梯形成形平台,对两种平台结构进行比较分析与抗噪结构性改进,并设计了一个直接I型FIR低通滤波器,对高速ADC输入信号进行噪声滤除,噪声滤除效果良好,减少了噪声对测量精度和能量分辨率的影响,最后通过工具自动生成Verilog代码移植到FPGA上,降低了研究的时间成本。

2 单指数核信号梯形成形算法公式推导

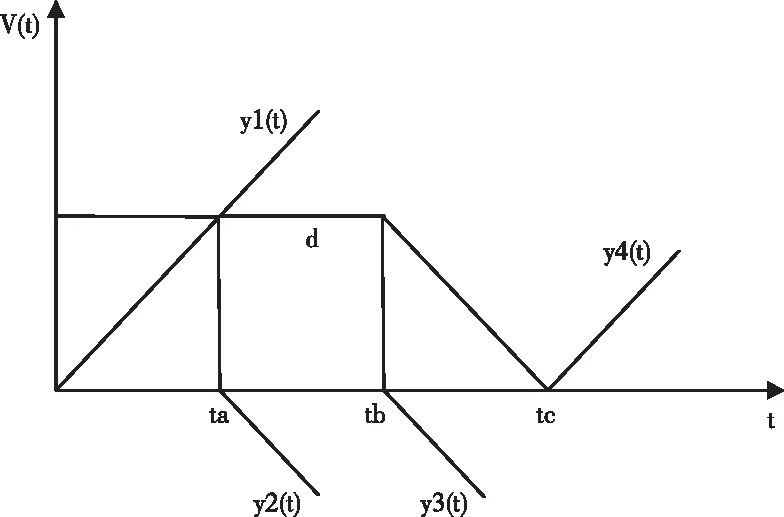

数字多道脉冲幅度分析器(DMCA)的设计中,梯形滤波成形算法是对核信号进行滤波成形处理使用频率最高的一种方法,因为梯形滤波成形的信号是一个等腰梯形,脉冲前后沿时间相等,脉宽窄,下降速度快,脉冲的上升沿和平顶宽度可以独立调节,以适应不同成形需求的实验,能有效抑制弹道亏损[11,12]。理想核脉冲的梯形滤波成形如图1所示。

图1 梯形成形示意图

核辐射信息经过闪烁体探测器或半导体探测器等核辐射探测器转换成电信号,这些核脉冲信号幅值不同、随机分布,但波形相似,其上升速度快、时间很短,下降缓慢、时间较长,顶部尖锐,波形图形的特征与指数衰减信号十分类似[13]。

设前放输出理想状态的单指数衰减信号,时域表达式为

Vi(t)=Vmax·exp(-t/tao)·u(t)

(1)

式中,Vmax为单指数衰减信号的幅值;tao为单指数衰减信号的时间常数;u(t)为标准单位阶跃函数。以Ts为采样周期进行采样,则有脉冲序列表达式为

Vi(t)=Vmax·exp(-n·Ts/tao)·u(t)

(2)

对(1)式作Z变换,且令d1=exp(-n·Ts/tao)则有

Vi(z)=z·Vmax/(z·d1)

(3)

图1中,Vmax为输出梯形信号的高度,ta为输出梯形信号的上升沿,tb为输出脉冲的宽度,d为梯形的平顶宽度,d=tb-ta;用分段函数表示梯形信号

从高等教育领域来分析,大数据在提供教育决策支持、推进教育教学改革以及深化教育管理变革等方面都起到了显著的作用。目前各教育主管部门和高校由于重视程度、基础条件、研究能力以及资金投入不同,大数据的应用发展水平也大不相同。如果要加强大数据在高等教育领域中的应用,充分发挥教育领域中海量数据的真实价值,应该需要从以下几个方面继续努力。

(4)

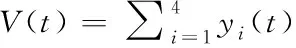

其中,y1(t)=Vmax·t;y2(t)=-y1(t-ta);y3(t)=-y1(t-tb);y4(t)=-y1(t-tc)。把上述子式代入式(4)做单边Z变换。

则有表达式为

(5)

其中,na=ta/Ts,nb=tb/Ts,nc=tc/Ts。

那么,由表达式(3)和表达式(5)则可以得到梯形滤波成形算法的Z变换函数

(6)

式中,na、nb为调节参数。

对式(6)进行Z逆变换,则可求得其时域表达式

V0(n)=2·V0(n-1)-V0(n-2)+

+Vi(n-nc-1)-d1·[Vi(n-2)-Vi(n-na-2)-Vi(n-nb-2)+Vi(n-nc-2)]}

(7)

根据时域表达式(7)就可以在MATLAB中编写脚本程序进行仿真,并在Simulink环境下搭建核脉冲梯形成形平台进行系统级仿真验证。可以通过改变na、nb的值在仿真中实现对梯形成形信号的调节。

3 梯形成形算法MATLAB仿真与模型改进

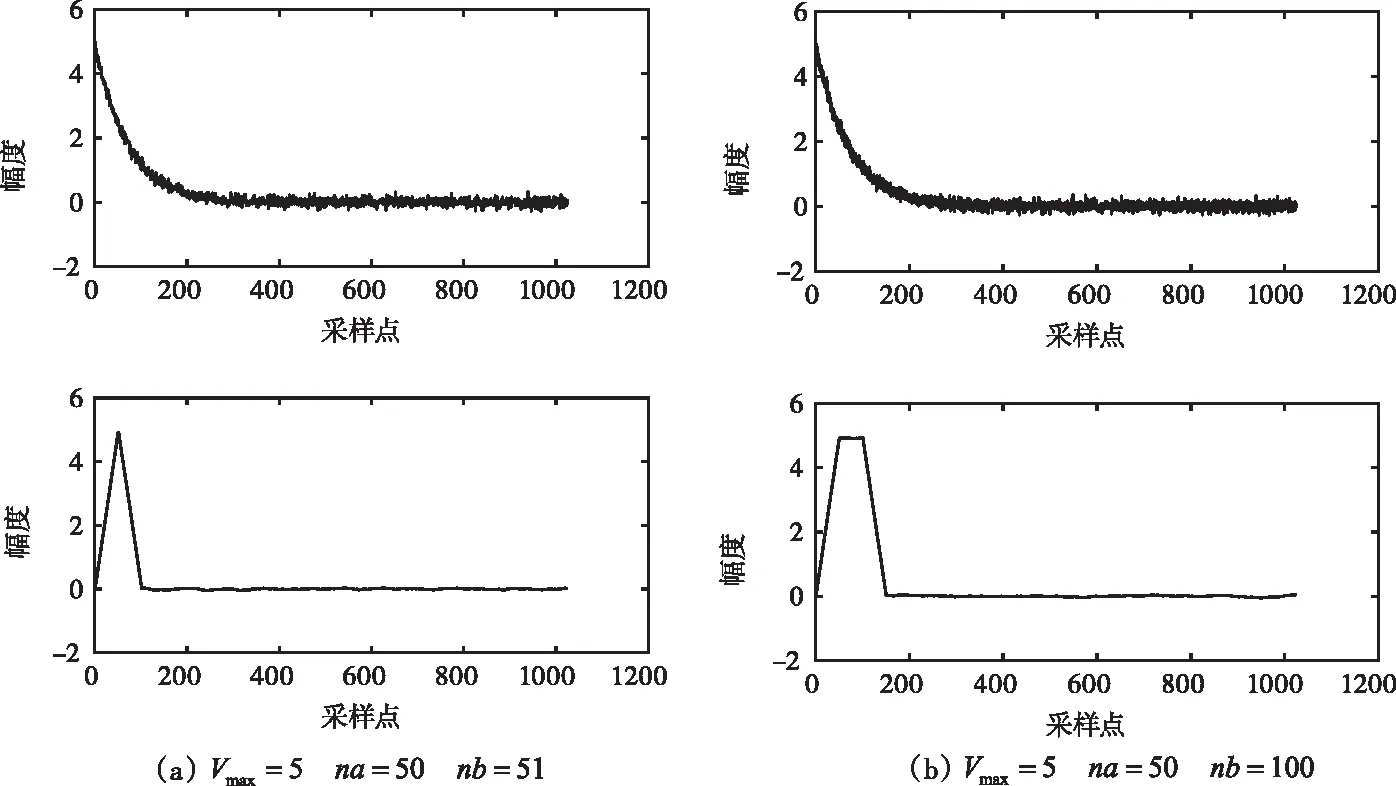

根据单指数衰减脉冲信号式(1)在MATLAB R2017b中编写梯形成形滤波脚本程序,以单指数衰减信号来模拟探测器的输出信号,仿真后得到效果如图2所示。考虑到实际情况中,探测器输出的信号会存在一定的噪声干扰,电子学噪声和高速ADC实时采样高频噪声与有用信号叠加后会降低测量精度,影响能量分辨率[14,15]。核电子学噪声产生影响的主要是热噪声和散粒噪声,这两者都是呈高斯正态分布的,因此,为了使仿真实验更贴近现实,在单指数衰减信号上叠加了一个高斯加性白噪声来模仿现实噪声所产生的影响,仿真波形如图3所示。

图3 加噪声信号梯形成形MATLAB仿真

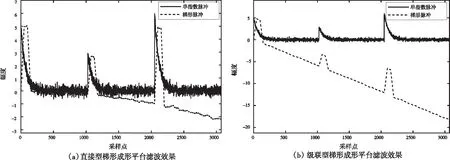

经过脚本程序进行模拟之后,在Simulink中建立梯形滤波成形平台,建立了直接型和模块化级联型两种脉冲梯形成形平台,读取叠加噪声的脉冲信号查看波形,Vmax=5,Vmax=3,Vmax=6,取量化时间ta=50,tb=100,得到滤波成形的波形如图4所示。脚本程序模拟出的良好波形在Simulink中噪声更加明显,对脉冲信号的梯形滤波成形带来影响,产生了基线误差。在直接型梯形成形平台中,梯形成形曲线不够平滑,且出现了基线漂移,而在初始设计的模块化级联型梯形成形平台中,虽然噪声的影响比直接型平台的小,但是也产生了基线漂移。这是因为在模型结构上,没有对噪声进行优化处理,差分运算部分靠前而非差分运算部分在后,这样的结构导致了滤波成形平台的整体结构抗噪性弱[16]。

图4 两种梯形成形平台滤波效果对比

综合以上原因,对上述方法做出了一些改进调整。首先,在模拟的梯形成形算法上,引入FIR滤波,在采样频率为50MHz的情况下,经过多次实验,确定了较好的数字截止频率ωn=0.45,基于MATLAB的fir1函数,求出滤波系数,再用MATLAB函数库中的filter函数滤波,设计了一个长度为32位的低通滤波器,滤除噪声,降低噪声产生的负面影响。其次,在梯形成形平台设计中,利用filterDesigner工具箱,选用等波纹的设计方法,设置采样频率为50MHz,设计了一个7阶等波纹FIR低通滤波器。由于其是有限单位脉冲响应,且具有很好的选频特性,在滤除噪声的同时拥有较好的稳定性[17]。经过FIR数字滤波器后,输入信号的噪声得到很好的滤除,噪声滤除前后效果对比如图5所示。

此外,在梯形成形平台结构设计上采用模块化设计,设计了级联型滤波平台的同时,改变了差分结构的位置,将整个负反馈结构的位置前移,削弱了噪声累积,使得基线漂移的情况得到改善。整体改进后的级联型平台梯形成形效果如图6所示。基线漂移得到改善,对输入信号滤除噪声后进行的梯形滤波成形,噪声得到明显的抑制,滤波成形的梯形效果良好。

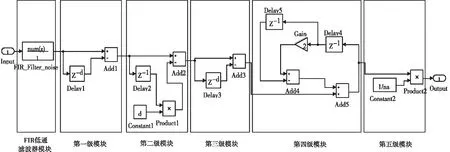

3 FPGA硬件实现与分析

采取级联型结构实现梯形成形滤波器的设计与验证,其本质上是由级数低的滤波器级联形成级数高的滤波器,每个滤波器都是独立的模块,并且将前一级的输出作为后一级的输入。如果由直接型结构实现梯形成形滤波器的设计,资源耗费大、结构复杂,并且数字处理有限精度的情况下,系统稳定性较差。采用级联型结构设计后,降低了资源消耗,优化了模型结构,提升了运算速度,并且系统更加稳定。设计好的级联型梯形成形滤波器模块化结构如图7所示。

图7 梯形成形滤波器模块化结构

输入信号从Input进入后先经过FIR低通滤波器,滤除噪声后进入第一级模块做延时处理,然后将第一级模块的输出作为后一级模块的输入,以此类推直至第五级模块结束,最后由Output输出梯形成形结果,成形波形可添加一个示波器模块Scope进行观察。

FIR低通滤波器模块是对输入信号进行噪声滤除,其输出信号的噪声大大降低,噪声的滤除效果如图5所示。FIR低通滤波器输出的信号作为第一级模块的的输入,第一级模块对滤除噪声的核脉冲信号进行nb个延时,输出信号就是从低通滤波器输出的信号减去nb个延时后的信号,输出波形是在滤除噪声信号波形后nb处将滤除噪声信号进行翻转。第二级模块将第一级模块的输出作为输入,并将这个信号延时一个时钟周期再乘以d_1,输出信号则由将第一级模块输出的信号减去延时一个时钟周期再乘d_1的信号所得到,仿真输出的波形则是第一级模块输出波形的幅度峰值。第三级模块的结构与第一级模块相同,输出信号是第二级模块输出的信号与将第二级模块输出的信号作na个延时后的信号做差得到的结果。第三级模块的输出作为第四级模块的输入,输出信号则是输入信号加上延时一个周期输入信号的两倍增益与输入信号延时两个周期的差,第四级模块是一个负反馈结构,不能够轻易调换位置,否则会产生基线漂移。第五级模块则是将第四级模块输出的信号除以na,输出波形就是将本季模块的输入信号波形缩小na倍,也就是最后成形的梯形。

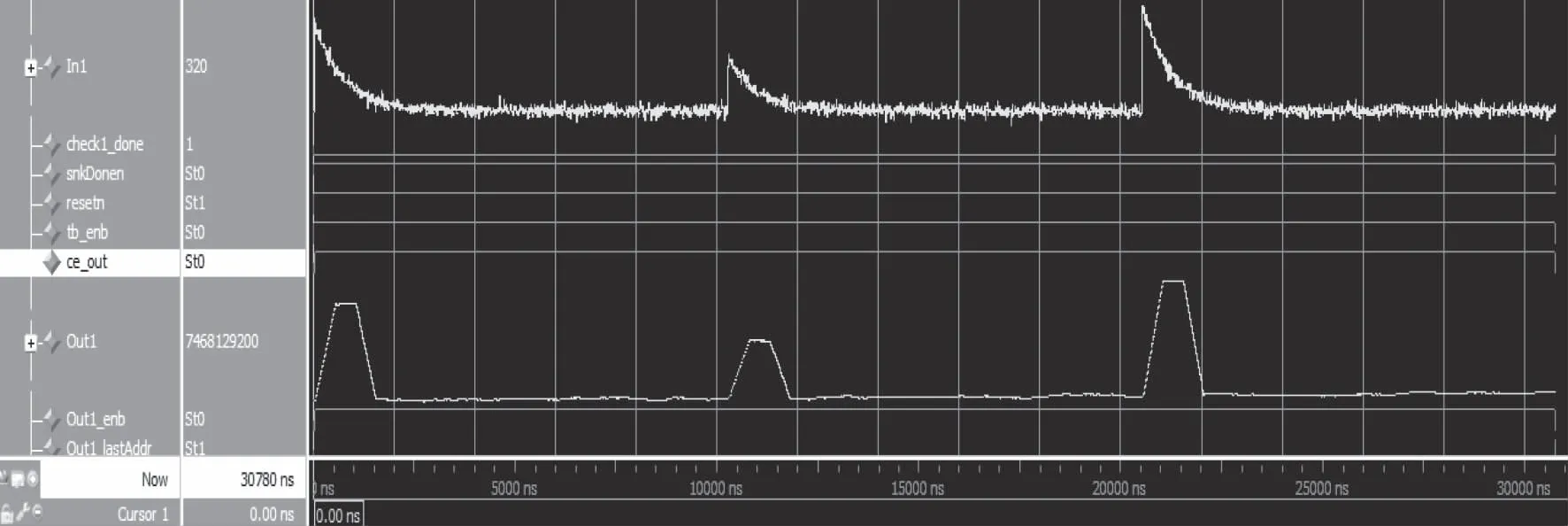

在Simulink设计好梯形滤波成形平台后,在Code选项卡调用HDL Workflow Advisor生成工程文件,用Quartus和Model-sim仿真软件打开工程文件对梯形成形效果作仿真验证。在生成工程时,硬件语言可以选择为VHDL或者Verilog HDL,可以根据实验需求进行选择。选用Verilog HDL语言生成工程后,由Quartus开发工具对整个工程进行编译、综合、布局布线,直至在FPGA上完成整个工作流程。用Model-sim仿真得到梯形成形波形如图8所示,得到的波形与MATLAB仿真测试波形的效果基本一致,FIR低通滤波器对噪声滤除效果好。

图8 梯形滤波成形Modelsim仿真

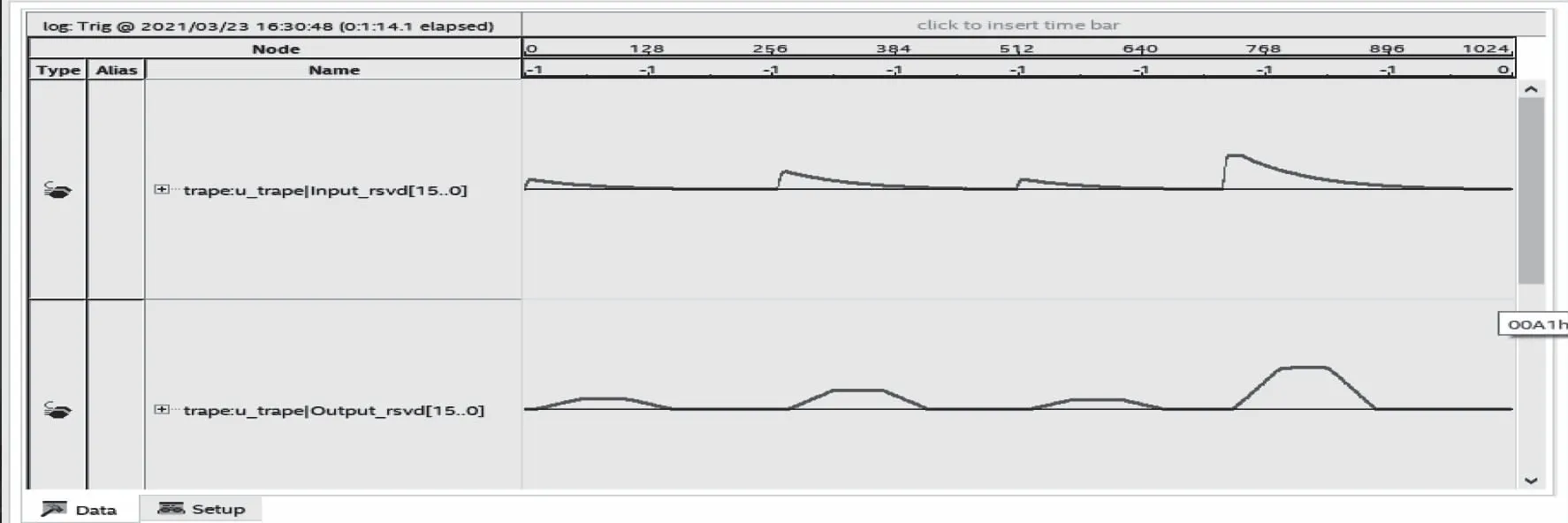

模拟验证通过后,在Quartus Prime中调用工具栏的Signal Tap Logic Analyzer 进行板级调试,调试时设置好所需参数,添加捕捉的波形,并设置触发条件,设置完成后进行一次综合编译,最后将FPGA硬件开发板上电,选定设备为开发板,将综合后的程序下载到FPGA硬件,传输数据并捕捉波形。本次实验选用的是Altera公司的EP4CE10F17C8芯片完实现多道数字滤波成形算法的设计。采用的是CIT-3000SY X 荧光元素录井仪实测的部分原始数据进行实际测试,通过Signal Tap对梯形成形滤波器输入输出的数据进行捕捉和观察验证,捕捉的波形如图9所示。波形捕捉准确,最终完成了数字多道梯形成形算法在FPGA的实现与改进。

图9 梯形滤波成形Signal Tap 时序验证图

4 结论

本文对单指数核脉冲的级联型结构梯形滤波成形平台改进后,提升了结构抗噪性,设计的直接型FIR低通滤波器对噪声能进行有效滤除,降低了噪声的干扰;对单指数核脉冲作梯形成形仿真,确定了合适的成形参数,能对成形脉冲进行调节从而适应需求;使用Simulink的HDL Code工具后,整体的设计使得FPGA开发流程得以简化,硬件资源消耗降低,通过Signal Tap Logic Analyzer 内嵌逻辑分析仪对实际数据的成形波形进行观察分析,结果与仿真结果基本一致,取得了不错的测试结果,对数字多道脉冲幅度分析器后续的设计工作具有一定帮助。