面向5G 智能电网的高精度时钟在线实时同步方法

韩子媛,王 轩,秦靖尧,王 瞧,许 岩

(1.中国电建集团河南省电力勘测设计院有限公司,河南郑州 450000;2.河南工业大学电气工程学院,河南郑州 450001)

5G 智能电网[1-3]需要统一的时间基准、精确的时间信息为实现“枢纽型、平台型、开放型”电力物联网保驾护航。智能电网中信号同步采样、设备故障检测及协调控制等均对时钟同步系统提出了高精度需求[4-6]。

目前,研究者多采用IEEE1588 精确时间同步协议[7-9]完成主从节点时差测量,基于PID 反馈控制方法调节从节点时钟,以与主节点时钟保持同步,如基于神经网络的PID 时钟控制算法[10-11]、基于模糊逻辑的PI 时钟控制算法[12-13]。为了进一步提高时钟同步性能,遗传算法(GA)[14]、粒子群优化(PSO)[15]、天牛须搜索[16]等方法被用于PID 控制器参数的整定和优化。以上研究中:①多侧重于PID 控制器参数优化;②多采用时钟误差状态的一次多项式模型,未充分考虑时钟相位误差、频率误差、钟漂的影响;③实际工程应用中主从节点多采用DSP/ARM+FPGA 物理架构,以上智能算法存在计算耗时、算法复杂度高等缺点,不利于在FPGA 等物理平台上实现。

为此,该文提出一种面向5G 智能电网的高精度时钟在线实时同步方法,并建立其数字实现模型,实现纳秒级主从节点时钟同步精度,支撑工程实践应用。

1 时钟状态建模

为了实现5G智能电网中主从节点的时钟同步,需要建立精确的时钟状态模型。表征时钟稳定性的因素主要包含时钟相位误差、频率误差和频率漂移。故采用二次多项式建立时钟状态模型,如式(1)所示:

式中,θ、γ和α分别为主从节点间时钟相位误差、频率误差和频率漂移,Tu为时钟同步系统的更新时间(调整间隔)。

2 时钟在线实时同步方法

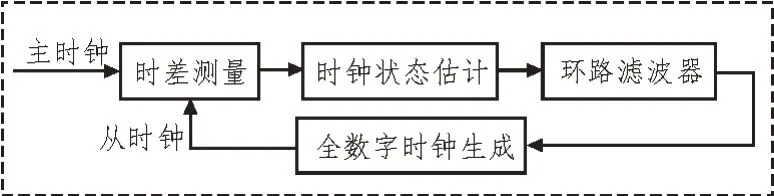

面向5G 智能电网的高精度时钟同步方法采用一种由时差测量、时钟状态估计、环路滤波器和全数字时钟生成单元构成的时钟反馈控制环路,实现主从节点间时钟同步。系统框图如图1 所示。

图1 时钟同步系统框图

具体原理如下:

1)时差测量单元

时差测量单元采用IEEE1588 协议获取主从节点时差ΔT。由主从节点间时差,可得主从节点间相位误差为:

式中,f0为系统标称频率。将主从节点间相位误差θ作为时钟状态估计单元的观测量。

2)时钟状态估计单元

为了降低时钟测量噪声对时钟同步精度的影响,采用卡尔曼滤波(Kalman Filter,KF)对时钟状态进行滤波估计。将时钟状态模型(式(1))作为KF 滤波的状态方程,表示为:

式中,A为3×3 的状态转移矩阵;ωk为状态向量噪声,其协方差矩阵为KF 滤波的过程噪声Q,=[θkγkαk]T表示tk时刻的状态向量。

时钟状态估计的观测方程为:

式中,zk=θ=2πf0ΔT由时差测量单元计算得到;H=[1 0 0] 为1×3 的设计矩阵;vk为测量噪声,其协方差矩阵为KF 滤波的测量噪声R。

3)环路滤波器单元

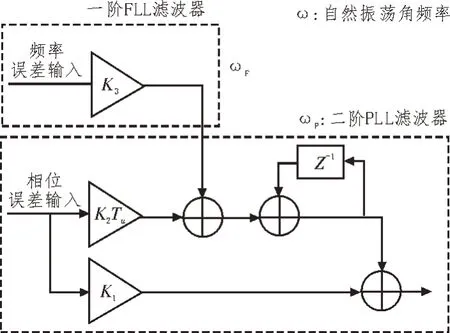

环路滤波器单元采用一阶FLL 辅助的PLL 滤波器(图2),以保证环路有足够大的频率牵引能力和足够高的时钟输出精度,输出用以调整从节点时钟。

图2 一阶FLL辅助的二阶PLL滤波器

环路滤波器中二阶PLL 滤波器的数字域表达式为:

其环路增益K1和K2的计算方法如下:

式中,BL为二阶PLL 滤波器的单边等效噪声带宽,ωP为自然振荡角频率,ξ为阻尼系数。

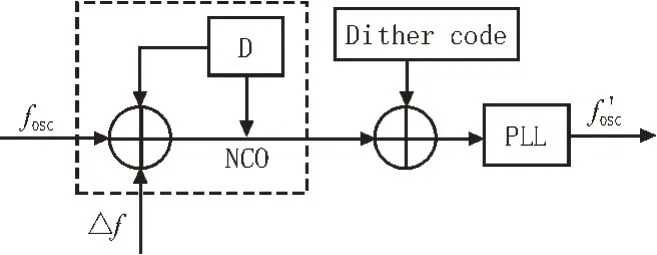

4)全数字时钟生成单元

全数字时钟单元(图3)采用脉冲抑制技术(Dither code)和电荷泵锁相环(Phase Locked Loop,PLL)实现高质量参考频率的再生,以与主节点时钟保持同步。图3 中,fOSC为从节点时钟,Δf为频率调整量为从节点时钟同步后的目标频率。

图3 全数字时钟生成

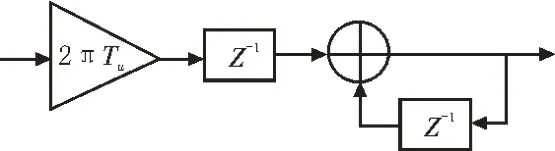

由于PLL 和抖动码(Dither code)不影响数字振荡器(NCO)的输出频率值,因此全数字时钟生成单元本质上是一个NCO。因此,将全数字时钟生成单元等效建模为系数为2πTu的累加器,如图4 所示。

图4 数字振荡器

3 系统仿真与验证

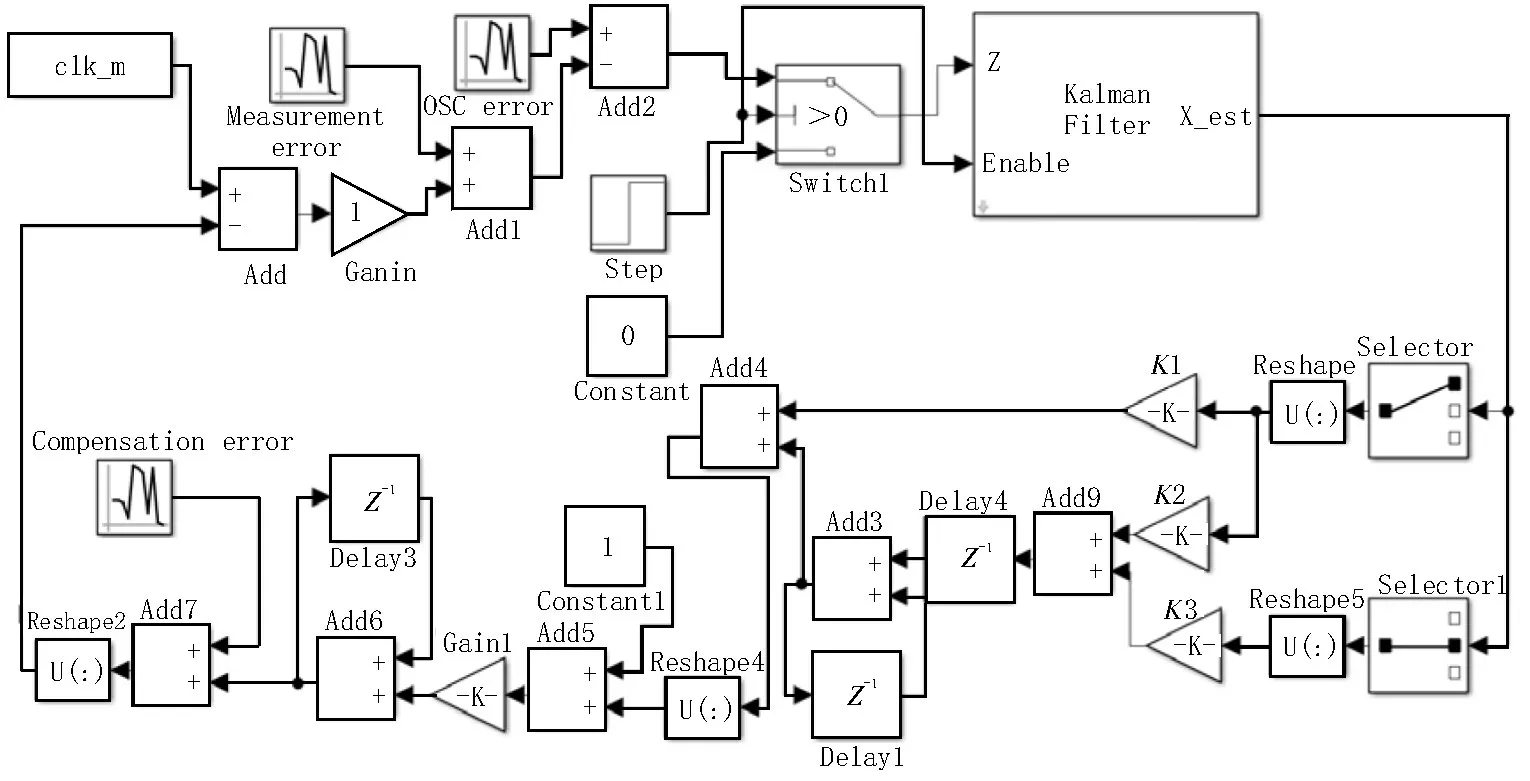

利用Matlab simulink 工具包构建时钟同步方法的数字仿真模型(图5)对主从节点时钟同步性能进行仿真验证。“clk_m”模块用于生成主时钟相位;从节点时钟相位是由初始参考频率与由环路滤波输出的偏置参考频率之和的累积产生;模型中开关“Switch”用于控制仿真状态,可以观察主从时钟同步环路由开环状态(主从时钟不同步)到闭环状态(主从时钟同步)的变化过程。开环状态下,环路滤波器的输入被强制为零。

图5 时钟同步数字实现模型

仿真设置中,假设从节点的初始偏置参考频率为1 Hz,在8.6 s 后进入闭环状态。为了观察时差的变化,主节点的偏置参考频率在前7.6 s 为0.5 Hz(钟漂为0.01 Hz/s),然后将其改为3 Hz。

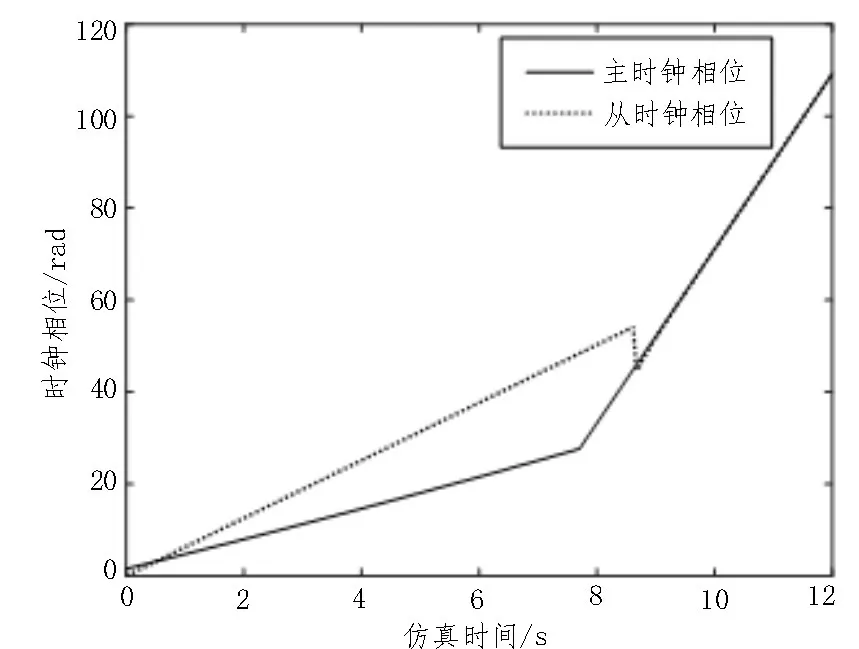

图6 给出了主节点和从节点的时钟同步仿真结果。在整个仿真过程中,主时钟独立运行,而从节点时钟阶段仅在开环状态下自由运行。由图可知,在闭环状态下,从节点的时钟相位会尝试跟踪主节点的时钟相位。两条曲线重合意味着实现了时间同步。

图6 主从时钟相位比较

主从节点间进行无线通信测量,节点间时差测量噪声影响时钟同步精度。图7 给出了不同载噪比(Carrier Noise Ratio,CNR)条件下的时钟同步精度,其时钟同步精度统计结果如表1 所示。由表1 可知,随着载噪比降低,主从节点间时钟同步精度衰减;载噪比在65~95 dBHz 范围内变化时,主从节点间时钟同步精度(标准差)在ns 级。

表1 时钟同步精度

4 结论

该文提出了一种面向5G 智能电网的主从节点时钟在线实时同步方法:首先,分析时钟特性,建立时钟模型;然后,采用卡尔曼滤波对时钟状态(相位误差、频率误差和钟漂)进行估计,降低噪声对时钟同步精度的影响;接着,采用一阶FLL 辅助的二阶PLL 环路滤波器,保证环路有足够大的频率牵引能力和足够高的时钟输出精度;最后,环路滤波器输出控制量驱动调节从节点时钟,与主时钟保持同步。系统性地构建了时钟同步方法的数字实现模型,仿真结果表明,主从节点通信载噪比在65~95 dBHz 范围内变化时,主从节点可实现ns级时钟同步精度,满足5G 智能电网的高精度时钟同步需求。