绝缘栅双极型晶体管驱动单元建模与仿真分析

李敏 刘志强 潘彦全

(中国第一汽车股份有限公司研发总院,长春 130013)

1 前言

功率单元将电池的直流电转换为驱动电机运转所需的交流电,是电动汽车功率调节的核心部件,其工作由驱动单元控制,驱动单元功能的准确性将直接影响整车性能和行驶安全性。

驱动芯片是驱动单元电路的核心器件,为在驱动单元设计初期进行仿真,需要针对驱动芯片进行芯片逻辑与时序及功能的建模。目前,国内外整车制造商在驱动单元建模时,普遍采用驱动芯片制造商提供的芯片简化模型,简化模型通常存在功能不完整或无法反映芯片瞬态特性的问题。芯片制造商为保护知识产权也可能不提供芯片模型,如电动汽车电驱动系统用驱动芯片[1]。

本文以英飞凌1ED020I12FA2[2]芯片为例,从驱动芯片及其外围电路建模方面研究适用于驱动芯片的建模仿真方法,并进行测试验证。

2 驱动芯片建模

2.1 驱动芯片的主要功能

1ED020I12FA2 是一款增强型栅极驱动器,既可用于驱动绝缘栅双极型晶体管(Insulated Gate Bipolar Transistor,IGBT),也可用于驱动金属氧化物半导体场效应晶体管(Metal Oxide Semiconductor Field Effect Transistor,MOSFET)。1ED020I12FA2具备以下功能:双电源供电;2 A轨到轨输出;退饱和检测;有源米勒钳位;无磁芯变压器高低压隔离;电源状态监控,即欠压锁定(Under Voltage-Lockout,UVLO)。

1ED020I12FA2驱动芯片设计原理如图1所示。

图1 1ED020I12FA2驱动芯片设计原理

2.2 驱动芯片的逻辑与时序

1ED020I12FA2 芯片主要功能与其输入、输出时序关系[1]如图2所示。

图2 1ED020I12FA2工作时序

图2 a 中,当输入脉冲宽度调制(Pulse Width Modulation,PWM)信号只有正输入IN+时,负输入IN-为低电平,芯片的输出信号与输入信号IN+保持一致,当复位(/RST)引脚输入低电平时,芯片输出低电平。当输入PWM 信号为IN+和IN-时,芯片输出逻辑主要由IN+信号决定,但当IN-出现高电平时,芯片将强制输出低电平。

图2b 中,TPDON为开通延迟时间,TPDOFF为关断延迟时间,TDESATfilter为退饱和保护时间常数,TDESATOUT为退饱和保护时间,TDESATleb为最初的消隐时间,TDESATFLT为退饱和保护触发时间,TRSTmin为最小复位时间,blanking time 为消隐时间。由图2b 可知,在不考虑输入、输出信号间延迟的情况下:当芯片的退饱和保护(Desaturation,DESAT)引脚电压VDESAT达到9 V时,将触发驱动芯片的退饱和保护功能,芯片的输出管脚OUT 被强制拉低,同时,芯片的故障(/FLT)引脚输出低电平,上报IGBT 故障;当/RST 引脚输入低电平时,/FLT 清除,芯片输出恢复图2a 所示的时序逻辑。

图2c 中,当芯片原边电源(VCC1)电压幅值低于欠压锁定阈值1(VUVLOL1)时,芯片输出锁止,OUT引脚输出低电平,同时预警(RDY)引脚输出低电平,上报RDY故障;当电源VCC1电压幅值高于欠压锁定恢复阈值1(VUVLOH1)时,RDY 故障清除,OUT 引脚输出恢复图2a 所示的时序逻辑。当芯片副边电源(VCC2)电压幅值低于欠压锁定阈值2(VUVLOL2)时,芯片输出锁止,OUT 引脚输出低电平,同时RDY 引脚输出低电平,上报RDY故障;当电源VCC2电压幅值高于欠压锁定恢复阈值2(VUVLOH2)时,RDY 故障清除,OUT 引脚输出恢复图2a时序逻辑。除以上翻转状态外,电源电压的幅值还影响芯片输入、输出脉冲信号的幅值。

综合上述分析可以看出,/RST 在处理信号逻辑时具有最高优先级,一旦触发/RST,芯片输出将一直处于锁止状态,即输出低电平,直至/RST 信号清除。根据以上分析,为简化描述,进行以下定义:

a. 将DESAT 引脚电压幅值低于9 V 定义为1,DESAT引脚电压幅值高于9 V定义为0;

b.将电源VCC1 电压幅值高于VUVLOH1定义为1,电源VCC1电压幅值低于VUVLOL1定义为0;

c. 将电源VCC2 电压幅值高于VUVLOH2定义为1,电源VCC2电压幅值低于VUVLOL2定义为0。

由此可得1ED020I12FA2 芯片的基本功能逻辑真值表和保护功能逻辑真值表,如表1和表2所示。

表1 1ED020I12FA2芯片基本功能逻辑真值表

表2 1ED020I12FA2芯片保护功能逻辑真值表

为使芯片工作逻辑更为简化,在一般应用中采用将IN-信号直接接入低电平的电路连接方式,由电源VCC1电压幅值决定芯片输入IN+的电平。

2.3 驱动芯片建模与仿真

基于以上针对1ED020I12FA2 芯片的功能分析,利用Saber 软件的StateAMS 工具,搭建1ED020I12FA2 芯片的行为级仿真模型[3-4],如图3 所示。在不清楚芯片内部电路结构的情况下,根据芯片的输入、输出关系,对芯片的动作进行行为级[2,5-6]描述,使其能够用于驱动单元的建模仿真,为驱动单元的各项功能仿真验证提供基础。

图3 1ED020I12FA2芯片行为级模型

根据数据手册中提供的典型应用电路,搭建芯片的应用电路模型并仿真,输出波形如图4 所示。由图4 可以看出,前15 μs 模拟1ED020I12FA2 芯片原边5 V电源欠压,前35 μs模拟1ED020I12FA2芯片副边15 V 电源欠压,在第54.5 μs 时触发1ED020I12 FA2 芯片退饱和保护功能,第100~105 μs 芯片复位后,1ED020I12FA2芯片输出恢复正常,直到第122 μs时1ED020I12FA2芯片原边5 V 电源再次欠压,芯片输出保持低电平。模型输出波形与数据手册中描述的时序逻辑相符。

图4 1ED020I12FA2芯片仿真波形

3 驱动单元建模

3.1 驱动单元的主要功能

驱动单元控制IGBT按照要求进行动作的同时,需对IGBT 进行必要的保护,其主要功能包括[7]:

a. 电源变换功能。提供驱动IGBT 开关动作所需的电压及功率,同时具有信号处理所需的模拟电源与数字电源。主电源变换电路将12 V 电源变换为6 路+15 V/-8 V 电源用作驱动芯片的副边电源。

b.隔离及功率放大功能。通过1ED020I12FA2芯片对驱动信号的高低压实现隔离及功率放大。

c. 模拟量采样及信号处理功能。采集功率模块温度、直流母线电压等模拟量信号并处理。

d. IGBT 模块保护功能。为IGBT 模块提供过压、过流、短路及过热等保护功能。 利用1ED020I12FA2 芯片的DESAT 功能匹配适当的外围电路实现IGBT模块的短路保护,短路保护响应时间不超过5 μs。

3.2 驱动单元建模与仿真

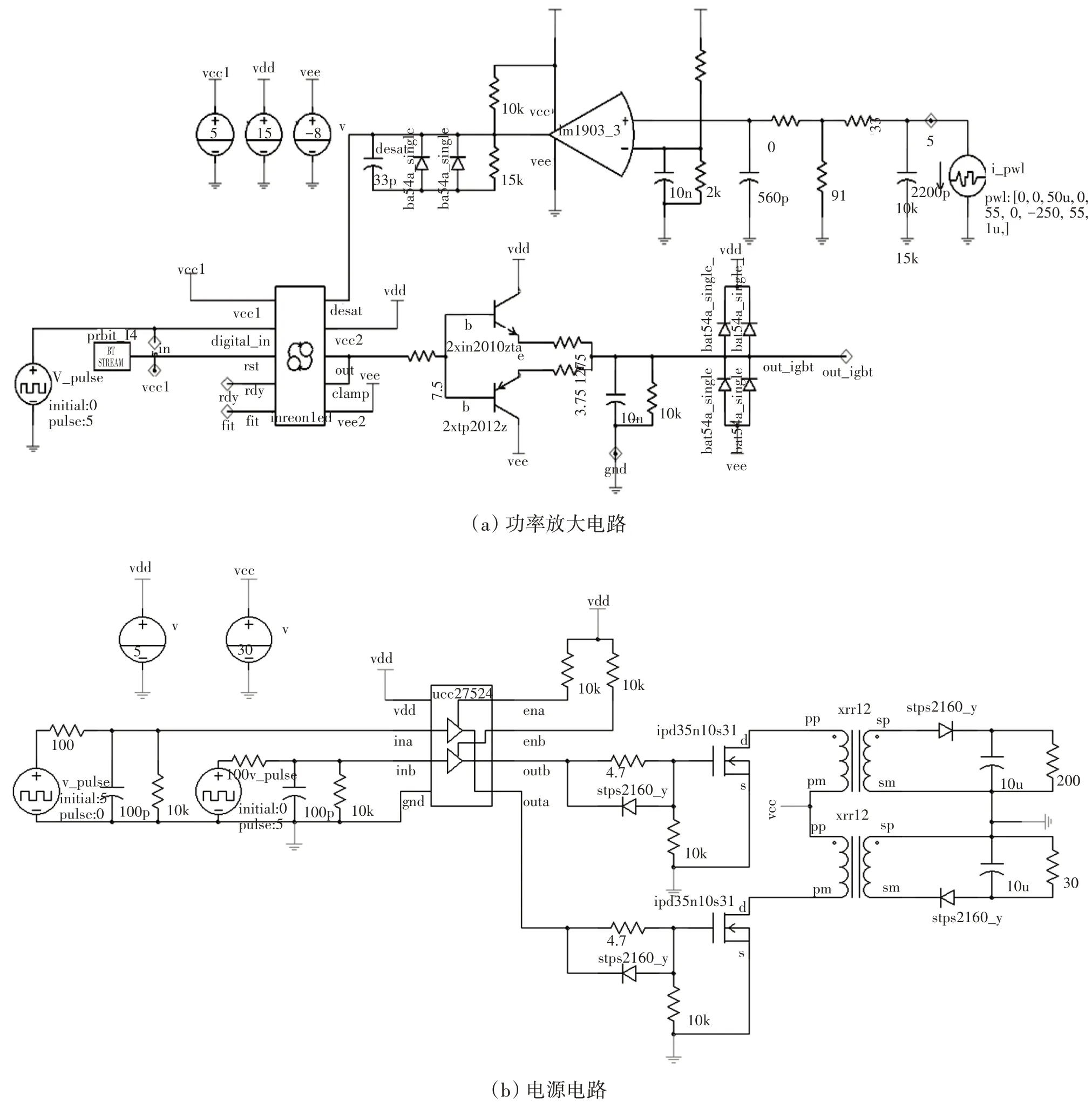

通过以上对驱动单元功能的分析,本文基于Saber 软件对驱动单元的电源变换功能[8]、隔离与功率放大功能[6]和IGBT 模块保护功能[9]进行电路原理建模,如图5 所示。驱动单元中的核心驱动芯片采用1ED020I12FA2芯片模型。

图5 驱动单元电路原理模型

在驱动单元的仿真中,将仿真时间延长至6 ms,仿真结果如图6所示。其中前1 ms模拟了芯片副边15 V 电源的建立过程,由于此时电源电压幅值没有达到VUVLOH2的限值,芯片输出RDY信号,即使芯片原边IN+引脚有脉冲输入,其输出仍为低电平;第1 ms后芯片副边电源幅值达到15 V,芯片输出逻辑电平与IN+输入一致;第3 ms时触发退饱和保护功能,此时距短路故障发生的时间为4 μs,芯片报/FLT 的同时,输出关闭,即持续输出低电平;直到第5 ms时发出复位信号,/FLT清除,芯片输出逻辑电平与IN+输入一致。该仿真结果与驱动单元电路的设计意图相符。

图6 驱动单元仿真波形

3.3 测试验证

为验证模型的正确性与有效性,对1ED020I12FA2型驱动芯片的驱动单元进行了功能测试[10],测试结果如图7 所示,其中,Vge为IGBT 栅极驱动信号,Ic为IGBT 集电极电流信号,Vce为IGBT 集电极与发射极间电压信号。受限于测试环境,仅对部分重要功能逻辑进行测试,测试结果符合设计预期。由图7a可知,当输入信号只有正输入IN+时,IN-为低电平,芯片的输出信号与输入信号IN+保持一致;由图7b 可知,实际电路中短路故障发生后6 μs 触发退饱和保护功能,不论芯片输入IN+为何状态,芯片输出驱动信号均为低电平。

图7 基于1ED020I12FA2驱动单元双脉冲测试波形

4 结束语

本文基于Saber StateAMS 工具建立了1ED020I12FA2 型驱动芯片行为级模型,仿真结果表明,该模型能够准确反映芯片的工作时序与逻辑,将芯片模型应用于驱动单元的电路原理仿真,仿真结果与驱动单元电路的设计意图相符,验证了驱动单元电路设计的正确性。