球栅阵列芯片锡球的三维检测方法研究*

梁天为, 朱呈祥, 陈 浩, 杨 光

(1.江苏师范大学 电气工程及自动化学院,江苏 徐州 221116;2.聚时科技(上海)有限公司,上海 201100)

0 引 言

随着芯片产业链在国内外的不断开拓,芯片封装检测技术得到了快速发展,芯片制造的诸多工艺已经在向亚微米级方向发展。球栅阵列(ball grid array,BGA)封装芯片是诸多集成芯片的一种[1],植球工艺的封装质量直接影响芯片的性能与可靠性。鉴于锡球直径小、检测指标精度高的特点,使得普通的接触式测量技术无法满足要求。目前应用于BGA芯片的检测技术主要有[2~9]:基于X射线的锡球检测、基于平面图像处理技术的锡球检测、基于机器学习的锡球表面缺陷检测等。基于X射线的检测技术,虽是无损检测,但检测效率不高且依赖于检测人员的主观判定;基于平面图像处理的检测技术,主要是针对锡球的表面缺陷,如锡球半径、间距、偏移等,无法测量到锡球的三维指标,且锡球表面光滑易反光,所以拍摄时对打光系统的要求严格;基于机器学习的检测技术,同上,也是主要针对锡球的表面缺陷,如空焊、过焊、缺焊以及锡球粘连等。此外,也有采用CCD方法对BGA锡球的三维尺寸进行测量[10],但该方法建模复杂,对硬件设施的要求也高。经相关文献检索以及工程实践经验表明,目前国内尚未有一种成熟的芯片外观检测系统,尤其是BGA芯片锡球的检测。

现有检测方法中,尚未有从芯片点云入手进行缺陷检测的公开文献报道。基于点云的高精度特点,本文提出一种新的BGA芯片锡球三维检测方法。其原理是将获取的BGA芯片点云转成深度图像,并引入连通域分析方法进行处理,可快速地得到芯片锡球高度及其共面度。算法鲁棒性好,速度和精度均可以达到实时检测要求,有效避免了从点云做直接处理的低效率。

1 检测指标与方法

1.1 检测指标

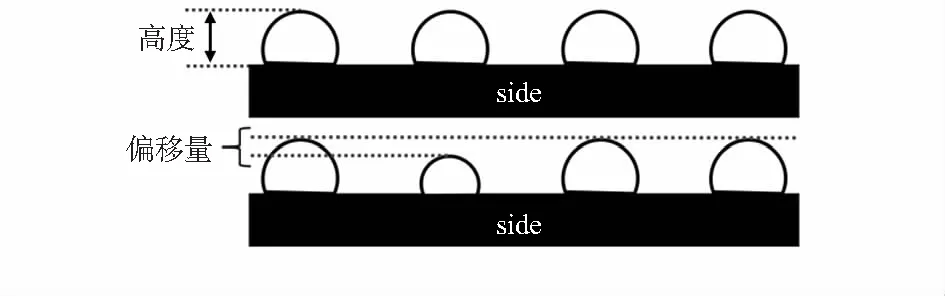

据行业内要求,BGA芯片的三维检测指标主要包括锡球高度、锡球共面度、芯片底座高度等。本文主要讨论锡球高度和共面度的检测,如图1所示。图中,高度为锡球顶部到芯片底座的距离,共面度以锡球高度偏移量作为衡量指标。

图1 检测指标

1.2 检测方法

1.2.1 深度图像转换原理

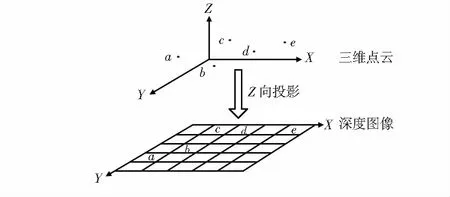

深度图像(depth image)是包含视点到物体对象表面距离相关信息的平面图像[11],其每个像素值代表视点到物体表面的实际距离。本文针对获取的芯片表面点云,利用沿Z方向投影在Z坐标值最小的点所在的XY平面并归一化的方法,将其转为深度图像,点云中的各三维点一一对应深度图像中的各像素,如图2所示,图2中5个三维点与视点所在面的距离实际用对应二维像素灰度值表示。

图2 深度图像转换原理

1.2.2 检测算法

根据具体检测环境的情况,调节双目线扫相机的光强、曝光时间等参数,获取到完整的三维点云数据。在获取BGA芯片点云数据后,根据点云的各点间距,预先设置好投影图像的大小和像素间距,利用上述图像转换原理将芯片点云转为深度图像。设定深度图的位深度为16位,各像素的灰度值代表点云各点到视点所在水平面的距离大小。针对深度图像,预设投影的相对高度,即设定点云中Z值最小点到视点所在水平面的距离

hd=2(zmax-zmin)

(1)

式中zmax,zmin分别为点云中Z坐标值的最小与最大值,zmax-zmin即为芯片的整体高度,视点所在位置设置为芯片整体高度的2倍距离所在的水平面。利用随机抽样一致性(RANSAC)算法拟合出芯片点云的基座平面并得到方程参数[12]。针对深度图像,利用连通域分析方法[13],提取各锡球区域的像素点并聚类,以此求取各区域的二维中心坐标。然后,选取中心点的8邻域并提取该9点对应的三维坐标点共同求平均,赋值给锡球顶部三维点,以减小中心点选取不精确带来的误差,提高算法的鲁棒性。

上述连通域分析算法主要包括:

1)阈值分割:二值化的主要方法有基于边缘灰度、基于直方图聚类以及定值选取的方法等。本文针对深度图像,通过设定锡球区域相对于基座表面的高度定值(Z方向)作为阈值T来进行二值化操作

(2)

输入16位深度图像g(x,y)可得到8位的二值图像gb(x,y)

(3)

上述操作可将图像分为目标前景与背景,黑色为背景,白色前景即为各锡球区域。

2)形态学处理:由于通过设定的高度阈值进行二值化操作后,目标不免会被分割成不连续的区域,因此,为减少计算错误,填充各区域空洞并去除各区域间的噪声点,使各锡球区域逼近圆形化,形态学处理十分重要。形态学处理是利用结构元素对图像目标区域进行分析的方法[14]。根据需求,首先设定结构元素M1的形状为椭圆,确定元素大小,对二值图像G进行闭运算操作获得图像G1,目的是填充目标区域内的细小空洞、平滑其边界。定义如下

G1=GM1=(G⊕M1)⊗M1

(4)

其次,设定结构元素M2的形状为椭圆,确定元素大小,对图像G1进行开运算操作,目的是消除孤立点、平滑其边界,以此保证各锡球区域的完整性。定义如下

(5)

3)连通域分析:对于二值图,连通域分析实际是采用4或8邻域的方法对像素值相同或相似的像素进行标记并聚类,可得到各类中所有的像素坐标值以及像素总数。

根据各锡球区域中心横纵坐标的最大与最小值,将各锡球依次排序。得到锡球顶部三维坐标点后,利用点到平面的距离,可计算得到锡球的高度;求取各锡球高度的平均值,利用作差法可得各锡球的位置偏差,求得共面度。设各锡球顶部坐标点为p(xi,yi,zi),i∈{1,2,…,m},则各锡球的高度及共面度如下

(6)

(7)

式中hi为各锡球高度;Ci为各锡球的偏移量,代表共面度;m为锡球总数;基座平面方程为Ax+By+Cz+D=0。

2 实验结果与误差分析

2.1 实验结果

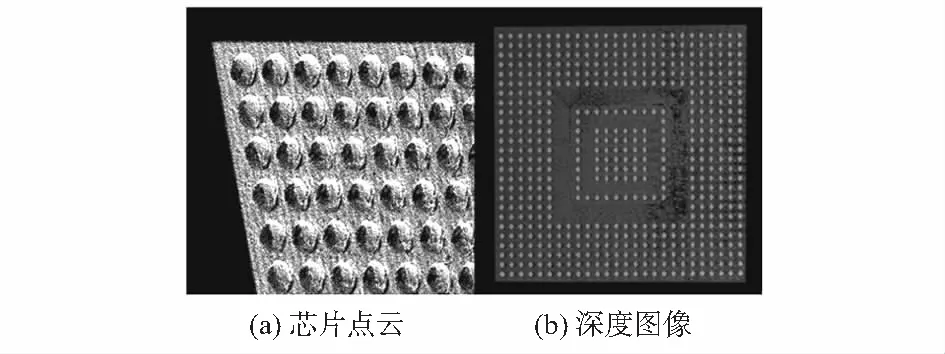

本文研究中,通过Chromasens—3DPIXA双目三维线扫相机获取BGA芯片的点云数据,点云数量为2 273 758个。算法利用Visual Studio 2017+OpenCV库等开发,使用OpenMP和多线程等技术提升速度,可同时处理多个BGA芯片点云;计算机配置为Intel®CoreTMi7—8700,GeForce GTX 1660,16.0 GB运行内存。图3为获取的BGA芯片部分三维点云示意及转换后的深度图,图像大小预设为2 560×2 560,像素间距等于点云的各点间距。

图3 芯片点云与深度图像

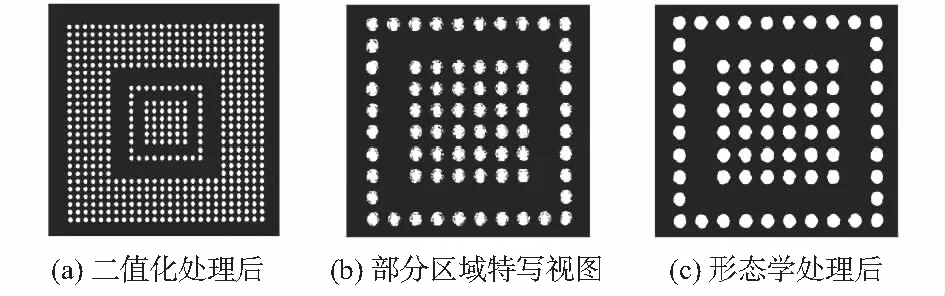

拟合基座表面获取平面方程参数后,通过设定的阈值进行二值化处理,得到图4(a)所示的结果。其中,图4(b)为图4(a)的特写视图,可明显看出,各锡球的目标区域存在不连贯性。利用本文所述的形态学处理方法,通过对比大小不同的结构元素所得出的效果,最终设置闭运算的椭圆形结构元素M1大小为15×15,开运算的椭圆形结构元素M2大小为5×5,对二值图进行处理,结果如图4(c)所示。可明显看出各锡球区域较为完整,更加逼近圆形化,且区间不存在孤立的噪声点。

图4 连通域分析结果

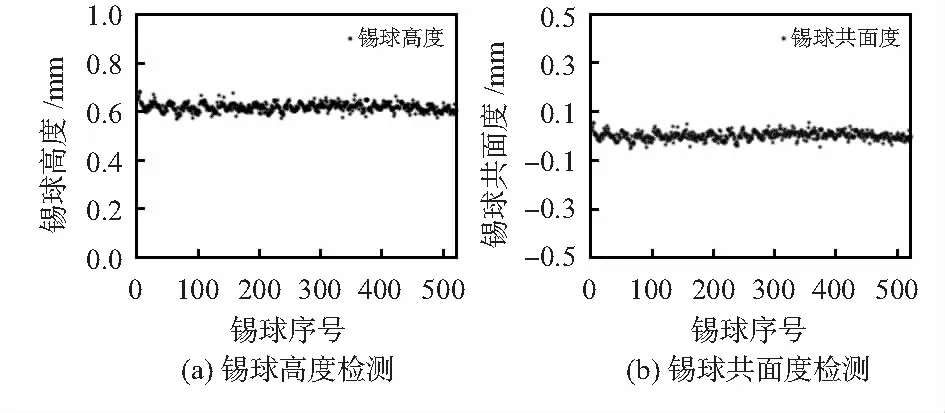

通过连通域分析后,利用上述公式可求取各锡球的高度及共面度,将计算结果绘制成如图5所示,图中横坐标为芯片中的552个锡球,纵坐标为计算结果。从运行时间上来看,本文检测算法共计耗时498.34 ms。为突出算法的优越性,本文直接对芯片点云进行处理,基于PCL算法库去除基座点云并利用聚类分割算法将各锡球单独分割计算,算法耗时7.392 s。由此可见本文算法的耗时远远小于对点云做直接处理的耗时,表明本文提出的三维检测方法,可有效地用于BGA芯片锡球的实时三维检测。

图5 检测结果的数据分布

2.2 误差分析

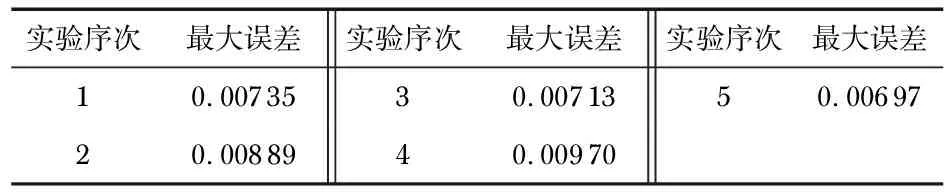

对同一芯片依次采集5次点云数据,对其进行重复性实验,并利用更加精密的设备(±2 μm)获取该芯片各锡球的高度数据作为标准参数。将每次实验测量的锡球高度数据与该芯片锡球标准参数的绝对差值的最大值,作为每次实验的最大误差,从而判定测量的重复性精度,误差如下

(8)

式中E为每次实验的最大误差;h′i,hi分别为各锡球的测量数据与标准数据;n为芯片的锡球总数。表1给出了每次实验的最大误差计算数据。可见,实验的最大误差不超过0.01 mm。这一结果表明,本文方法检测精度明显优于行业内通用的检测标准(误差为0.015 mm[15])。

表1 实验的最大误差 mm

3 结束语

本文提出了一种新的BGA芯片锡球三维检测方法。首先将采集到的BGA芯片点云转换成深度图像,然后经过点云与图像信息的预处理,利用连通域分析方法并行计算各锡球的高度及共面度。在特定的光强下多次重复性实验的最大误差皆不超过0.01 mm,相比于直接做点云处理的方法,本文所提出的方法速度快、精度高,获得了满意的效果。为芯片的在线检测提供了理论与方法依据,同时也可为其他类型芯片的检测提供一些借鉴。